# Growth and Characterization of High Permittivity Thin Film Nanolaminates Fabricated by Atomic Layer Epitaxy

#### Hui Zhang

B.E. of Material Science and Engineering,

Central South University of Technology, Changsha, Hunan, China, 1994

M.S. of Material Science and Engineering,

Oregon Graduate Institute of Science and Technology, 1997

M.S. of Electrical Engineering,

Oregon Graduate Institute of Science and Technology, 1998

A dissertation presented to the faculty of the

Oregon Graduate Institute of Science and Technology

in partial fulfillment of the

requirements for the degree

Doctor of Philosophy

in

Electrical and Engineering

May, 2000

The dissertation "Growth and Characterization of High Permittivity Thin Film Nanolaminates Fabricated by Atomic Layer Epitaxy" by Hui Zhang has been examined and approved by the following Examination Committee:

Dr. Rajendra Solanki, Thesis Advisor Professor, Oregon Graduate Institute

Dr. Jack McCarthy

Assistant Professor, Oregon Graduate Institute

Dr. Anthony Bell Associate Professor, Oregon Graduate Institute

Dr. J. Neal Cox, Intel Corporation

To

my parents & my husband

#### Acknowledgements

I would like to express my deepest appreciation to my advisor, Dr. Raj Solanki for his guidance, encouragement and financial support during the course of this project.

I am indebted to the thesis committee members: Dr. Jack McCarthy, Dr. Anthony Bell and Dr. J. Neal Cox for reviewing this dissertation and offering helpful suggestions.

Special thanks go to Dr. Indrajit Banerjee, Dr. Christopher Barbero, Dr. Brian Roberds, Dr. Edward Ritz, Justin Shaw, Zeting Pei, Doug Skinner and Lisa Volpol for their constant support and invaluable assistance.

Finally, I would like to thank my husband Michael and our parents for their support and consistent encouragement.

## **Table of Contents**

| ACKNOWLEGEMENTS                                                                                                      | iv  |

|----------------------------------------------------------------------------------------------------------------------|-----|

| TABLE OF CONTENTS                                                                                                    | v   |

| LISTS OF TABLES                                                                                                      | vii |

| LISTS OF FIGURES                                                                                                     | ix  |

| ABSTRACTS                                                                                                            | xiv |

|                                                                                                                      |     |

| Chapter 1 Introduction                                                                                               | 1   |

| Reference                                                                                                            | 5   |

| Chapter 2 MOS System and high permittivity materials                                                                 | 8   |

| 2.1 MOS System                                                                                                       | 8   |

| 2.2 Charges in MOS system                                                                                            | 20  |

| 2.3 Carrier transport in dielectric films                                                                            | 23  |

| 2.4 MOSFET transistor                                                                                                | 29  |

| 2.5 Scaling issues and limitations                                                                                   | 34  |

| 2.6 High dielectric constant materials                                                                               | 37  |

| Reference                                                                                                            | 43  |

| Chapter 3 Atomic layer epitaxy                                                                                       | 46  |

| 3.1 Background of ALE                                                                                                | 41  |

| 3.2 The mechanism of ALE process                                                                                     | 41  |

| Reference                                                                                                            | 47  |

| Chapter 4 ALE growth of Ta <sub>2</sub> O <sub>5</sub> , HfO <sub>2</sub> , ZrO <sub>2</sub> and their nanolaminates | 53  |

| 4.1 Introduction of the F-120 ALE reactor                                                                            | 53  |

| 4.2 Growth and initial characterization of Ta <sub>2</sub> O <sub>5</sub>      | 57  |

|--------------------------------------------------------------------------------|-----|

| 4.3 Growth and initial characterization of HfO <sub>2</sub>                    | 63  |

| 4.4 Growth and initial characterization of ZrO <sub>2</sub>                    | 65  |

| 4.5 Growth and initial characterization of nanolaminates                       | 69  |

| 4.5.1 Growth of Ta <sub>2</sub> O <sub>5</sub> -HfO <sub>2</sub> nanolaminates | 69  |

| 4.5.2 Growth of Ta <sub>2</sub> O <sub>5</sub> -ZrO <sub>2</sub> nanolaminates | 71  |

| 4.5.3 Growth of ZrO <sub>2</sub> -HfO <sub>2</sub> nanolaminates               | 71  |

| Reference                                                                      | 73  |

| Chapter 5 Characterization of MOS structure with high k insulators             | 75  |

| 5.1 Nitrided silicon substrate                                                 | 75  |

| 5.2 Material and electrical characterization of binary oxides                  | 79  |

| 5.2.1 Ta <sub>2</sub> O <sub>5</sub> thin films                                | 79  |

| 5.2.2 HfO <sub>2</sub> and ZrO <sub>2</sub> thin films                         | 93  |

| 5.3 Material and electrical characterization of nanolaminates                  | 95  |

| 5.3.1 Ta <sub>2</sub> O <sub>5</sub> -HfO <sub>2</sub> nanolaminates           | 95  |

| 5.3.2 Ta <sub>2</sub> O <sub>5</sub> -ZrO <sub>2</sub> nanolaminates           | 109 |

| 5.3.3 ZrO <sub>2</sub> -HfO <sub>2</sub> nanolaminates                         | 113 |

| 5.4 Electrical properties of SiO <sub>2</sub> and high k films                 | 115 |

| Reference                                                                      | 120 |

| Chapter 6 Summary and Conclusions                                              | 122 |

| <b>T</b> 7'4-                                                                  | 107 |

## **List of Tables**

| Table 1-1 | The International Technology Roadmap                                                                  | 2  |

|-----------|-------------------------------------------------------------------------------------------------------|----|

| Table 2-1 | Conduction processes in dielectric films                                                              | 24 |

| Table 2-2 | Scaling factors associated with important device parameters for                                       |    |

|           | the initial constant-field scaling law, generalized one and the                                       |    |

|           | practical constant-voltage scaling law                                                                | 36 |

| Table 2-3 | The energy band gap and dielectric constant of various                                                |    |

|           | dielectric materials                                                                                  | 41 |

| Table 5-1 | Electrical properties of Ta <sub>2</sub> O <sub>5</sub> thin film grown on p-type Si                  |    |

|           | substrate, where a thin layer of SiO <sub>2</sub> exists at the interface due                         |    |

|           | to the Si oxidation                                                                                   | 83 |

| Table 5-2 | Ta <sub>2</sub> O <sub>5</sub> films grown on Al passivated Si. The thickness of                      |    |

|           | Al layer is 2 nm                                                                                      | 85 |

| Table 5-3 | Electrical properties of Ta <sub>2</sub> O <sub>5</sub> / Si <sub>3</sub> N <sub>4</sub> after RTA in |    |

|           | argon and oxygen ambients                                                                             | 86 |

| Table 5-4 | Electrical properties of HfO <sub>2</sub> / Si <sub>3</sub> N <sub>4</sub> with the thickness of      |    |

|           | Si <sub>3</sub> N <sub>4</sub> about 2.76nm or 2.12nm                                                 | 93 |

| Table 5-5 | Electrical properties of ZrO <sub>2</sub> / Si <sub>3</sub> N <sub>4</sub> with the thickness of      |    |

|           | Si <sub>3</sub> N <sub>4</sub> about 2.76nm or 2.12nm                                                 | 94 |

| Table 5-6 | The Ta <sub>2</sub> O <sub>5</sub> - HfO <sub>2</sub> nanolaminates grown on Al coated Si             |    |

|           | substrates with and without rapid thermal annealing                                                   | 97 |

| Table 5-7 | The Ta <sub>2</sub> O <sub>5</sub> - HfO <sub>2</sub> nanolaminates growth on nitrided Si substrates. |    |

|           | The thickness of Si <sub>3</sub> N <sub>4</sub> is 2.76 nm                                            | 99 |

| Table 5-8  | Ta <sub>2</sub> O <sub>5</sub> -ZrO <sub>2</sub> nanolaminates deposited on Si substrates.       |     |

|------------|--------------------------------------------------------------------------------------------------|-----|

|            | The thickness ratio of Ta <sub>2</sub> O <sub>5</sub> : ZrO <sub>2</sub> is 12%: 88%             | 109 |

| Table 5-9  | Ta <sub>2</sub> O <sub>5</sub> - ZrO <sub>2</sub> nanolaminates grown on nitrided Si substrates. |     |

|            | The thickness of Si <sub>3</sub> N <sub>4</sub> is 2.76 nm                                       | 112 |

| Table 5-10 | ZrO <sub>2</sub> -HfO <sub>2</sub> nanolaminates growth on nitrided Si substrates.               |     |

|            | The thickness of Si <sub>3</sub> N <sub>4</sub> is 2.76 nm                                       | 114 |

## **List of Figures**

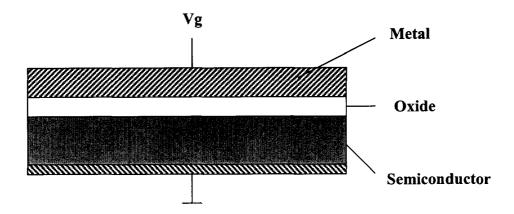

| Fig. 2.1  | MOS Structure                                                                | 9  |

|-----------|------------------------------------------------------------------------------|----|

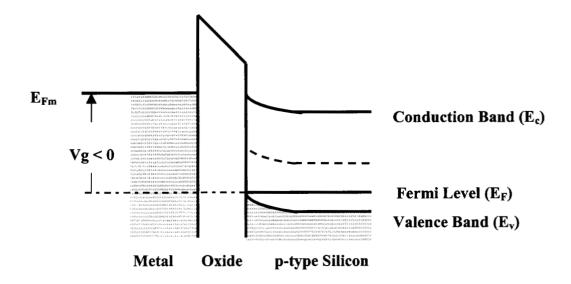

| Fig. 2.2a | Accumulation region of MOS capacitor                                         | 10 |

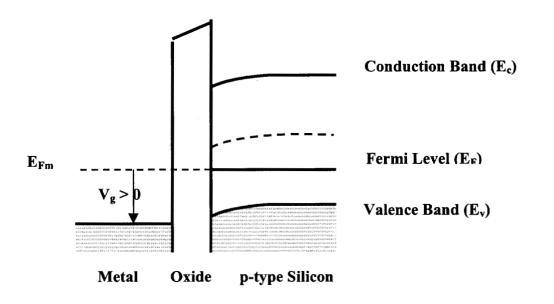

| Fig. 2.2b | Depletion region of MOS capacitor                                            | 10 |

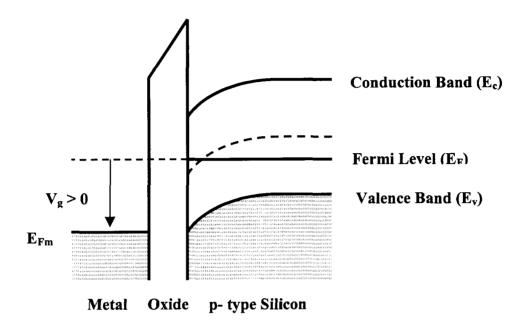

| Fig. 2.2c | Inversion region of MOS capacitor                                            | 11 |

| Fig. 2.3  | Energy band diagram at the surface of a p-type semiconductor.                |    |

|           | An arrow pointing down (up) denotes positive (negative) potential.           |    |

|           | Surface potential is measured with respect to the Fermi level E <sub>F</sub> |    |

|           | at the interface. Surface band bending $\psi_s$ is measured with respect     |    |

|           | to the intrinsic Fermi level E <sub>i</sub> at the interface                 | 13 |

| Fig. 2.4  | MOS capacitance-voltage characteristics under (a) low frequency              |    |

|           | (b) high-frequency (c) deep –depletion conditions                            | 16 |

| Fig. 2.5  | Low frequency equivalent circuit of the MOS capacitor                        | 18 |

| Fig. 2.6  | High frequency equivalent circuit of the MOS capacitor                       | 18 |

| Fig. 2.7  | MOS C-V curves measured at room temperature with frequency                   |    |

|           | as a parameter . The substrate is n-type                                     | 19 |

| Fig. 2.8  | MOS C-V characteristics as a function of the oxide thickness.                |    |

|           | Solid lines correspond to low frequency and dashed lines                     |    |

|           | represent high frequency. The substrate is p-type silicon                    | 20 |

| Fig. 2.9  | Four categories of oxide charges in the MOS system                           | 22 |

| Fig. 2.10 | Four basic transport processes in Schottky emission                          | 25 |

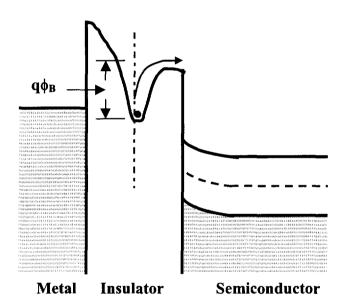

| Fig. 2.11 | Illustration of Frenkel-Poole emission. $\phi_B$ is the barrier height       | 26 |

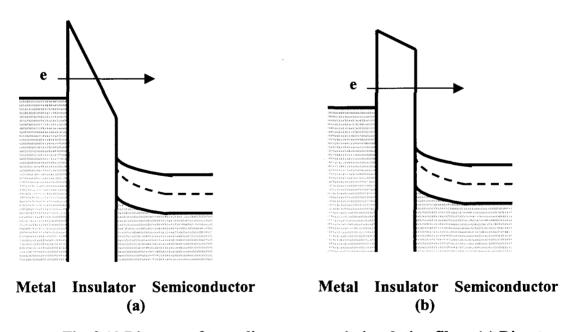

| Fig. 2.12 | Diagram of tunneling processes in insulating films. (a) Direct               |    |

|           | Tunneling (b) Fowler-Nordheim Tunneling                                      | 27 |

|           |                                                                              |    |

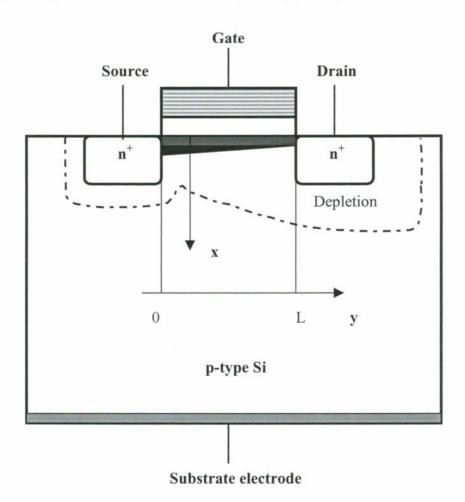

| Fig. 2.13 | Cross section of a MOSFET                                                              | 29         |

|-----------|----------------------------------------------------------------------------------------|------------|

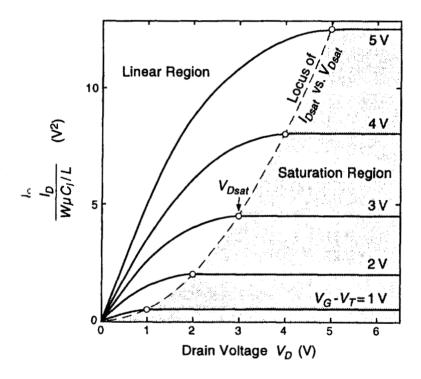

| Fig. 2.14 | Idealized saturation characteristics (ID vs. VD) of an n-channel                       |            |

|           | MOSFET .The dashed line indicates the locus of $I_{D\text{sat}}$ vs. $V_{D\text{sat}}$ | 33         |

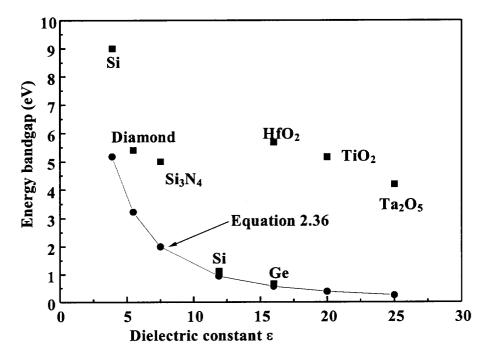

| Fig. 2.15 | Energy bandgap vs. the dielectric constant of various                                  |            |

|           | semiconductor and dielectric materials                                                 | <b>4</b> 1 |

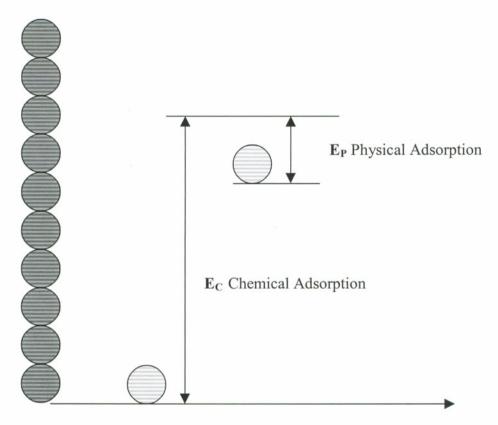

| Fig. 3.1  | Energy diagram of chemical and physical adsorption                                     | 48         |

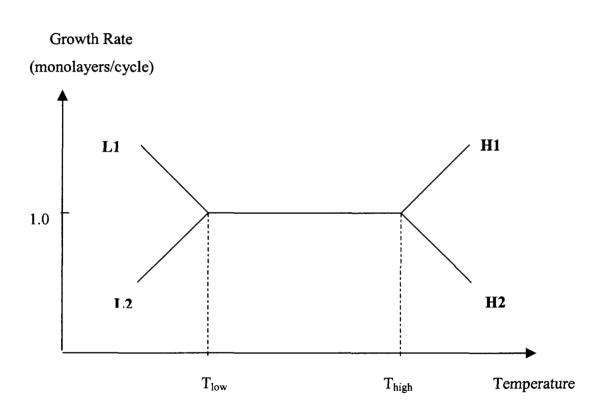

| Fig. 3.2  | An ALE processing temperature window                                                   | 49         |

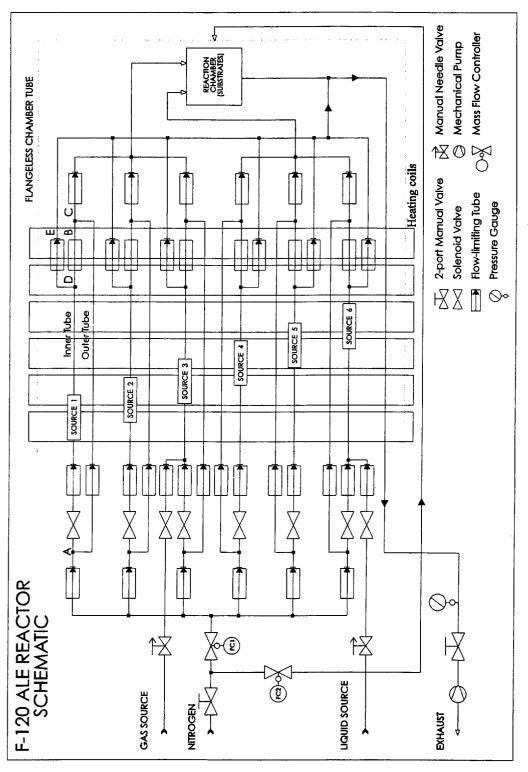

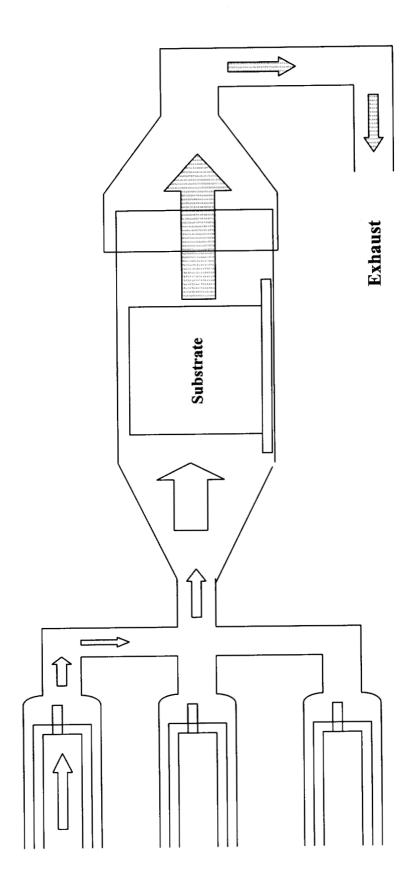

| Fig. 4.1  | ALE F-120 reactor system schematic                                                     | 5          |

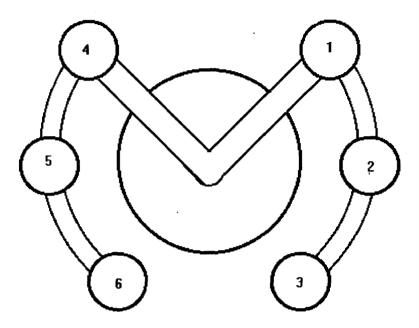

| Fig. 4.2  | Schematic diagram of the F-120 substrate holder (side view)                            | 56         |

| Fig. 4.3  | The rear view of F-120 substrate holder                                                | 57         |

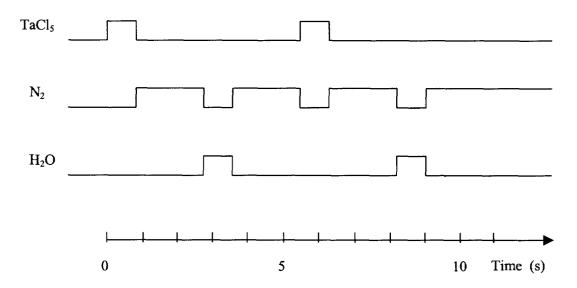

| Fig. 4.4  | Gas pulse sequence in Ta <sub>2</sub> O <sub>5</sub> growth by ALE process             | 58         |

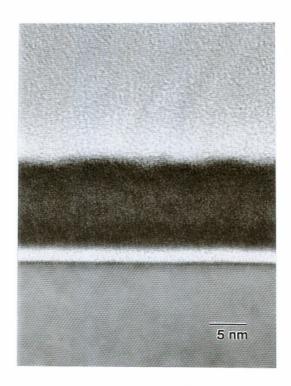

| Fig. 4.5  | High resolution TEM lattice image of Ta <sub>2</sub> O <sub>5</sub> film with an       |            |

|           | ellipsometrically measured thickness of 11.6 nm grown on silicon                       |            |

|           | substrate. A layer of 1.5 nm SiO <sub>2</sub> is formed at the interface               | 59         |

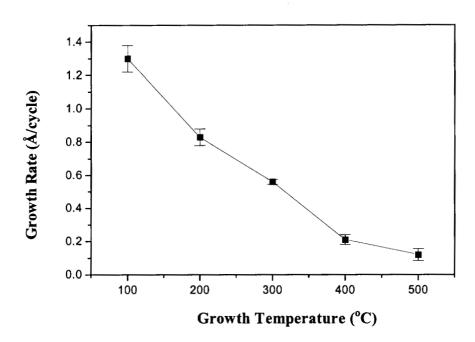

| Fig.4.6   | Growth rate vs. growth temperature of Ta <sub>2</sub> O <sub>5</sub> ALE thin films    |            |

|           | grown on Si substrate using TaCl <sub>5</sub> and H <sub>2</sub> O                     | 61         |

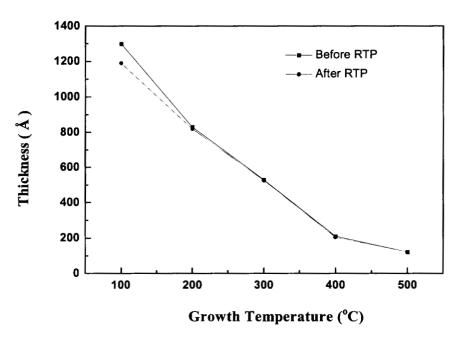

| Fig. 4.7  | The effect of RTP on Ta <sub>2</sub> O <sub>5</sub> film thickness at growth           |            |

|           | temperatures of 100, 200, 300, 400 and 500°C. The number                               |            |

|           | of water turn is 4 and water is kept at 20°C                                           | 61         |

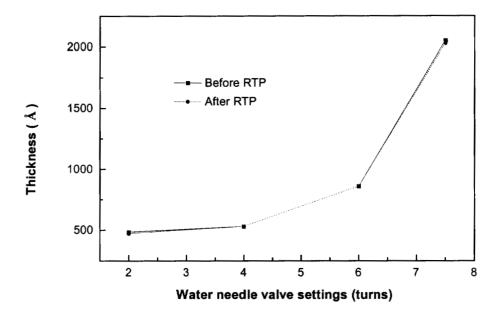

| Fig. 4.8  | The effect of water on Ta <sub>2</sub> O <sub>5</sub> film thickness at growth         |            |

|           | temperature of 300°C                                                                   | 6          |

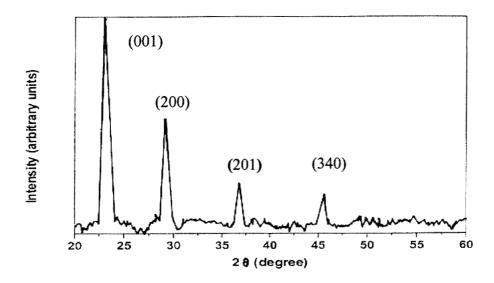

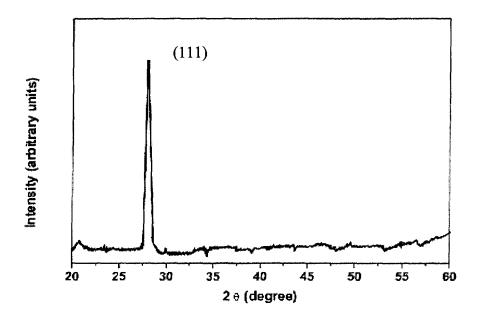

| Fig. 4.9  | X-ray diffraction pattern of rapid thermal annealed Ta <sub>2</sub> O <sub>5</sub>     |            |

|           | film at 800°C for 30 s in Ar                                                           | 62         |

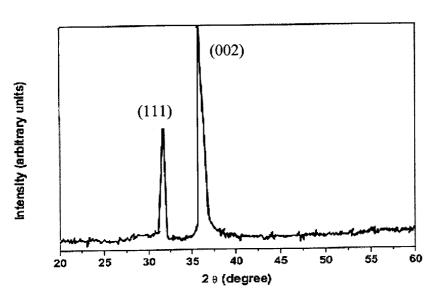

| Fig. 4.10 | X-ray diffraction pattern of HfO2 annealed in RTA chamber                              |            |

|           | at 800°C for 30 s in Ar                                                                | 64         |

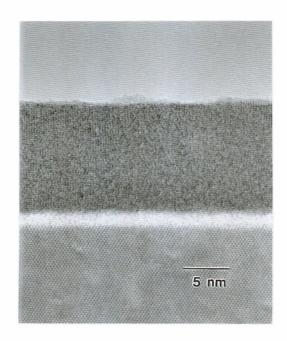

| Fig. 4.11 | High resolution TEM lattice image of HfO2 film with an                                 |            |

|           | ellipsometry thickness of 15 nm grown on Si. SiO <sub>2</sub> layer of                 |            |

|           | 2 nm is formed at the interface                                                        | 65         |

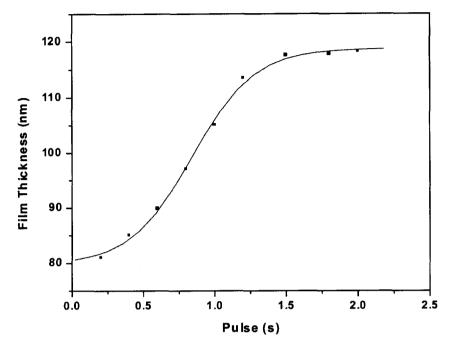

| Fig. 4.12 | The dependence of film thickness on the ZrCl <sub>4</sub> pulse duration               |            |

|           | for ZrO <sub>2</sub> film deposited at 300°C for 1000 reaction cycles. The                        |

|-----------|---------------------------------------------------------------------------------------------------|

|           | ZrCl <sub>4</sub> purge time used was 2.0 s except for 2.0 s pulse time                           |

|           | where 4.0 s purge duration was employed67                                                         |

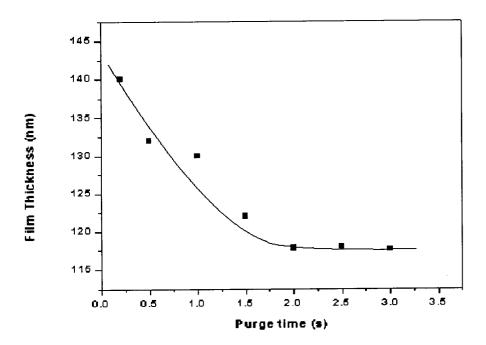

| Fig. 4.13 | The film thickness as a function of the water purge durations.                                    |

|           | The data were measured at the center of the film grown by 1000                                    |

|           | cycles at 300°C using 2.0 s ZrCl <sub>4</sub> pulses68                                            |

| Fig. 4.14 | X-ray diffraction pattern of ZrO <sub>2</sub> annealed at 700°C for 30 s in Ar68                  |

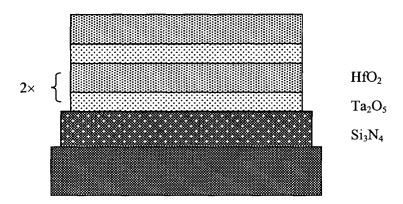

| Fig. 4.15 | Schematic cross-section view of a Ta <sub>2</sub> O <sub>5</sub> - HfO <sub>2</sub> nanolaminates |

|           | structure of $2 \times (Ta_2O_5 + HfO_2)$ . The thickness of each constituent                     |

|           | layer can be varied by number of reaction cycles. The silicon                                     |

|           | nitride layer is 2.76 nm thick70                                                                  |

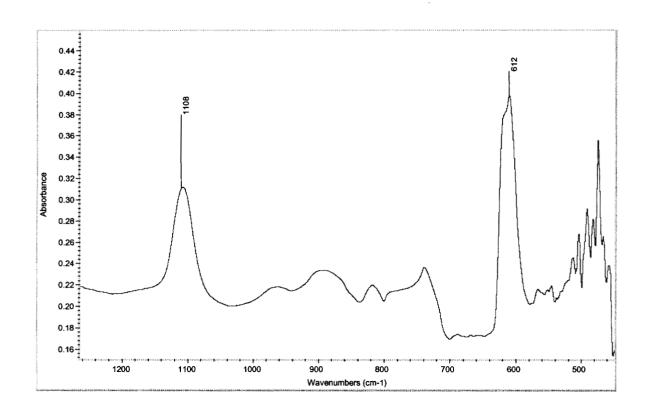

| Fig. 5.1  | FTIR spectrum of the nitrided Si substrate. The thickness of                                      |

|           | the nitride layer is 2.76nm77                                                                     |

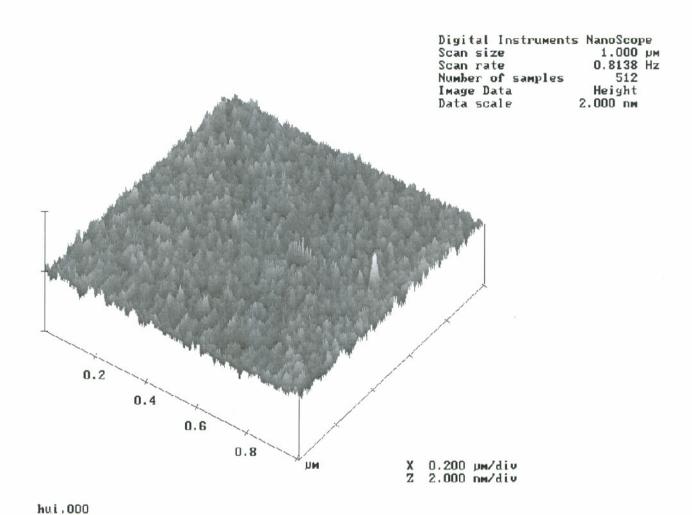

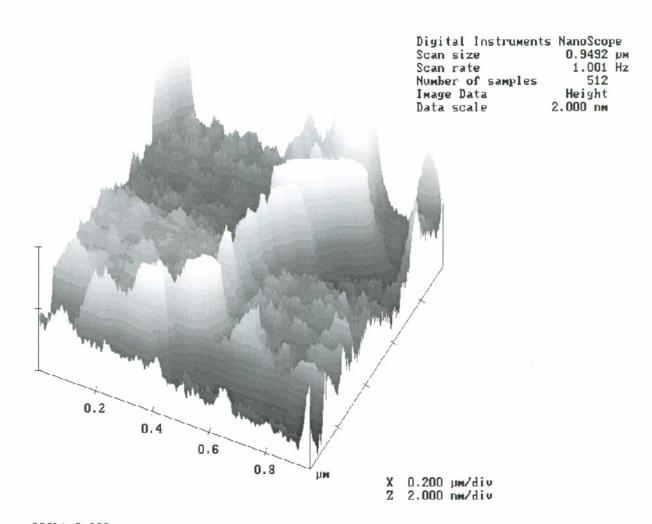

| Fig. 5.2  | AFM image of the silicon nitride layer of 2.76 nm, grown by                                       |

|           | rapid thermal annealing at 1000°C in ammonium for 30 s78                                          |

| Fig. 5.3a | AFM image of sample #322b1-2 on Si at 300°C for 1000 cycles80                                     |

| Fig. 5.3b | AFM image of sample #351b1-1 on Si at 300°C for 80 cycles81                                       |

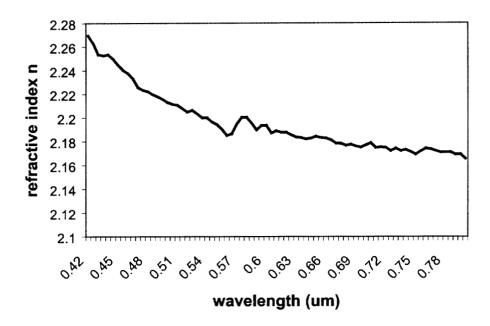

| Fig. 5.4  | Refractive index of as-deposited Ta <sub>2</sub> O <sub>5</sub> film of 75 nm in                  |

|           | the visible region81                                                                              |

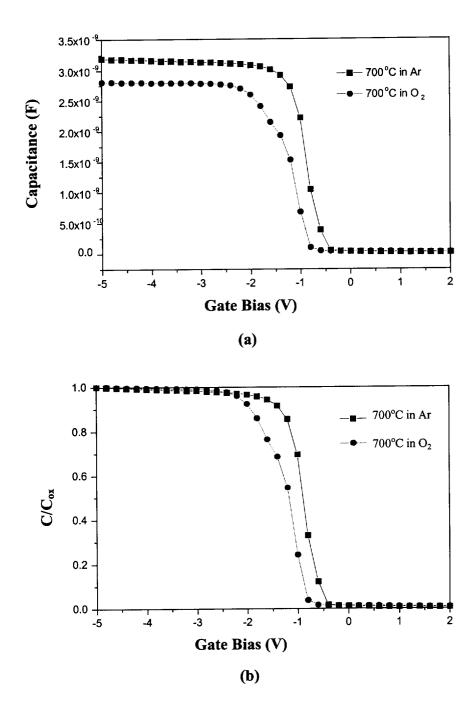

| Fig. 5.5  | High frequency C-V curves for 16 nm thick of Ta <sub>2</sub> O <sub>5</sub>                       |

|           | annealed at 700°C for 60 s in Ar and O2. (a) C-V curve                                            |

|           | (b) Normalized C-V curve87                                                                        |

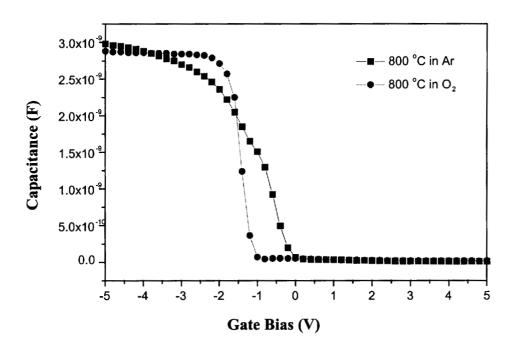

| Fig. 5.6  | High frequency C-V curves for 17 nm thick of Ta <sub>2</sub> O <sub>5</sub>                       |

|           | annealed at 800°C for 60 s in Ar and O <sub>2</sub> 88                                            |

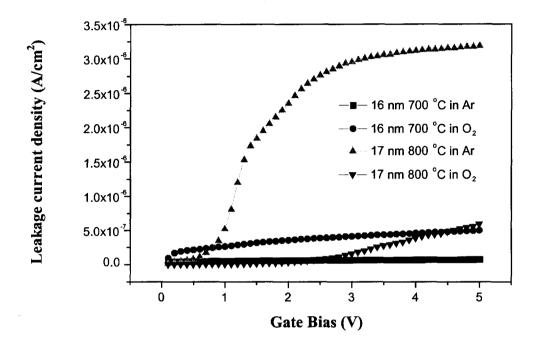

| Fig. 5.7  | The leakage current density of MOS capacitors with 16 nm                                          |

|           | and 17 nm thick Ta <sub>2</sub> O <sub>5</sub> gate dielectric layers and under                   |

|           | different annealing conditions90                                                                  |

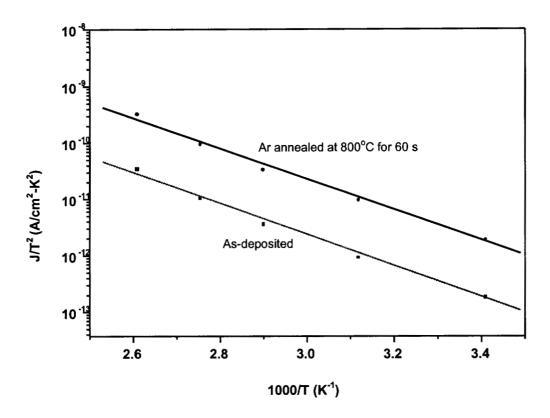

| Fig. 5.8  | J/T <sup>2</sup> plots of gate leakage current under positive gate bias +2.0                      |

|           | volts for as-deposited and Ar annealed Ta <sub>2</sub> O <sub>5</sub> film of 17 nm91                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------------|

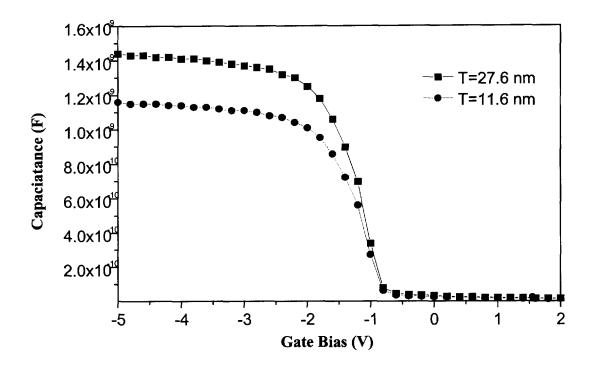

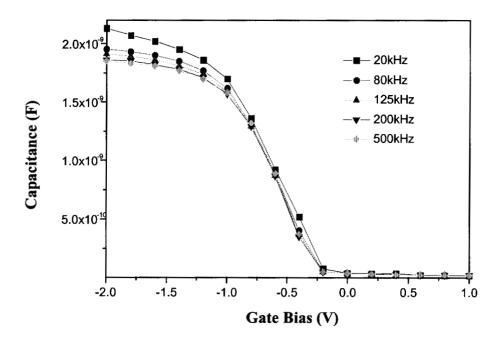

| Fig. 5.9  | C-V characteristics of the HfO <sub>2</sub> thin films with thicknesses                                                      |

|           | 27.6 nm and 11.6 nm respectively. The thicknesses include                                                                    |

|           | 2.76 nm of nitride. The area of the capacitor is 0.0028 cm <sup>2</sup> 94                                                   |

| Fig. 5.10 | An AFM image of the Ta <sub>2</sub> O <sub>5</sub> - HfO <sub>2</sub> nanolaminates. The                                     |

|           | stack is $5 \text{ Ta}_2\text{O}_5 + 2 \times (10 \text{ Ta}_2\text{O}_5 + 10 \text{ HfO}_2) \dots 100$                      |

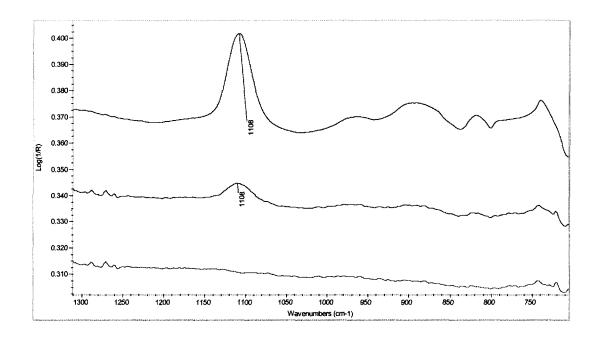

| Fig. 5.11 | FTIR spectra of Ta <sub>2</sub> O <sub>5</sub> /HfO <sub>2</sub> nanolaminates/Si <sub>3</sub> N <sub>4</sub> /Si and        |

|           | Si <sub>3</sub> N <sub>4</sub> /Si. The top curve is the spectrum of the nanolaminates,                                      |

|           | the middle one is nitrided silicon substrate, the bottom one is                                                              |

|           | the subtraction of two curves showing that there is no SiO <sub>2</sub>                                                      |

|           | forming at the interface101                                                                                                  |

| Fig. 5.11 | FTIR spectra of Ta <sub>2</sub> O <sub>5</sub> /HfO <sub>2</sub> nanolaminates/Si <sub>3</sub> N <sub>4</sub> /Si and        |

|           | Si <sub>3</sub> N <sub>4</sub> /Si. The top curve is the spectrum of the nanolaminates,                                      |

|           | the middle one is nitrided silicon substrate, the bottom one is the                                                          |

|           | subtraction of two curves showing that there is no SiO <sub>2</sub>                                                          |

|           | forming at the interface102                                                                                                  |

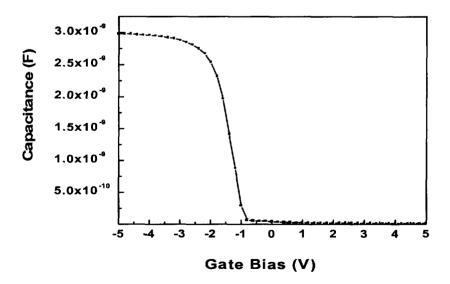

| Fig. 5.13 | Calculation of the flatband voltage from a C-V measurement.                                                                  |

|           | The gate voltage corresponds to the peak of $\frac{d^2}{dV_G^2} \left[ \frac{1}{(C_{HF}/C_{ox})^2} \right]$                  |

|           | was the flatband voltage103                                                                                                  |

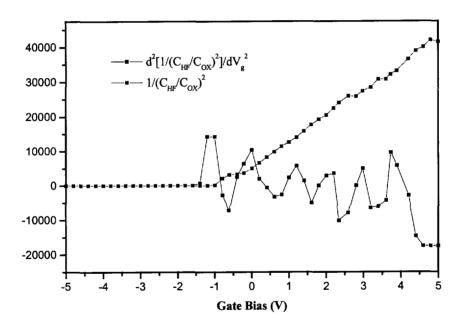

| Fig. 5.14 | Hysterisis characteristic of Ta <sub>2</sub> O <sub>5</sub> -HfO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> nanolaminates, |

|           | the $Ta_2O_5$ -HfO <sub>2</sub> is 5 $Ta_2O_5$ + $10(8\times Ta_2O_5 + 8\times HfO_2)$ and $Si_3N_4$                         |

|           | is 2.12 nm104                                                                                                                |

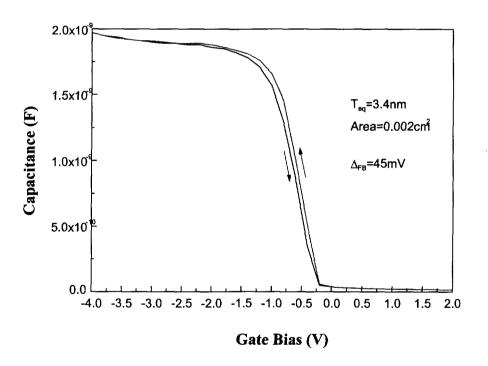

| Fig. 5.15 | Frequency dependency of C-V curve of Ta <sub>2</sub> O <sub>5</sub> -HfO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub>        |

|           | nanolaminates, the $Ta_2O_5$ -HfO <sub>2</sub> is 5 $Ta_2O_5$ + $10(8\times Ta_2O_5 + 8\times HfO_2)$                        |

|           | and Si <sub>3</sub> N <sub>4</sub> is 2.12 nm105                                                                             |

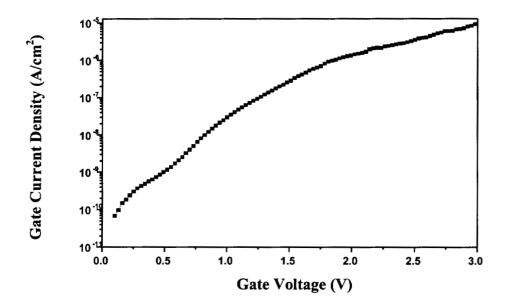

| Fig. 5.16 | The leakage current density vs. applied voltage for the                                                                      |

|           | A1-Ta <sub>2</sub> O <sub>5</sub> /HfO <sub>2</sub> -Si <sub>2</sub> N <sub>4</sub> -Si capacitor. The thickness of the      |

|           | nanolaminates was 7.4 nm. The area of the capacitor                                                                                         |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

|           | is 0.0028 cm <sup>2</sup> 107                                                                                                               |

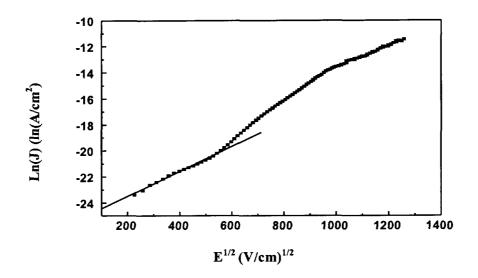

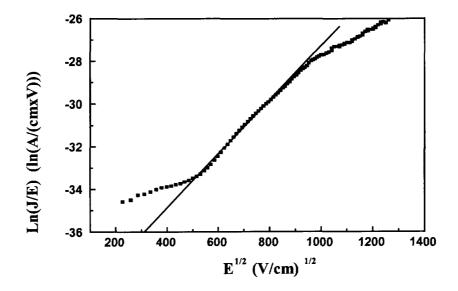

| Fig. 5.17 | The $ln(J)$ vs $E^{1/2}$ is plotted for the Al-Ta <sub>2</sub> O <sub>5</sub> /HfO <sub>2</sub> -Si <sub>3</sub> N <sub>4</sub> -Si (MIS)   |

|           | capacitor. The straight line characteristic at low electric field                                                                           |

|           | (< 0.4 MV/cm) indicates Schottky emission108                                                                                                |

| Fig. 5.18 | The $ln(J/E)$ vs. $E^{1/2}$ is plotted for the Al-Ta <sub>2</sub> O <sub>5</sub> /HfO <sub>2</sub> -Si <sub>3</sub> N <sub>4</sub> -Si(MIS) |

|           | capacitor. The straight-line characteristic at relative high electric                                                                       |

|           | field (> 0.4 MV/cm) indicates Poole-Frenkel conduction108                                                                                   |

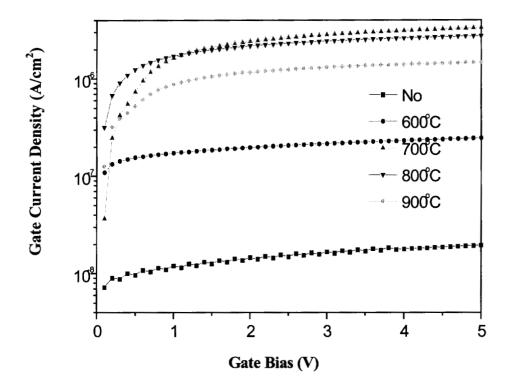

| Fig. 5.19 | Gate current density of as-deposited and RTA treated                                                                                        |

|           | Ta <sub>2</sub> O <sub>5</sub> - ZrO <sub>2</sub> nanolaminates grown on nitrided Si substrates.                                            |

|           | The thickness of the nanolaminates is about 3.7 nm and the                                                                                  |

|           | nitride thickness is 2.76 nm111                                                                                                             |

| Fig. 5.20 | Gate current density of as-deposited and O2 RTA treated                                                                                     |

|           | ZrO <sub>2</sub> - HfO <sub>2</sub> nanolaminates grown on nitrided Si substrates.                                                          |

|           | The thickness of the nanolaminates is about 3.4 nm and the                                                                                  |

|           | nitride thickness is 2.76 nm                                                                                                                |

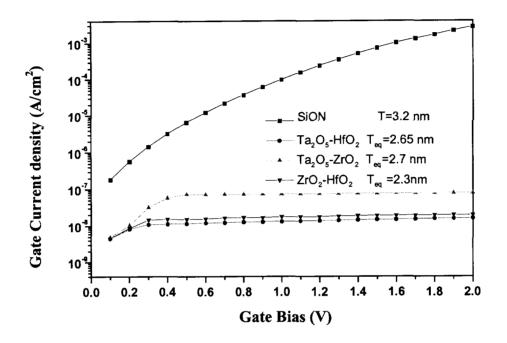

| Fig. 5.21 | Gate leakage current of SiON, Ta <sub>2</sub> O <sub>5</sub> - HfO <sub>2</sub> nanolaminates/Si <sub>3</sub> N <sub>4</sub> ,              |

|           | Ta <sub>2</sub> O <sub>5</sub> - ZrO <sub>2</sub> nanolaminates/Si <sub>3</sub> N <sub>4</sub> , and ZrO <sub>2</sub> - HfO <sub>2</sub>    |

|           | nanolaminates/Si <sub>3</sub> N <sub>4</sub> . The thickness of Si <sub>3</sub> N <sub>4</sub> is 2.76 nm for all                           |

|           | three nanolaminates                                                                                                                         |

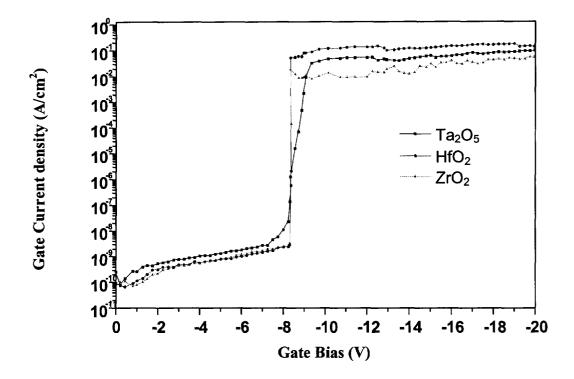

| Fig. 5.22 | Ramped I-V characteristic of MIS capacitors with binary                                                                                     |

|           | high k films driven to breakdown in the accumulation mode.                                                                                  |

|           | All films are of 8 nm thick                                                                                                                 |

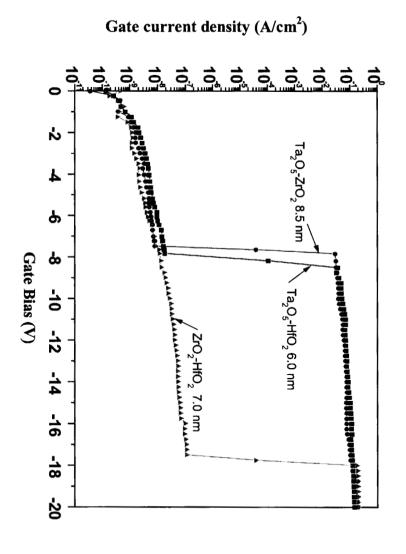

| Fig. 5.23 | I-V characteristics of MIS capacitors of Ta <sub>2</sub> O <sub>5</sub> - HfO <sub>2</sub> ,                                                |

|           | Ta <sub>2</sub> O <sub>5</sub> - ZrO <sub>2</sub> and ZrO <sub>2</sub> - HfO <sub>2</sub> nanolaminates in the                              |

|           | accumulation region 118                                                                                                                     |

#### **ABSTRACT**

Growth and Characterization of High Permittivity Thin Film Nanolaminates Fabricated by Atomic Layer Epitaxy

Hui Zhang, B. S., M. S.

Ph. D., Oregon Graduate Institute of Science and Technology May, 2000

Thesis Professor: Dr. Rajendra Solanki

This thesis considers three issues regarding high permittivity thin films and their nanolaminates. Atomic layer epitaxy, the process technique used to deposit thin films of Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub> and their nanolaminates will be discussed first. Material properties of these films are presented next. Finally, the electrical properties and dielectric characteristics are investigated.

Atomic layer epitaxy was used to grow binary oxides (Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, and ZrO<sub>2</sub>) and their nanolaminates (Ta<sub>2</sub>O<sub>5</sub> - HfO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub> - ZrO<sub>2</sub>, HfO<sub>2</sub>-ZrO<sub>2</sub>) on silicon substrates. Metallic chlorides and water vapor were used as source materials. The as-deposited Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub> and ZrO<sub>2</sub> thin films grown at 300°C were amorphous. The crystallization temperatures of these films were 800°C, 800°C and 700°C, respectively.

Transmission electron microscope (TEM) showed that silicon surface oxidation occurred during the high permittivity film growth due to the use of water vapor. A thin layer of silicon nitride was grown by rapid thermal nitridation as a barrier layer prior to the deposition of high permittivity films.

Capacitors made with these binary oxides and their nanolaminates were characterized by capacitance – voltage (C-V) and current – voltage (I-V) measurements. Dielectric constants, flatband voltage and interface fixed charges were calculated based on C-V data. Leakage current of nanolaminates was dramatically reduced compared to

that of binary oxides. It was found that Schottky emission and Poole-Frenkel conduction were the major leakage mechanisms. Crystallization of amorphous films had two effects on the dielectric properties. First, it increased the dielectric constant, which was desirable. Secondly, it created grain boundaries that facilitate the current leakage in the dielectric films. As the thicknesses of high permittivity films decreased, the dielectric constants dropped. This reduction in dielectric constant has been shown to depend on the number of atomic monolayers and the atomic polarizability of the film. The investigation of these high permittivity nanolaminates suggested that they could be useful for future gate dielectric material.

#### Chapter 1

#### Introduction

The metal-oxide-semiconductor or MOS structure is, without a doubt, the core structure in modern-day microelectronics. Although a quasi-MOS device was first proposed in the 1920s, the metal-oxide-semiconductor fields effect transistor (MOSFET) achieved practical status in 1960, mainly attributed to D. Kahng and M. M. Atalla who filed patents on the Si-SiO<sub>2</sub> based FET [1]. Over the last four decades, the integrated circuit (IC) market has increased dramatically. In 1960s the IC market was broadly based on the bipolar transistors. Since 1970s, however, digital MOS ICs has prevailed. MOSFET and related integrated circuits now constitute about 90% of the semiconductor device market.

Throughout the MOS development history, the quality of the gate SiO<sub>2</sub> and its interface to Si has always been playing an essential role, in both MOS and Dynamic Random Access Memory (DRAMs) [2]. There were strong efforts to obtain a dielectric film superior to the thermally grown SiO<sub>2</sub>. They include SiO<sub>2</sub> formed using plasma [3], laser [4], and CVD (Chemical Vapor Deposition) technique [5], Si<sub>3</sub>N<sub>4</sub> [6], and ferroelectrics [7]. Such films having other interfaces than thermal SiO<sub>2</sub> to Si, however, suffered from inferior dielectric quality, especially with respect to the defect charge density, and so have not been implemented as gate dielectrics.

Continued Ultra-Large Scale Integration (ULSI: more than 10<sup>7</sup> transistors on a chip) has been achieved mainly by decreasing the size of an individual transistor as well

as by increasing the chip size and circuit complexity, as typically seen for DRAM whose memory size grows at a rate of approximately four times every three years. The feature size (L) of an individual device continues to decrease to two thirds or a little bit less than that of a prior generation. For example, L was on the order of several micrometers in the 1970s, the decade of Large-Scale Integration (LSI: 10<sup>3</sup> ~ 10<sup>4</sup> transistors on a chip), while that for the ULSL is now scaled down to 0.25μm or less. Accordingly, the thickness of the gate oxides has been reduced from ~100nm in the LSI technology to ~10nm or less for ULSI. As described in the National Technology Roadmap for Semiconductors (Table 1-1), the device dimension will shrink from 0.25μm in 1997 to 0.10μm in 2005.

Table 1-1 The International Technology Roadmap [8]

| Year                  | 1999  | 2000 | 2001 | 2002  | 2003 | 2004 | 2005  |

|-----------------------|-------|------|------|-------|------|------|-------|

| Technology Node       | 180nm |      |      | 130nm |      |      | 100nm |

| DRAM ½ Pitch (nm)     | 180   | 165  | 150  | 130   | 120  | 110  | 100   |

| MPU Gate Length (nm)  | 140   | 120  | 100  | 85-90 | 80   | 70   | 65    |

| MPU/ASIC ½ Pitch (nm) | 230   | 210  | 180  | 160   | 145  | 130  | 115   |

| ASIC Gate Length (nm) | 180   | 165  | 150  | 130   | 120  | 110  | 100   |

The scaling trends discussed above lead to several limitations and issues of the MOS technology, mainly to (a) small-geometry effects, (b) limited performance under high electrical field, (c) hot-carrier-induced device degradation, (d) gate-induced drain leakage, and (e) gate-dielectric reliability [9]. The limitations (b, c, e) are closely related to the quality of the gate dielectric and its interface to silicon, while the limitations (a, b, d) are more dependent on the gate dielectric thickness. In either case, almost all the limitations become more critical as the gate dielectric thickness is scaled down to

nanometer scale. Generally, increasing internal electric fields will enhance the circuit performance while it degrades reliability. Therefore, trade-off between performance and reliability has become one of the most important device design issues in ULSI technology.

With the continuous shrinkage of the silicon dioxide thickness, direct tunneling current through the dielectric will be a very serious concern. A major limiting factor in transistor scaling beyond the current 0.18-µm design rules has been the difficulty to grow high quality, ultra-thin oxides as the tunneling limit of 2.5nm for SiO<sub>2</sub> is approached and gate currents exceed 1 A/cm<sup>2</sup>. Furthermore, SiO<sub>2</sub> is not a good diffusion barrier for gate electrode dopants, such as boron. Even with nitrogen incorporation [10, 11], it is difficult to utilize ultra-thin nitrided oxides for sub-0.25µm technologies due to high tunneling current and rough Si-SiO<sub>2</sub> interface. Therefore, a high dielectric constant (k) material of equivalent electrical dielectric thickness is a possible alternative to thermally grown SiO<sub>2</sub>. High k materials [12-14] have been studied for storage capacitors but successful demonstrations for MOSFET are rare [15]. The biggest challenge in DRAM technology is to shrink the size of the memory cell, while maintaining enough capacitance to store a bit. With the traditional SiO<sub>2</sub> as the dielectric, special topologies have to be used to achieve high capacitance and high density. This results in planarization problem and process complexity. Therefore, it is very desirable to replace the current SiO<sub>2</sub> with high permittivity materials.

As a relatively high permittivity material, silicon nitride film has been studied extensively as a gate or capacitor dielectric. It is not used alone but in combination with  $SiO_2$  to form silicon oxynitride [16] or nitride/oxide stack [17]. However, the dielectric constant (7.5~7.8) of silicon nitride is not high enough for future 0.10µm ULSI devices. According to the National Technology Road Map for semiconductors (1997), gate dielectric scaling down to 2nm is desired from 2006 onward. When the  $SiO_2$  thickness is reduced below 2 nm, alternative high permittivity dielectrics such as  $Ta_2O_5$ ,  $TiO_2$ ,  $HfO_2$  and  $ZrO_2$  must be considered.  $Ta_2O_5$  has been studied for applications as the capacitor

dielectric in gigabit DRAMs [18-20]. Ta<sub>2</sub>O<sub>5</sub> has also been proposed as MOSFET gate dielectric for high-speed circuit in simulation study [21]. Recently MOSFET devices have also been fabricated using high k thin films such as Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub> and ZrO<sub>2</sub>. Some of these results were reported in references [22-25]. One major obstacle in using high k materials is that a solid material with higher permittivity tends to have narrower bandgap. This is deduced from a reduced cohesive force according to the quantum-mechanical consideration [26], thereby suffering from a larger leakage current.

The purpose of this research was to study the deposition of Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub> and ZrO<sub>2</sub> films and their nanolaminates (Ta<sub>2</sub>O<sub>5</sub>-HfO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>-ZrO<sub>2</sub> and HfO<sub>2</sub>-ZrO<sub>2</sub>) using atomic layer epitaxy (ALE) technique and to characterize the material and electrical properties of MOS capacitors made with these films.

This thesis contains 6 chapters including this introduction. In chapter 2, dielectric properties of materials are discussed and the relationship between dielectric constant and bandgap is presented. This chapter also includes basic theory of MOS system and the ULSI device scaling. The ALE technique and its application are described in chapter 3. In chapter 4, the experimental results of the Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, ZrO<sub>2</sub> and their nanolaminates by ALE technique are presented. The fabrication sequence and material characteristics are also included in this chapter. Chapter 5 presents material and electrical properties of MOS capacitors built with these high k thin films. C-V characteristics at high frequency were investigated and dielectric constants were extracted from C-V measurement. I-V characteristics were studied to determine the leakage mechanisms and reliability. Argon and oxygen annealing effects on leakage current are described. Summary and conclusions were presented in chapter 6.

#### References

- [1] M. M. Atalla, E. Tannenbaum, and E. J. Scheibner, "Stabilization of silicon surfaces by thermally grown oxides," Bell Syst. Tech. J. 38, 1959, pp. 749-754.

- [2] P. Singer, "Dierections in dielectrics in CMOS and DRAMs," Semiconductor International 17, 1994, pp. 56-59.

- [3] V. K. Bhat, K. N. Bhat, and A. Subrahmanyam, "Electrical characterization of Ultrathin oxides of silicon grown by N<sub>2</sub>O plasma assisted oxidation," J. Electronic Materials **20**, 2000, pp. 399-404.

- [4] I. W. Boyd, "Incorporation of carbon dioxide laser-grown oxide layers into conventional metal-oxide-silicon devices," J. Appl. Phys. 54, 1983, pp. 3561-3565.

- [5] L. G. Meiners, "Indirect plasma deposition of silicon dioxide," J. Vac. Sci. Technol. 21,1982, pp. 655-658.

- [6] Y. Kuo, "PECVD silicon nitride as gate dielectric for amorphous silicon thin film transistor," J. Electrochem. Soc. 142, 1995, pp. 186-190.

- [7] J. R. Pfiester, Performance limit of CMOS very large scale integration, Ph.D. Thesis, Elect. Eng. Dept., Stanford University, Technology Report, No. G541-1 (1984).

- [8] The International Technology Road Map for Semiconductors, Semiconductor Industry Association, San Jose, CA, 1999.

- [9] T. Hori, Gate Dielectrics and MOS ULSIs, Springer-Verlag Berlin Heidelberg, 1997, p. 110.

- [10] Y. Yamamoto, T. Ogura, Y. Saito, K. Uwasawa, T. Tatsumi, and T. Mogami, "An advanced 2.5nm oxidized nitride gate dielectric for highly reliable 0.25µm MOSFET," Symp. on VLSI Technology Digest of Technical Papers, 1997, pp. 45-46.

- [11] X. Guo and T. P. Ma, "Tunneling Leakage current in oxynitride: dependence on oxygen/nitrogen content," IEEE Electron Device Letters 19, June 1998, pp. 207-209.

- [12] M. Hao, K. Lai, W. M Chen, and J. C. Lee, "Surface cleaning effect on dielectric integrity for Ultrathin oxynitride grown in N<sub>2</sub>O," Appl. Phys. Lett. **65**, 1994, pp. 1133-1135.

- [13] Y. Matsui, K. Torri, M. Hirayama, Y. Fujisaki, S. Iijima, and Y. Ohji, "Reduction of current leakage in chemical vapor deposited Ta<sub>2</sub>O<sub>5</sub> thin films by oxygen radical annealing," IEEE Electron Device Letters 17, 1996, pp. 431-433.

- [14] S.C. Sun and T. F. Chen, "Leakage current reduction in chemical-vapor deposited  $Ta_2O_5$  films by rapid thermal annealing in  $N_2O$ ," IEEE Electron Device Letters 17, 1996, pp. 355-357.

- [15] M. Matsui, H. Hagayoshi, G. Muto, S. Tanimoo, K. Kuroiwa, and Y. Tarui, "Amorphous silicon thin film transistors employing photoprocessed tantalum oxide films as gate insulators," Jpn. J. Appl. Phys. 29, 1990, pp. 62 -66.

- [16] B. Maiti, P. J. Tobin, V. Misra, R. I. Hedge, K. G. Reid, and C. Gelatos, "High performance 20 Å NO oxynitride for gate dielectric in deep sub quarter micron CMOS technology," IEEE IEDM, Washington, DC, Dec. 7-10, 1997, pp. 651-654.

- [17] B. Y. Kim, H. F. Luan, and D. L. Kwong, "Ultra thin (<3nm) high quality nitride /oxide stack gate dielectrics fabricated by in-situ rapid thermal processing," IEEE IEDM, Washington, DC, Dec. 7-10, 1997, pp. 463-466.

- [18] K. A. Mckinley and N. P. Sandler, "Tantalum pentoxide for advanced DRAM applications," Thin Solid Films **290-291**, 1996, pp. 440-446.

- [19] M. B. Lee, H.D. Lee, B.L. Park, U.I.Chung, Y.B. Koh, and M.Y. Lee, "Electrical characterization of CVD TiN upper electrode for Ta<sub>2</sub>O<sub>5</sub> capacitor," IEEE IEDM, San Francisco, CA, Dec. 8-11, 1996, pp. 683-686.

- [20] S. C. Sun and T. F. Chen, "A new post-deposition annealing method using furnace N<sub>2</sub>O for the reduction of leakage current of CVD Ta<sub>2</sub>O<sub>5</sub> storage capacitors," IEEE IEDM, San Francisco, CA, Dec. 8-11, 1996, pp. 687-690.

- [21] H. Shimada and T. Ohmi, "Current drive enhancement by using high-permittivity gate insulator in SOI MOSFET's and its limitation," IEEE Trans. Electron Devices 43, 1996, pp. 431-435.

- [22] J. L. Autran, R.Devine, C. Chanelieve, and B. Balland, "Fabrication and characterization of Si-MOSFET's with PECVD amorphous Ta<sub>2</sub>O<sub>5</sub> gate insulator," IEEE Electron Device Letters 18, 1997, pp. 447-449.

- [23] D. Park, Y. King, Q. Lu, T. King, C. Hu, A. Kalnisky, S. Tay, and C. C. Cheng, "Transistor characteristics with  $Ta_2O_5$  gate dielectric," IEEE Electron Device Letters 19, Nov. 1998, pp. 441-443.

- [24] B. H. Lee, L. Kang, W-J Qi, R. Nieh, Y. Joen, K. Onishi, and J. C. Lee, "Ultrathin hafnium oxide with low leakage and excellent reliability for alternative gate dielectric application," IEEE IEDM, Washington, DC, Dec.5-8, 1999, pp. 133-136.

- [25] W. J. Qi, R. Nieh, B. H. Lee, L. Kang, Y. Jeon, K. Onishi, T. Ngai, S. Banerjee, and J. C. Lee, "MOSCAP and MOSFET characteristics using ZrO<sub>2</sub> gate dielectric deposited directly on Si," IEEE IEDM, Washington, DC, Dec.5-8, 1999, pp. 145-148.

- [26] K. W. Boer, Survey of Semiconductor Physics, Van Nostrand Reinhold, 1990, p. 26.

### Chapter 2

#### **MOS System and High Permittivity Materials**

In this chapter, the history and fundamentals of the metal-oxide-semiconductor structure are reviewed. Basic device physics and device characterization techniques are discussed. Device scaling and demand for high permittivity materials as gate dielectrics are presented as well. This chapter also includes the discussion of dielectric properties of high permittivity materials and their application in ULSI devices.

#### 2.1 MOS system

An MOS structure shown in Fig. 2.1 consists of a top electrode called a gate generally made by vacuum deposition of a metal or by chemical deposition of polysilicon, an oxide layer usually thermally grown, and an ohmic contact to the silicon substrate. An MOS capacitor has only two terminals, and is the simplest and most useful device in the study of semiconductor surfaces and gate dielectrics [1]. A second metallic layer present on the bottom side of the semiconductor provides an electrical contact to the silicon substrate.

Fig. 2.1 MOS Structure

An ideal MOS structure has the following explicit properties: (1) the metallic gate is sufficiently thick so that it can be considered an equipotential region under ac as well as dc biasing conditions; (2) the oxide is a perfect insulator with zero current flowing through the oxide layer under all static biasing conditions; (3) there are no charge centers located in the oxide or at the oxide-semiconductor interface; (4) the semiconductor is uniformly doped; (5) the semiconductor is sufficiently thick so that, regardless of the applied gate potential, a field-free region (so called Si "bulk") is encountered before reaching the back contact [2]. With the scaling down of device size, the idealization (2) and (3) have been challenged.

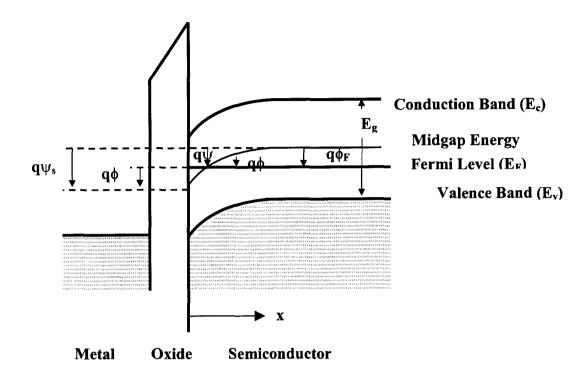

The energy band diagram is an indispensable aid in visualizing the internal status of the MOS structure under static biasing conditions. As schematically illustrated in Fig. 2.2, when an ideal MOS capacitor with a p-type substrate is biased with  $V_g$  not equal to zero, basically three situations may arise at the semiconductor surface.

Fig. 2.2a Accumulation region of MOS capacitor

Fig. 2.2b Depletion region of MOS capacitor

Fig. 2.2c Inversion region of MOS capacitor

Regardless of the gate potential  $V_g$ , the Fermi level  $E_F$  remains constant throughout the semiconductor since no current flows in the semiconductor. When  $V_g < 0$ , the negative gate potential attracts positive charges under the interface in the semiconductor (holes in the p-type Si in the case of Fig. 2.2a). This results in an enhanced concentration of majority carriers (holes for p-type substrate), called accumulation, at the interface of oxide and semiconductor. When a positive gate voltage is applied, negative charges are introduced near the semiconductor and oxide interface. This, at first, is due to the holes being pushed away from the semiconductor surface, leaving behind a depletion region consisting of uncompensated acceptor ions as illustrated in Fig. 2.2b. As the positive gate potential increases, the surface depletion region is widened. Accordingly, the total electrostatic potential variation, as represented by the energy band bending, increases so that the midgap energy  $E_i$  crosses over the quasi-Fermi level  $E_F$  of the semiconductor. Beyond this point, the concentration of

minority carriers (electrons in this case) is larger than that of the majority carriers (holes) near the semiconductor and oxide interface. Therefore, the surface is rich in minority carriers, so called under inversion condition, as shown in Fig. 2.2c. Similar results can be obtained for n-type semiconductors when the gate bias is reversed.

To derive the capacitance – voltage (C-V) characteristics of the MOS structure, we need to develop a relation for the charge in the semiconductor to the surface band bending potential  $\psi_s$ . A p-type semiconductor is used to illustrate the C-V characteristics as show in Fig. 2.3. An arrow pointing down represents a positive potential. Band bending potential ( $\psi$ ) is measured with respect to midgap energy ( $E_i$ ) as a function of the distance x from the interface of oxide and semiconductor. It is defined to be zero in the bulk of the semiconductor, which indicated that gate voltage drop was only applied across the oxide and the semiconductor surface. The surface potential  $\phi$  is defined as the potential difference between  $E_i$  and  $E_F$ , and therefore  $\psi(x)$  can be expressed as  $\phi(x) + \phi_F$ . The n and p are given as functions of either  $\psi(x)$  or  $\phi(x)$  by the following equations:

$$n(x) = N_D \exp(\psi(x) / \phi_t) = n_i \exp(\phi(x) / \phi_t)$$

(2.1a)

$$p(x) = N_A \exp(-\psi(x)/\phi_t) = n_i \exp(-\phi(x)/\phi_t)$$

(2.1b)

where  $n_i$  is the intrinsic carrier concentration,  $\phi_t = kT/q$  is the thermal voltage (~ 26 mV at room temperature),  $N_D(N_A)$  is the donor (acceptor) concentration.

Fig. 2.3 Energy band diagram at the surface of a p-type semiconductor. An arrow pointing down (up) denotes positive (negative) potential. Surface potential  $\phi_s$  is measured with respect to the Fermi level  $E_F$  at the interface. Surface band bending  $\psi_s$  is measured with respect to the intrinsic Fermi level  $E_i$  at the interface.

From the above discussion together with Eqn. 2.1, The following regions of surface band bending potential can be distinguished [3]:

| $\psi_s < 0$                  | Accumulation of holes (bands bending upward)   |

|-------------------------------|------------------------------------------------|

| $\psi_s=0$                    | Flat-band condition $(n < p)$                  |

| $\phi_F>\psi_s>0$             | Depletion of holes (bands bend downward)       |

| $\psi_s =  \varphi_F$         | Intrinsic condition at surface $(n = p = n_i)$ |

| $2\varphi_F>\psi_s>\varphi_F$ | Weak inversion $(N_A > n > p)$                 |

| $\psi_s > 2 \varphi_F$        | Strong inversion $(n > N_A)$                   |

The potential distribution in the semiconductor is described by one-dimensional Poisson equation:

$$\frac{d^2\psi(x)}{dx^2} = -\frac{\rho(x)}{\varepsilon_{\star}} = -\frac{q}{\varepsilon_{\star}} [p(x) - n(x) + N_D - N_A]$$

(2.2)

where p(x) and n(x) is the hole and electron concentration in silicon respectively,  $N_D$  and  $N_A$  are the density of ionized donors and acceptors respectively,  $\varepsilon_s$  is the permittivity of the semiconductor,  $\rho(x)$  is the total space-charge density. Integrating Eqn. 2.1 in conduction with Eqn. 2.2 from the bulk toward the surface [4]

$$\int_{0}^{\partial \psi / \partial x} \frac{\partial \psi}{\partial x} d \left[ \frac{\partial \psi}{\partial x} \right] = -\frac{q}{\varepsilon_{s}} \int_{0}^{\psi} \left[ N_{A} \left( e^{-\psi / \phi_{t}} - 1 \right) - N_{D} \left( e^{\psi / \phi_{t}} - 1 \right) \right] d\psi \quad (2.3)$$

gives the relation between potential  $\psi$  and the electric field E:

$$E = -\frac{\partial \psi}{\partial x} = \pm \sqrt{2} \frac{\phi_t}{L_D} F(\psi, N_A)$$

(2.4)

with the positive sign for  $\psi > 0$  and the negative sign for  $\psi < 0$ . The extrinsic Debye length  $L_D$  which is a characteristic length of semiconductors, and  $F(\psi, N_A)$  are defined as

$$L_D = \sqrt{\frac{\varepsilon_s \phi_t}{q N_A}}$$

$$(2.5a)$$

$$F(\psi, N_A) = \sqrt{e^{-\psi/\phi_t} + \psi/\phi_t - 1 + (n_i/N_A)^2 (e^{\psi/\phi_t} - \psi/\phi_t - 1)}$$

$$(2.5b)$$

At thermal equilibrium the depletion layer width of abrupt junction is about  $8L_D$  for Si. The surface electric field  $E_s$  is given by substituting  $\psi_s$  for  $\psi$  into Eqn. 2.4. By

Gauss's law, the total charge  $Q_s$  per unit area in the semiconductor required to produce the field  $E_s$  is:

$$Q_s \equiv -\varepsilon_s E_s = \mp \sqrt{2} \frac{\varepsilon_s \phi_t}{L_D} F(\psi_s, N_A)$$

(2.6)

The differential capacitance of the semiconductor is given by:

$$C_{s} \equiv \frac{\partial Q_{s}}{\partial \psi_{s}} = \frac{\varepsilon_{s}}{\sqrt{2}L_{D}} \frac{\left|1 - e^{-\psi_{s}/\phi_{t}} + \left(n_{s}/N_{A}\right)^{2} \left(e^{\psi_{s}/\phi_{t}} - 1\right)\right|}{F(\psi_{s}, N_{A})}$$

(2.7)

The total capacitance C of a MOS system is a series combination of insulator capacitance  $C_i$  and the semiconductor capacitance  $C_s$ :

$$C = \frac{1}{1/C_i + 1/C_s} \tag{2.8}$$

C<sub>i</sub> is the oxide capacitance per unit area:

$$C_i = \frac{\varepsilon_i}{t_i} \tag{2.9}$$

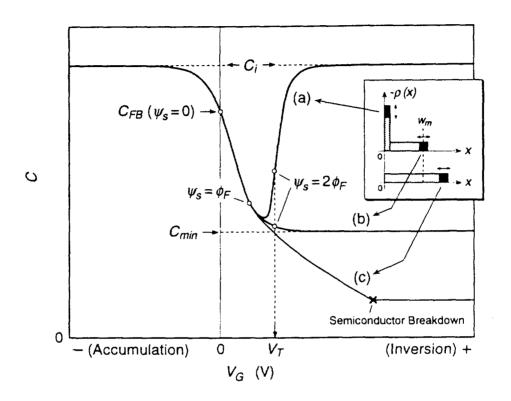

where  $\varepsilon_i$  is the permittivity of the insulator (oxide in most cases) and  $t_i$  is the thickness of the insulator. When a gate voltage is applied to the MOS structure, the ideal MOS capacitance – voltage (C-V) characteristics for a p-type semiconductor can be described by the C-V curves at high- and low-frequency conditions as shown in Fig. 2.4.

Fig. 2.4 MOS capacitance-voltage characteristics under (a) low frequency, (b) high-frequency, and (c) deep –depletion conditions

[5]

For the low frequency C-V curve (a) in Fig. 2.4, accumulation of holes occurs with a negative gate bias ( $V_g < 0$ ) and  $Q_s$  (hole charge in this case) dominates. Therefore the differential capacitance of the semiconductor  $C_s$  is much larger than the capacitance of the insulator  $C_i$ . As a result, the total C of the MOS is close to its maximum  $C_i$ . As  $V_g$  is increased to be slightly positive, a depletion layer, which may act as a dielectric layer of thickness w in series with the insulator, forms and widens near the semiconductor surface. Therefore the total capacitance C decreases substantially according to

$$C = \frac{1}{t_i / \varepsilon_i + w / \varepsilon_s} \tag{2.10}$$

As  $V_g$  is further increased to exceed the so called threshold voltage  $V_t$  at which strong inversion occurs ( $\psi_s \approx 2\phi_F$ ), total capacitance C increases again after showing a minimum and then approaching the maximum  $C_i$ , since the charges  $Q_s$  in the inversion layer of semiconductor increases dramatically by a slight increase of the surface band bending potential  $\psi_s$ . Once strong inversion occurs, w reaches its maximum  $w_m$ . Simplifying F in Eqn. 2.5b by expressing it only through the second term and equating  $Q_s$  at  $\psi_s \approx 2\phi_F$  with Eqn. 2.6 to  $Q_D = qN_Aw_m$ ,  $w_m$  is given by:

$$w_m \approx \sqrt{\frac{2\varepsilon_s 2\phi_F}{qN_A}} = 2\sqrt{\frac{\phi_F}{\phi_t}} L_D \tag{2.11}$$

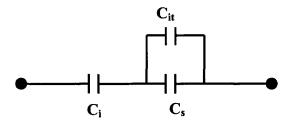

To measure the differential capacitance, the AC signal of small amplitude  $\delta V$  with the angular frequency  $\omega$  ( $\omega = 2\pi f$ , f being frequency) is superimposed onto the DC voltage  $V_g$ . Comparing the curves a and b in Fig. 2.4, it should be noticed that the increase of capacitance in inversion region occurs at low frequencies where the recombination-generation rates of minority carriers can keep up with the small signal variation and lead to charge exchange with the inversion layer. These minority carriers will contribute an additional capacitance  $C_{it}$  to the measured low frequency C-V curve. At low frequencies, the C-V characteristics are represented by the equivalent circuit in Fig. 2.5. The total capacitance can be calculated using Eqn. (2.12).

$$\frac{1}{C_{LF}} = \frac{1}{C_i} + \frac{1}{C_s + C_{tt}}$$

(2.12)

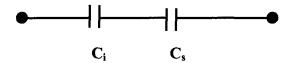

At higher frequencies, interface traps lag behind the small-signal AC change with the minority –carrier response time. The capacitance at high frequency can be given by:

$$C_{HF} = \frac{C_i C_s}{C_i + C_s} \tag{2.13}$$

This capacitance corresponds to the equivalent circuit shown in Fig. 2.6.

Fig. 2.5 Low frequency equivalent circuit of the MOS

Fig. 2.6 High frequency equivalent circuit of the MOS capacitor

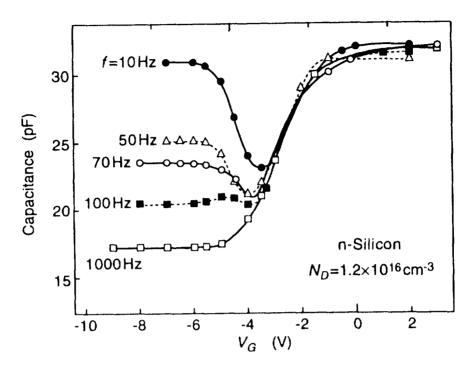

An experimental set of low frequency C-V data is shown in Fig. 2.7. It is obvious that for this Si-SiO<sub>2</sub> system the onset of low frequency curves occurs at  $f \le 100$  Hz.

Fig. 2.7 MOS C-V curves measured at room temperature with frequency as a parameter. The substrate is n-type.

[6]

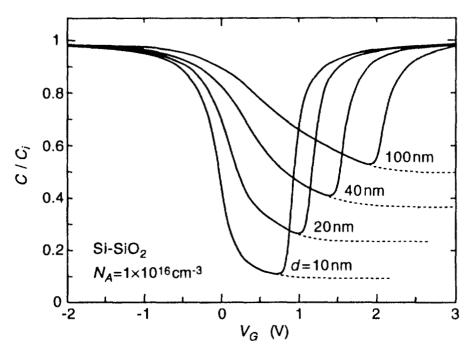

The capacitance-voltage characteristics of an ideal MOS structure vary not only with the frequency but also the thickness of the oxide layer and the doping concentration of the substrate. As the thickness d is made thinner or the substrate doping is made lighter, a large variation of capacitance is observed, as illustrated in Fig. 2.8. In these figures, the dielectric constant  $k = \varepsilon_i / \varepsilon_0$  of SiO<sub>2</sub> is approximately three times smaller than that of silicon (~11.8),  $\varepsilon_0$  being the permittivity of vacuum. In order to replace another insulator for SiO<sub>2</sub>, simply replace its physical thickness t with an electrically equivalent thickness of SiO<sub>2</sub>,  $t_{eq,ox}$  defined as

$$t_{eq,ox} = \frac{\varepsilon_{ox}}{\varepsilon_i} t = \frac{3.9}{\varepsilon_i / \varepsilon_0} t \tag{2.14}$$

Fig. 2.8 MOS C-V characteristics as a function of the oxide thickness. Solid lines correspond to low frequency and dashed lines represent high frequency. The substrate is p-type silicon.

[7]

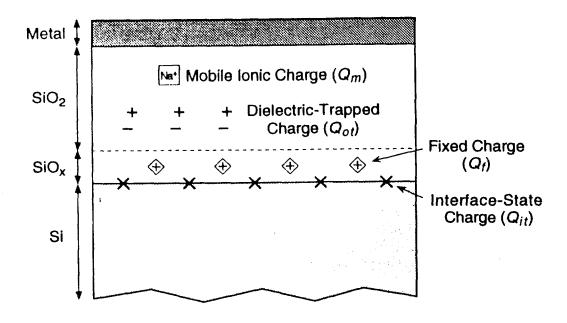

#### 2.2 Charges in a MOS system

An ideal MOS capacitor does not contain any defect charges. However, for a real MOS capacitor there exist different defect charges especially near the  $Si-SiO_2$  interface where the chemical composition is considered not to be stoichiometric ( $SiO_x$ : x <2) unlike in the bulk. As shown in Fig. 2.9, there are four distinct types of charges in the  $Si-SiO_2$  system:  $Q_f$  the fixed charges, located very near the interface but can not exchange charges with the semiconductor;  $Q_{it}$  the interface –state charges, located very close to the

interface and have energy states close to the Fermi level ( $E_F$ ) within the forbidden bandgap as to be able to exchange charges with the semiconductor;  $Q_{ot}$  oxide trapped charges, the trap sites are distributed throughout the bulk of the oxide;  $Q_m$  mobile ionic charges, results from alkali-metal ions (mainly sodium) that are easy to be absorbed in the oxide under bias-temperature aging conditions. Among the four kinds of charges,  $Q_f$  causes the parallel shift  $\Delta V$  along the V axis in a C-V curve, i.e.

$$\Delta V = -\frac{Q_f}{C_i} = -\frac{Q_f t_i}{\varepsilon_i} \tag{2.15}$$

where  $t_i$  is the thickness of insulator (oxide) and  $\varepsilon_i$  is the permittivity of the insulator.

The effects of  $Q_{it}$  on C-V curve are more complicated.  $Q_{it}$  will not simply shift the C-V curve in parallel but stretch them out, because the interface states occupancy varies with the gate bias. Since the interface state levels are distributed across the energy band gap, the interface state density is described as  $D_{it} \equiv \partial N_{it}/\partial E$  in units of cm<sup>-2</sup>/eV. There are two types of interface states, acceptor type and donor type. Acceptor –like interface states are negative when filled with electrons and neutral when empty, whereas donor-like ones are neutral when filled and positive when empty. It is generally considered that interface states above the midgap energy are acceptor type while those below midgap are donor type. An interface state can interact with the silicon conduction band by capturing or emitting an electron and with the silicon valence band by capturing or emitting a hole.

Fig. 2.9 Four categories of oxide charges in the MOS system. [8]

Interface states can be extracted from capacitance, conductance and sub-threshold measurements. Terman used the theoretical and measured high frequency C-V data to extract the interface state density [9]. The interface state density can also be obtained from the low frequency C-V measurement, a technique developed by Berglund [10]. The difference of the theoretical and measured low frequency C-V curve is due to the interaction of interface states with the silicon substrate. Castagne and Vapaille proposed a method to calculate interface state density using both high frequency and low frequency C-V data [11]. The conductance method, proposed by Nicollian and Goetzberger in 1967, is considered the most sensitive approach to determine D<sub>it</sub> [12]. It is based on the measurement of the equivalent parallel conductance G<sub>p</sub> of a MOS capacitor as a function of bias and frequency. The charge pumping method, originally proposed by Brugler in 1969 [13], is suitable for interface states measurement on small geometry MOSFET's

states distribution from the charge pumping effects [14]. The advantage of charge pumping method is the direct measurement of the current that is proportional to D<sub>it</sub> and the fact it can be used to measure regular MOSFET devices without preparing extra test structures.

#### 2.3 Carrier transport in dielectric films

The conductance of an insulating thin film is assumed to be zero in an ideal MOS structure. Real insulators, however, show carrier conductance when the electric field or temperature is sufficiently high. An estimation of the relationship between electric field and the permittivity can be obtained from

$$E_i \varepsilon_i = E_s \varepsilon_s \tag{2.16}$$

where  $E_i$  and  $E_s$  are electric fields in insulator and semiconductor, respectively, and  $\epsilon_i$  and  $\epsilon_s$  are the corresponding permittivities. For the Si-SiO<sub>2</sub> system, the field for silicon at avalanche breakdown is about  $3\times10^5$  V/cm, the corresponding field in oxide is about three time larger ( $\epsilon_{Si}/\epsilon_{SiO_2} = 11.9/3.9$ ), that is, about  $10^6$  V/cm. Under such an electric field, the conduction of electron and hole in the oxide film is negligible even at elevated temperatures. However, when sufficiently high electric fields E (V/cm), are applied to dielectric films, the response is passage of a current density j (A/cm²). If E is small, the response is linear or ohmic, and the conductivity ( $\sigma$ ), given by j/E, is independent of E. For larger applied fields the j-E relationships defining charge transport through dielectric films are more complex. Depending on the mechanism, the conduction process is described in Table 2-1 [15]. In most cases the magnitude of j is strongly temperature-dependent according to Maxwell-Boltzmann relationship.

Table 2-1 Conduction processes in dielectric films

|                  |                                                                                            | TV 1: (I) T                                            |  |

|------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------|--|

|                  |                                                                                            | Voltage(V), Temperature(T)                             |  |

| Process          | j-E relationships                                                                          | dependence                                             |  |

| 1.Schottky       | $j = A^* T^2 \exp \left[ \frac{-q(\Phi_B - (qE/(4\pi\varepsilon_i))^{1/2})}{kT} \right]$   | $T^2$ $-b$                                             |  |

| emission         | $J = A T \exp \left[ \frac{kT}{kT} \right]$                                                | $\approx T \exp \left[ \frac{1}{T} \right]$            |  |

| 2. Frenkel-Poole | $i - P_{\text{over}} \left[ -q(\Phi_B - (qE/(\pi \varepsilon_i))^{1/2}) \right]$           | $= V \exp \left[ + a'V^{1/2} - b \right]$              |  |

| emission         | $j = B \exp \left[ \frac{-q(\Phi_B - (qE/(\pi \varepsilon_i))^{1/2})}{kT} \right]$         | $\approx V \exp \left[ \frac{1}{T} \right]$            |  |

| 3. Tunneling     | $j = \frac{CE^2}{\Phi_B} \exp{-\left[\frac{8\pi (2m)^{1/2} (q\Phi_B)^{3/2}}{3hqE}\right]}$ | $\approx V^2 \exp(-\frac{c}{V})$                       |  |

| 4.Space-charge-  | $j = \frac{4\varepsilon_0 (2q/m)^{1/2}}{2} \frac{E^{3/2}}{4^{1/2}}$                        | $\approx V^{3/2}$                                      |  |

| limited          | $J = \frac{1}{9} \frac{1}{t^{1/2}}$                                                        |                                                        |  |

| 5.Ohmic          | $E_{g}$                                                                                    | $eE_g$                                                 |  |

| (intrinsic)      | $j = ET^{3/2} \exp \left[ -\frac{E_g}{2kT} \right]$                                        | $\approx VT^{3/2} \exp \left[ -\frac{eE_g}{T} \right]$ |  |

| 6.Ionic          | $j \approx \frac{E \exp\left[-E_a/kT\right]}{T}$                                           | $\approx \frac{V \exp(-E_a/T)}{T}$                     |  |

| conduction       | $T \sim \frac{1}{T}$                                                                       | $\sim$ $T$                                             |  |

| (low field)      |                                                                                            |                                                        |  |

| 7.Ionic          | $j \approx \sinh[qaE/kT]\exp[-E_a/kT]$                                                     | $\approx \sinh(gV/T)\exp(-hE_a/T)$                     |  |

| conduction       |                                                                                            |                                                        |  |

| (high field)     |                                                                                            |                                                        |  |

$A^*$  = Richardson constant,  $\Phi_B$  = barrier height, E = electric field,  $\epsilon_i$  = insulator dielectric constant,  $\epsilon_o$  = permittivity of free space, m = effective electron mass, t = insulator thickness, h = Planck's constant,  $E_g$  = insulator energy gap,  $E_a$  = activation energy for ion creation and motion. Constants B, C, a, a, b, c, e, and f are independent of V.

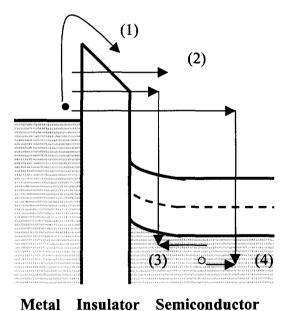

The Schottky emission process is similar to the current transport in the metal-semiconductor contacts that is mainly due to (1) majority carriers transport from the metal over the potential barrier into the semiconductor at moderate temperatures (e.g., 300K). The other contributions to carrier transport from thermionic emission across the metal-insulator interface or the insulator-semiconductor interface are (2) quantum-mechanical tunneling of electrons through the barrier, (3) recombination in the space-charge region and (4) electron injection from the metal to the semiconductor under negative gate bias. Fig. 2.10 shows the transport processes in the Schottky emission under forward bias. A plot of  $\ln(J)$  versus  $\sqrt{E}$  yields a straight line where E is the electric filed and J is the current density. Meanwhile, a plot of  $\ln(J/T^2)$  versus 1/T would also show a straight line where T denotes the temperature.

Fig. 2.10 Four basic transport processes in Schottky emission. [16]

The Frenkel-Poole emission, shown in Fig. 2.11, is due to the field-enhanced thermal excitation of trapped electrons into the conduction band. For trap states with coulomb potentials, the expression is virtually identical to that of the Schottky emission. The barrier height is the depth of the trap potential well. The tunneling is caused by the field-assisted electron emission into the conduction band or by electrons tunneling from metal Fermi level into the insulator conduction band. The tunneling process is substantially

Fig. 2.11 Illustration of Frenkel-Poole emission.  $\phi_B$  is the barrier height. [17]

dependent on the applied voltage and independent of the temperature. Fowler-Nordheim tunneling occurs at a large electric field above 6-7 MV/cm. If electric field E<sub>i</sub> is further increased beyond 10~12 MV/cm, depending on the dielectric film thickness, dielectric breakdown occurs. When the thickness of dielectric films is reduced to 4~5nm, direct

tunneling becomes dominant. The tunneling processes are shown in Fig. 2.12. A simple criterion that direct tunneling occurs is that:

$$V_i \equiv E_i t < \Phi_B \tag{2.17}$$

which means that electrons go into the conduction band of silicon rather than of  $SiO_2$ .  $V_i$  is the potential across the oxide layer of thickness t.  $\Phi_B$  is the barrier potential from metal to oxide. Substituting  $\Phi_B = 3.2$  V and  $E_i = 7$  MV/cm for the onset of F-N tunneling into Eqn. 2.17, for example, we approximately find for the  $Si\text{-}SiO_2$  system that direct tunneling is dominant when the dielectric thickness is less than 4.5 nm. This agrees with the experimental observations. Due to the mechanism of direct tunneling, it has much smaller dependence on the gate voltage  $V_g$  compared to the F-N tunneling. Therefore, the current in such a low- $V_g$  range at which MOSFET's are operated in practice is undesirably increased, setting a fundamental constraint on MOS technology.

Fig. 2.12 Diagram of tunneling processes in insulating films. (a) Direct Tunneling (b) Fowler-Nordheim Tunneling

The space-charge-limited current is due to the carriers injected into the insulator, where no compensating charge is present. At low voltage and high temperature, conduction current is formed by thermally excited electrons hopping from one isolated state to the next, this leads to an ohmic characteristic exponential dependence on temperature. The ionic conduction is similar to diffusion processes. The dc ionic conduction is not obvious during the time the voltage is initially applied since ions can not be readily injected or extracted from the insulator. After the initial current flow, positive and negative space charges will build up at the metal-insulator and insulator-semiconductor interfaces, causing a distortion of the potential distribution. As the voltage is removed, large internal fields remain which cause some ions to flow back to their equilibrium position.

Intrinsic tunneling and leaky paths due to neutral trapping centers created by plasma exposure are the major leakage mechanisms in MOS devices with untrathin oxide [18]. Thin gate oxides are subjected to plasma process induced charging damage since so many plasma steps are used and plasma damage is cumulative. Plasma charging may cause electrical stress of the gate oxide that can result in reduced device yield. When charging stress is milder, interface traps are generated and the characteristics of MOS devices may exhibit a higher range of variability. Reliability of devices is also degraded. The nature of the oxide degradation under plasma charging relies on the Fowler-Nordheim (F-N) current being forced through the thin oxide layer under electrical stress. Degradation of the gate oxide leakage depends on bias polarity, temperature, and gate material such as boron or phosphor doped poly silicon gates. The Stress-Induced-Leakage-Current (SILC) in gate oxide has been studied extensively since it may impose constraints on dielectric thickness scaling. It was reported that for stress voltage below 5 V and for gate oxide thickness less than 3.5 nm, SILC is caused by tunneling via interfacial traps, rather than through bulk oxide traps [19].

## 2.4 MOSFET Transistor

MOSFET transistor is a four-terminal structure including gate, substrate, source and drain, as shown in Fig. 2.13. There are two types of transistors based on the carriers in the channel: n-type (n-channel) and p-type (p-channel). In this section, operation theory and equations of n-channel on p-type substrate are discussed. Similar results can also be applied to p-channel device with corresponding polarity modifications.

Fig. 2.13 Cross section of a MOSFET

When the gate voltage  $V_g$  is larger than the threshold voltage  $V_{th}$ , electrons in the substrate will be attracted to the semiconductor surface, forming so called n-channel underneath the gate oxide. The potential difference between source and drain will cause electrons in the n-channel to drift from source to drain therefore current flows through the channel. The threshold voltage is an important parameter for the MOSFET device. It is the minimum gate voltage needed to turn on the transistor. The threshold voltage for large-geometry devices on uniformly doped substrates with no short- or narrow-channel effects is given by

$$V_{th} = V_{FB} + 2\phi_F + \frac{\sqrt{2q\varepsilon_{Si}N_A(2\phi_F)}}{C_i}$$

(2.18)

$$\phi_F = \frac{kT}{q} \ln \left( \frac{N_A}{n_i} \right) \tag{2.19}$$

where  $V_{FB}$  is the flat band voltage, substrate and source are both grounded. The threshold voltage for non-uniformly doped, ion-implanted devices depends on the implant dose as well.  $C_i$  is the gate dielectric capacitance, which increases with the reduction of gate dielectric thickness. Additional corrections are needed for short- or narrow-channel devices. The charges that exist at interface of semiconductor and oxide will also cause a shift of the threshold voltage. In this case, the threshold voltage can be expressed as

$$V_{th} = V_{FB} + 2\phi_F + \frac{\sqrt{2q\varepsilon_{Si}N_A(2\phi_F)}}{C_i} + \frac{Q_u + Q_{ot}}{C_i}$$

(2.20)

where Q<sub>it</sub> are the interface charges and Q<sub>ot</sub> are the oxide trapped charges. The scaling of oxide thickness results in an increase of oxide capacitance. Therefore, the threshold voltage could be reduced.

As a large enough gate voltage is applied to the MOSFET device, an n-type inversion layer will be formed and electrons in this n-channel will flow from source to drain with  $V_D > 0$ . There are two cases of small and large  $V_D$  to be considered. For a small  $V_D$ , inversion layer charges are uniformly distributed under the gate oxide and current flows through the conducting channel. The channel acts as a resistor in this case so that the drain current increases proportionally to  $V_D$ . This is called linear region. As  $V_D$  is further increased, electrons in the inversion layer close to the drain end will be attracted to the drain and this region will be depleted of mobile electrons. Therefore the channel resistance will be increased until eventually the inversion layer charge becomes zero (called pinchoff) at the drain end.  $V_D$  at which saturation occurs is denoted by the saturation drain voltage  $V_{Dsat}$ . Once  $V_D$  exceeds the saturation voltage, the pinchoff point will move towards the source end leaving a depletion region behind at the surface. The drain current will eventually remain constant  $I_D$  because it depends on the voltage drop (fixed at  $V_{Dsat}$ ) inside the channel. This region is called saturation.

To derive the  $I_D$ - $V_D$  characteristics, only drift current is considered for simplicity. The mobility is assumed to be constant throughout the channel. Integrating the equation for current density J ( $v_d$ : drift velocity of the electrons) [3]

$$J = -qn(x)v_d \tag{2.21}$$

from the surface towards the point  $x = x_I$  at which the intrinsic Fermi level  $E_i$  intersects  $E_{Fn}$  gives

$$I_D = WQ_I \mu_n E_{\parallel} = -WQ_I \mu_n \partial V / \partial y \tag{2.22}$$

where  $E_{\parallel} \equiv -\partial V/\partial y$ , W is the width of the channel, and  $Q_{\rm I}$  is the inversion charge per unit area defined by

$$Q_I = -\int_{1}^{X_I} q n(x) dx \tag{2.23}$$

There are several methods to calculate the  $Q_I$  in Eqn. 2.23. Some approaches are very complicated and time-consuming. Usually a gradual-channel approximation is used  $(V_D << 2 \phi_F)$ , in this case) and a simple drain current calculation yields

$$I_D = \frac{W}{L} \mu_n C_i (V_g - V_{th} - V_d / 2) V_D$$

(2.24)

where the threshold voltage  $V_{\text{th}}$  is given by

$$V_{th} = 2\phi_F + \frac{1}{C_i} \sqrt{2\varepsilon_s q N_A \cdot 2\phi_F} = 2\phi_F + K \sqrt{\phi_t \cdot 2\phi_F}$$

(2.25)

K is a characteristic ratio of semiconductor capacitance to the gate dielectric capacitance C<sub>i</sub> defined by

$$K = \frac{\sqrt{2\varepsilon_s}}{C_i} \frac{1}{L_o} = \frac{\sqrt{2\varepsilon_s q N_A/\phi_t}}{C_i}$$

(2.26)

which includes the Debye length  $L_D$  as described in Chapter 2.1. Eqn. 2.24 reflects the drain current in the so-called linear region. In this region, for a given gate voltage  $V_g$ ,  $I_D$  first increases linearly with  $V_D$ , then gradually levels off, and reaches its maximum  $I_{Dsat}$  at  $V_{Dsat}$ . Solving  $\partial I_D/\partial V_D=0$  with Eqn. 2.24 produces

$$V_{Dsat} = V_g - V_{th} (2.27)$$

I<sub>Dsat</sub> is then obtained by substituting Eqn. 2.27 into Eqn. 2.24,

$$I_{Dsat} = \frac{W}{L} \mu_n C_i \frac{(V_g - V_{th})^2}{2}$$

(2.28)

which is used to describe  $I_D$  with  $V_D > V_{Dsat}$ . A typical  $I_D - V_D$  curve is shown in Fig. 2.14.

Fig. 2.14 Idealized saturation characteristics ( $I_D$  vs.  $V_D$ ) of an n-channel MOSFET .The dashed line indicates the locus of  $I_{Dsat}$  vs.  $V_{Dsat}$ .

[3]

According to the drain current expression in the linear region,  $I_D$  should be zero for  $V_g < V_{th}$ . This is because when the drain current was explored, only drift current was considered. In reality, there will be a current flow in the channel even gate voltage is

smaller than the threshold voltage. Unlike the drift current in the strong inversion, the subthreshold current  $I_D$  in weak inversion is dominated by diffusion due to the difference between the electron density at the source and drain. This current is especially important for low-voltage, low-power applications such as CMOS logic and DRAM memory devices.

## 2.5 Scaling issues and limitations