# Algebraic Specification and Verification of Processor Microarchitectures

John Robert Matthews B.S., University of Washington, 1990

A dissertation submitted to the faculty of the

Oregon Graduate Institute of Science and Technology

in partial fulfillment of the

requirements for the degree

Doctor of Philosophy

in Computer Science and Engineering

October 2000

© Copyright 2000 by John Robert Matthews All Rights Reserved

The dissertation "Algebraic Specification and Verification of Processor Microarchitectures" by John Robert Matthews has been examined and approved by the following **Examination Committee:**

John Launchbury

Professor

Thesis Research Adviser

Dick Kieburtz Professor

Dylan McNamee Assistant Professor

Mary Sheeran Professor Chalmers University of Technology

# Dedication

To Julie and my parents.

# Acknowledgements

I would like to thank my advisor, John Launchbury, for helping me to become a researcher. John has been an excellent teacher and a major source of inspiration in this work. He has given me just the right balance of direction, freedom, and encouragement. Thank you John.

This work was funded by grants from the Air Force Material Command and Intel Corporation, as well as a graduate research fellowship from the National Science Foundation. These endowments helped me to pursue my own research agenda, for which I am grateful. I was also funded by internships at Intel and Microsoft Research (Cambridge), where I gained insight into the pragmatic goals and concerns of industrial verification. I would like to thank Borislav Agapiev and Carl Seger of Intel, as well as Don Syme and Andrew Gordon of Microsoft in giving me these internship opportunities and guidance. I would in addition like to thank the many people at Intel and Microsoft who patiently answered my wide-ranging questions, including Mark Aagaard, Luca Cardelli, Oege de Moor, Robert Jones, Tom Melham, John O'Leary, and Simon Peyton Jones.

I greatly enjoyed my time at the Oregon Graduate Institute, as well as the stimulating discussions and encouragement I received from the members of the PacSoft and Hawk research groups. I spent some exceptional years here.

Byron Cook, Nancy Day, Jeff Lewis, and Thomas Nordin put a lot of time and effort into developing aspects of the Hawk system, which I happily made use of. I fondly remember long talks on aspects of Hawk formalization with Byron Cook, Nancy Day, Sava Krstić and Mark Shields. Their knowledge and insight have improved my thesis.

I would also like to thank the other members of my thesis committee, Dick Kieburtz, Dylan McNamee, and Mary Sheeran, and librarian Julianne Williams for their excellent comments and discussions. I apologize now for any remaining omissions or errors.

I am indebted to my parents Bob Matthews, Elizabeth and Michael O'Connell, and my brother Michael Matthews for the love and encouragement they have shown me for as long as I can remember.

Finally, I would like to thank Julie, the love of my life, for being at my side all of these years, even when I couldn't always be at hers. Thank you for helping me through it all.

# Contents

| D | Dedication       iv         Acknowledgements       v |        |                                                    |  |  |

|---|------------------------------------------------------|--------|----------------------------------------------------|--|--|

| A |                                                      |        |                                                    |  |  |

| A | bstra                                                | ct     |                                                    |  |  |

| 1 | Intr                                                 | oducti | on                                                 |  |  |

|   | 1.1                                                  | Hardw  | are description languages                          |  |  |

|   |                                                      | 1.1.1  | Goals of the Hawk language                         |  |  |

|   | 1.2                                                  | Thesis | statement                                          |  |  |

|   | 1.3                                                  | Synop  | sis                                                |  |  |

| 2 | Inti                                                 | oducti | on to Hawk                                         |  |  |

|   | 2.1                                                  |        | awk library                                        |  |  |

|   |                                                      | 2.1.1  | Signals                                            |  |  |

|   |                                                      | 2.1.2  | Components                                         |  |  |

|   |                                                      | 2.1.3  | Using the components                               |  |  |

|   |                                                      | 2.1.4  | Recursive definitions                              |  |  |

|   |                                                      | 2.1.5  | Other embedded Haskell languages                   |  |  |

|   | 2.2                                                  | A sim  | ple microprocessor                                 |  |  |

|   |                                                      | 2.2.1  | Unpipelined SHAM specification                     |  |  |

|   |                                                      | 2.2.2  | Pipelining                                         |  |  |

|   |                                                      | 2.2.3  | Transactions                                       |  |  |

|   |                                                      | 2.2.4  | Transaction structure                              |  |  |

|   |                                                      | 2.2.5  | Changes to handle transactions                     |  |  |

|   |                                                      | 2.2.6  | Unpipelined SHAM                                   |  |  |

|   |                                                      | 2.2.7  | SHAM2 with transactions                            |  |  |

|   |                                                      | 2.2.8  | Hazards                                            |  |  |

|   |                                                      | 2.2.9  | Hawk specification of extended SHAM                |  |  |

|   |                                                      | 2.2.10 | Extending transactions to other microarchitectures |  |  |

|   |                                                      | 2.2.11 | Transactions in other modeling languages           |  |  |

|   |                                                      |        |                                                    |  |  |

|   | 2.3  | Modeli  | ng the DLX                                   |

|---|------|---------|----------------------------------------------|

|   |      | 2.3.1   | Executing the model                          |

|   | 2.4  | Other l | nardware modeling languages                  |

| 3 | Mic  | roarchi | tecture algebra                              |

|   | 3.1  | Introdu | action                                       |

|   | 3.2  | Referen | nce microarchitecture                        |

|   | 3.3  | Algebra | aic reasoning and the microarchitecture laws |

|   |      | 3.3.1   | Algebraic reasoning                          |

|   |      | 3.3.2   | Delay laws                                   |

|   |      | 3.3.3   | Bypasses and bypass laws                     |

|   |      | 3.3.4   | Projection laws                              |

|   | 3.4  | Transfo | orming the microarchitecture                 |

|   |      | 3.4.1   | Retiming stage                               |

|   |      | 3.4.2   | Move control wires stage                     |

|   |      | 3.4.3   | Propagate hazard information stage           |

|   |      | 3.4.4   | Remove forwarding logic stage                |

|   |      | 3.4.5   | Cleanup stage                                |

|   |      | 3.4.6   | Final pipeline                               |

|   |      | 3.4.7   | Verifying the final microarchitecture        |

| 4 | Fori | malizin | g Hawk in higher order logic                 |

|   | 4.1  | Elemen  | ts of higher order logic                     |

|   |      | 4.1.1   | Terms                                        |

|   |      | 4.1.2   | Types and type operators                     |

|   |      | 4.1.3   | Primitive constants                          |

|   |      | 4.1.4   | Defined constants                            |

|   |      | 4.1.5   | Inference rules and proofs                   |

|   |      | 4.1.6   | Type definitions                             |

|   |      |         | Datatypes                                    |

|   | 4.2  | The Isa | abelle theorem prover                        |

|   |      | 4.2.1   | Certifying proofs in Isabelle                |

|   |      | 4.2.2   | Higher level tactics                         |

|   | 4.3  | Embed   | ding Hawk                                    |

|   | 4.4  | Modeli  | ng recursive definitions                     |

|   |      | 4.4.1   | Axiomatic definitions                        |

|   |      | 4.4.2   | Well-founded recursion                       |

|   |      | 4.4.3   | Coinductive types and corecursive functions  |

|   |      |         |                                              |

|   | 4.5               | Defining recursive functions as fixed points                       |

|---|-------------------|--------------------------------------------------------------------|

|   |                   | 4.5.1 Unique fixed points                                          |

|   |                   | 4.5.2 Properties of unique fixed points                            |

| • | Con               | verging equivalence relations                                      |

|   | 5.1               | Definition                                                         |

|   | 5.2               | Examples                                                           |

|   |                   | 5.2.1 Discrete CER                                                 |

|   |                   | 5.2.2 Lazy list CER                                                |

|   | 5.3               | Contracting functions and the CER fixpoint theorem                 |

|   | 5.4               | Recursive definitions over coinductive lists                       |

|   |                   | 5.4.1 Defining <i>iterates</i>                                     |

|   | 5.5               | Composing converging equivalence relations                         |

|   |                   | 5.5.1 Defining recursive functions with the function-space CER 106 |

|   |                   | 5.5.2 Other CER combinators                                        |

|   | 5.6               | Demonstrating equality between coinductive elements                |

|   | 5.7               | Defining functions with unbounded look-ahead                       |

|   | 5.8               | Generalizing well-founded recursion                                |

|   | 5.9               | Proof of the CER fixpoint theorem                                  |

|   |                   | 5.9.1 Outline                                                      |

|   |                   | 5.9.2 Converging approximation maps                                |

|   |                   | 5.9.3 Properties of <i>apx</i>                                     |

|   | 5.10              | Applying CERs to Hawk circuits                                     |

|   |                   | Related work                                                       |

| , | Veri              | fying the microarchitecture laws                                   |

|   | 6.1               | A theory of transactions                                           |

|   | 0.1               | 6.1.1 Transaction as an abstract datatype                          |

|   |                   | 6.1.2 Transaction laws                                             |

|   |                   | 6.1.3 Derived transaction operators                                |

|   | 6.2               | Exploiting symmetry in transaction fields                          |

|   | 0.2               | 6.2.1 First class field names                                      |

|   |                   | 6.2.2 Generalized field laws                                       |

|   | 6.3               | Lifting the transaction theory to signals                          |

|   |                   | Proof of alu time-invariance for nop                               |

|   | n 4               | 1 1001 01 data villio invariance for 100p                          |

|   | 6.4<br>6.5        | Temporal reasoning 149                                             |

|   | 6.4<br>6.5<br>6.6 | Temporal reasoning                                                 |

|          |        | 6.6.2  | Converging equivalence relations for signals      |

|----------|--------|--------|---------------------------------------------------|

|          |        | 6.6.3  | Properties of envs component                      |

|          |        | 6.6.4  | Definition and properties of fvEnvs component     |

|          |        | 6.6.5  | Definition and properties of bypass component     |

|          |        | 6.6.6  | Proof of the microarchitecture law                |

| 7        | Ret    | rospec | ${f tive}$                                        |

|          | 7.1    | The fi | nctional basis of Hawk                            |

|          |        | 7.1.1  | Structured datatypes                              |

|          |        | 7.1.2  | Lazy evaluation                                   |

|          |        | 7.1.3  | Higher order functions                            |

|          |        | 7.1.4  | Static typing and polymorphism                    |

|          |        | 7.1.5  | Nondeterminism                                    |

|          | 7.2    | Transa | actions                                           |

|          |        | 7.2.1  | Verifying pipelines with transactions             |

|          |        | 7.2.2  | Calculating space efficient pipelines             |

|          | 7.3    | Algeb  | raic reasoning                                    |

|          |        | 7.3.1  | Proving the component laws                        |

|          |        | 7.3.2  | Simplifying the pipeline                          |

|          | 7.4    | Conve  | rging equivalence relations                       |

|          | 7.5    | Mecha  | unizing the verification                          |

|          |        | 7.5.1  | Mechanizing the microarchitecture law proofs      |

|          |        | 7.5.2  | Mechanizing the top level pipeline simplification |

|          | 7.6    | Concl  | usions and further research directions            |

| Bi       | ibliog | graphy |                                                   |

| <b>.</b> |        | nhianl | Note 100                                          |

| _ ⊔ ≀    | ~~~~   | mhianl | Note                                              |

# List of Tables

| 4.1 | The primitive constants of HOL         | 79 |

|-----|----------------------------------------|----|

| 4.2 | Some derived constants in Isabelle HOL | 79 |

# List of Figures

| 2.1  | Resettable Counter. A simple circuit that counts the number of clock cycles |    |

|------|-----------------------------------------------------------------------------|----|

|      | between reset signals                                                       | 11 |

| 2.2  | Unpipelined version of SHAM                                                 | 17 |

| 2.3  | Pipelined SHAM. Since the register file and the ALU each now take one       |    |

|      | clock cycle to complete, we now need extra Delay circuits. The Delay        |    |

|      | circuits in turn require us to add Select circuits to act as bypasses. The  |    |

|      | logic controlling the Select circuits is not shown                          | 20 |

| 2.4  | A transaction as it flows through the pipeline. As the transaction pro-     |    |

|      | gresses, its operands become more refined                                   | 24 |

| 2.5  | bypass circuit                                                              | 27 |

| 2.6  | Block diagram of extended SHAM pipeline. Each Pipeline Register circuit     |    |

|      | is made up of multiple Delay and Select circuits. The Select circuits are   |    |

|      | used for bypassing, ensuring that the source operands are up-to-date        | 29 |

| 0.1  |                                                                             |    |

| 3.1  | One-stage pipeline.                                                         | 41 |

| 3.2  | Hawk code for reference microarchitecture                                   |    |

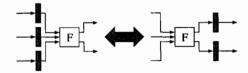

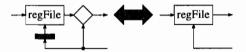

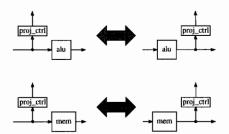

| 3.3  | Universal circuit-duplication law                                           |    |

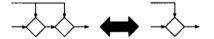

| 3.4  | feedback rotation law                                                       | 45 |

| 3.5  | time-invariance law.                                                        | 45 |

| 3.6  | bypass circuit idempotence law                                              | 46 |

| 3.7  | register-bypass law                                                         | 46 |

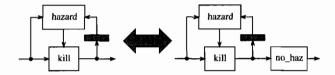

| 3.8  | hazard-bypass law                                                           | 47 |

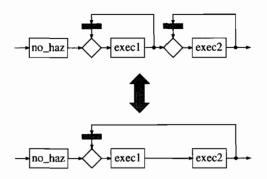

| 3.9  | Hazard-squashing logic guarantees no hazards                                | 48 |

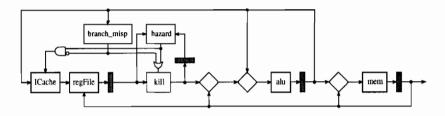

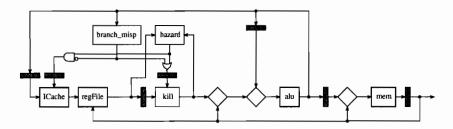

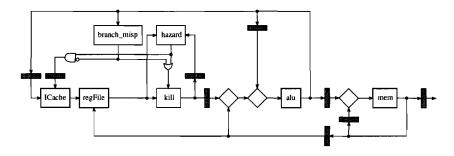

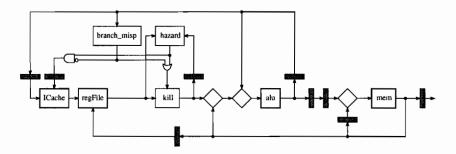

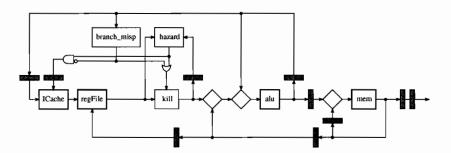

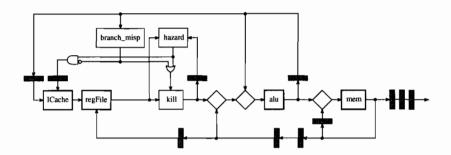

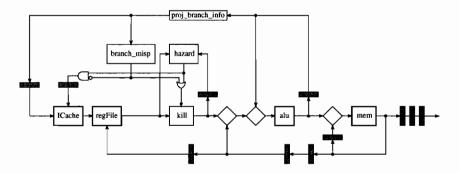

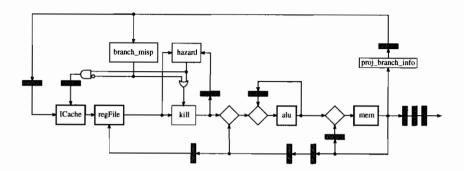

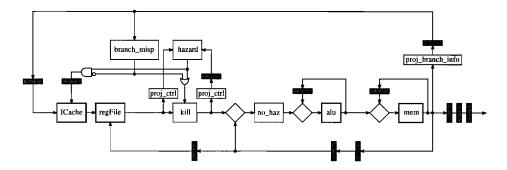

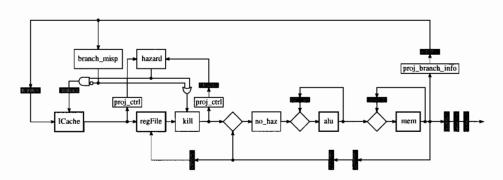

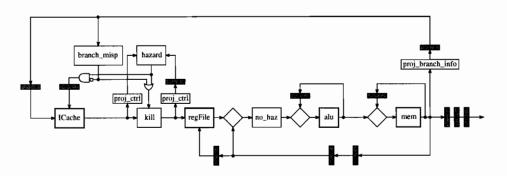

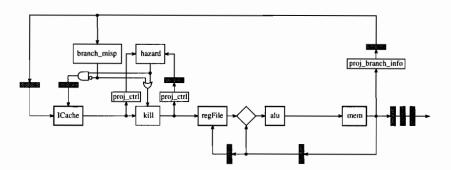

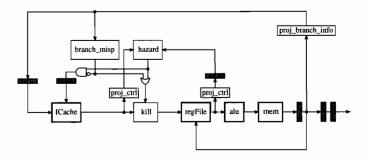

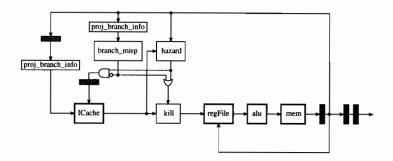

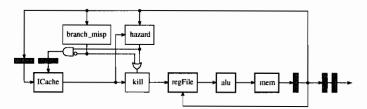

| 3.10 | Microarchitecture before simplification                                     | 50 |

| 3.11 | Split delay circuit after regFile, using the circuit duplication law        | 51 |

| 3.12 | Split delay circuit after alu, using the feedback-rotation law              | 51 |

| 3.13 | Split twice the delay circuit leading to branch_misp and iCache, using two  |    |

|      | applications of the circuit-duplication law                                 | 52 |

| 3.14 | Move delay circuits through the branch_misp and hazard circuits, using      |    |

|      | the corresponding time-invariance laws                                      | 52 |

|      |                                                                             |    |

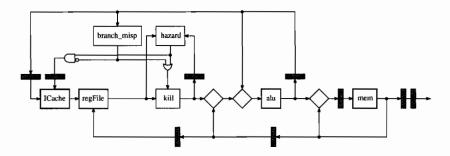

| 3.15 | Move delay circuits through the or and and circuits, using the circuit-<br>duplication law and the corresponding time-invariance laws | 52 |

|------|---------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.16 | Move delay circuits through the kill circuit, using the corresponding time-                                                           |    |

|      |                                                                                                                                       | 53 |

| 3.17 | Split the delay circuit after the kill circuit, using the circuit duplication                                                         |    |

|      | law                                                                                                                                   | 53 |

| 3.18 | Split the delay circuit after the mem circuit, using the feedback rotation law                                                        | 53 |

| 3.19 | Split the bottom-most delay circuit, using the circuit duplication law                                                                | 54 |

| 3.20 | Split the bottom-most delay circuit again, using the circuit duplication law                                                          | 54 |

| 3.21 | Move the delay circuit before the first bypass circuit through the first and                                                          |    |

|      | second bypasses, using the corresponding time-invariance laws                                                                         | 54 |

| 3.22 | Move the delay circuit through the alu circuit using the corresponding                                                                |    |

|      | time-invariance law                                                                                                                   | 55 |

| 3.23 | Split the delay circuit after the alu circuit using the feedback-rotation law                                                         | 55 |

| 3.24 | Move the delay circuit through the third bypass circuit using the corre-                                                              |    |

|      | sponding time-invariance law                                                                                                          | 55 |

| 3.25 | Move the delay circuit through the mem circuit using the corresponding                                                                |    |

|      | time-invariance law                                                                                                                   | 56 |

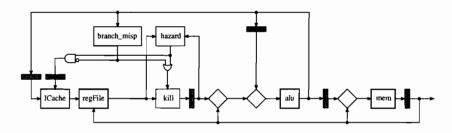

| 3.26 | Split the delay circuit after the mem circuit, using the corresponding feedback-                                                      |    |

|      | rotation law                                                                                                                          | 56 |

| 3.27 | Split the delay circuit below the mem circuit, using the corresponding circuit                                                        |    |

|      | duplication law                                                                                                                       | 56 |

| 3.28 | Move the delay circuit through the last bypass circuit, using the corre-                                                              |    |

|      | sponding time-invariance law                                                                                                          | 57 |

| 3.29 | Move the delay circuit through the mem circuit, using the corresponding                                                               |    |

|      | time-invariance law                                                                                                                   | 57 |

|      | Split the delay circuit after the mem circuit, using the feedback-rotation law                                                        | 57 |

|      | Split the bottom-rightmost delay circuit, using the circuit duplication law.                                                          | 58 |

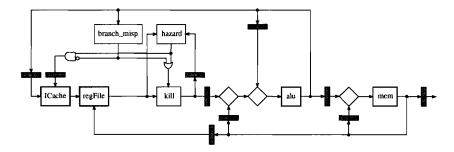

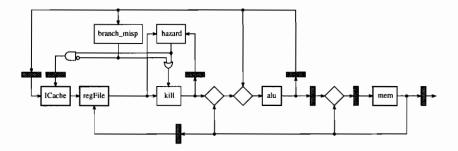

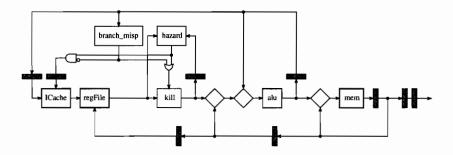

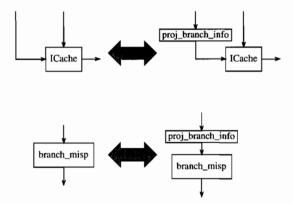

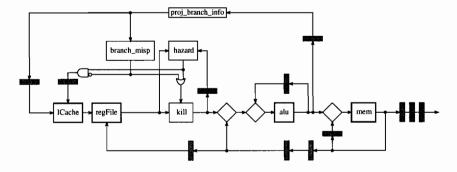

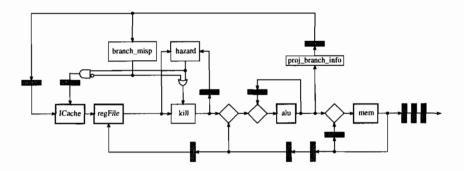

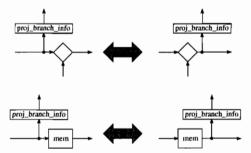

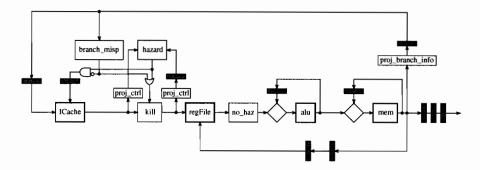

|      | Projection insertion laws for proj_branch_info                                                                                        | 58 |

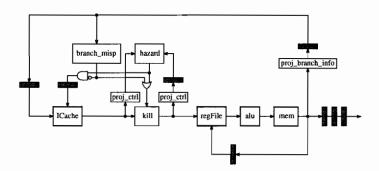

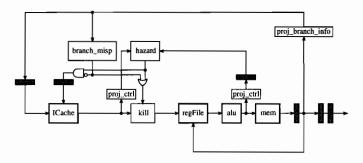

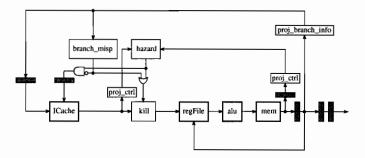

| 3.33 | Insert proj_branch_info projection on the inputs to iCache and branch_misp,                                                           |    |

|      | using the corresponding projection laws from Figure 3.32                                                                              | 59 |

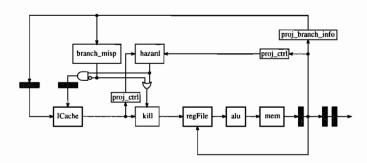

| 3.34 | Move proj_branch_info past the left-most delay, using the corresponding                                                               |    |

|      | time-invariance law                                                                                                                   | 59 |

| 3.35 | Merge the two instances of proj_branch_info, using the circuit duplication                                                            | 00 |

| 0.00 | law in reverse                                                                                                                        | 60 |

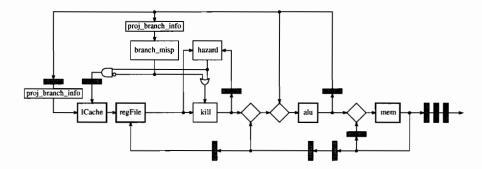

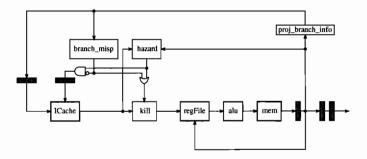

| 3.36 | Split the delay circuit ahead of proj_branch_info                                                                                     | bί |

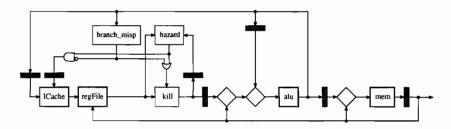

| 3.37 | Move the proj_branch_info circuit past the delay circuit using the corre-               |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | sponding time-invariance law                                                            | 61 |

| 3.38 | Projection-invariance laws for proj_branch_info                                         | 61 |

| 3.39 | Move proj_branch_info past the third bypass and mem circuit, using the                  |    |

|      | projection invariance laws from Figure 3.38                                             | 62 |

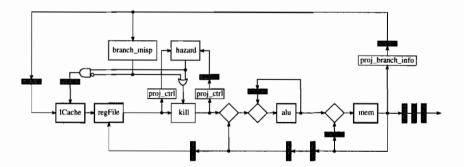

| 3.40 | <pre>proj_ctrl projection insertion law</pre>                                           | 62 |

| 3.41 | Add proj_ctrl projections to the inputs of the hazard circuit using the cor-            |    |

|      | responding projection-insertion laws (Figure 3.40), and move the right-most             |    |

|      | <pre>proj_ctrl circuit past the delay using the corresponding time-invariance law</pre> | 62 |

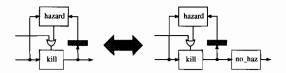

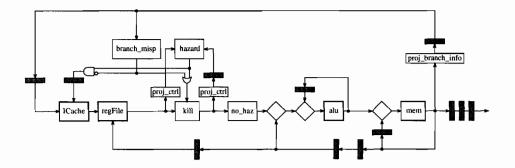

| 3.42 | Generalized no_haz projection insertion law                                             | 63 |

| 3.43 | Insert a no_haz projection after the kill circuit, using the projection in-             |    |

|      | sertion law shown in Figure 3.42                                                        | 63 |

| 3.44 | Commute no_haz with the first bypass, using the corresponding projection                |    |

|      | commutativity law (we also reroute the mem stage feedback wire)                         | 64 |

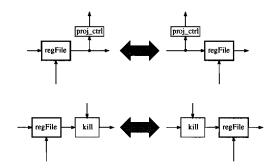

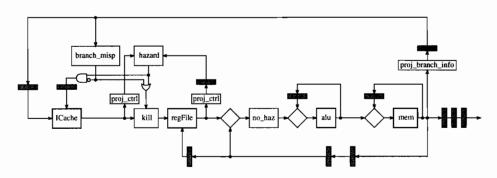

| 3.45 | register file commutativity laws                                                        | 64 |

| 3.46 | Commute the first projectr1 projection with the register file, using the                |    |

|      | first law of Figure 3.45                                                                | 65 |

| 3.47 | Commute the register file with the kill circuit, using the second law of                |    |

|      | Figure 3.45                                                                             | 65 |

| 3.48 | Commute the second projectr1 projection with the register file, using the               |    |

|      | first law of Figure 3.45                                                                | 65 |

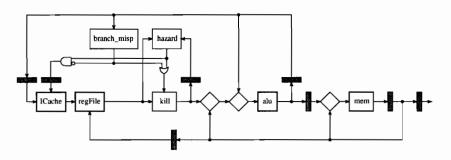

| 3.49 | Use the register-bypass law to remove the left-most bypass and the delay                |    |

|      | circuit below it                                                                        | 66 |

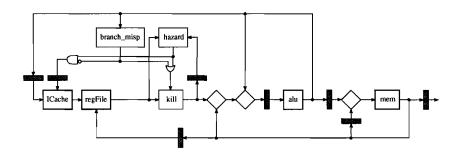

| 3.50 | Remove the right-most bypass circuit using the hazard-bypass law                        | 66 |

| 3.51 | register file commutes with hazard projection                                           | 66 |

| 3.52 | Swap the register file with no_haz, using the commutativity law in Figure 3.51 $$       | 67 |

| 3.53 | Remove no_haz, using the no_haz projection insertion law (Figure 3.42) in               |    |

|      | reverse                                                                                 | 67 |

| 3.54 | Merge the delay feeding into the remaining bypass circuit with the right-               |    |

|      | bottom-most delay, using the circuit-duplication law in reverse                         | 67 |

| 3.55 | Remove the last bypass circuit, using the register-bypass law                           | 68 |

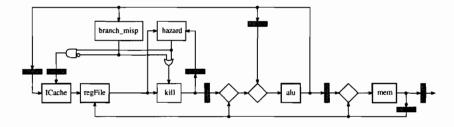

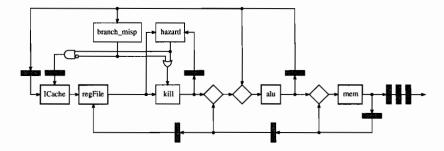

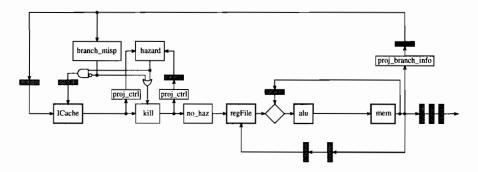

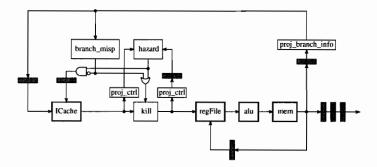

| 3.56 | Swap the proj_branch_info projection with the delay next to it, using the               |    |

|      | corresponding time-invariance law                                                       | 68 |

| 3.57 | Merge the three forking delay circuits after the mem circuit, using the feed-           |    |

|      | back rotation law in reverse                                                            | 69 |

| 3.58 | More proj_ctrl projection invariance laws                                               | 69 |

|      |                                                                                         |    |

| 3.59 | Move the right-most proj_ctrl circuit past the register file, using the first               |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | law of Figure 3.45                                                                          | 69  |

| 3.60 | Move the right-most proj_ctrl circuit past the alu, using the first law in                  |     |

|      | Figure 3.58                                                                                 | 70  |

| 3.61 | Move the right-most proj_ctrl circuit past the mem, using the second law                    |     |

|      |                                                                                             | 70  |

| 3.62 | Swap the right-most proj_ctrl circuit with the delay, using the corre-                      |     |

|      | 1 0                                                                                         | 70  |

| 3.63 | Merge the delay after the mem unit with the delay below the right-most                      |     |

|      | , ,                                                                                         | 71  |

| 3.64 | Remove proj_ctrl circuits, using the projection insertion law of Figure 3.42                |     |

|      |                                                                                             | 71  |

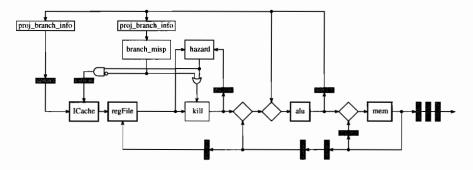

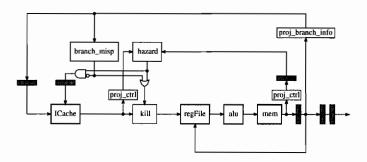

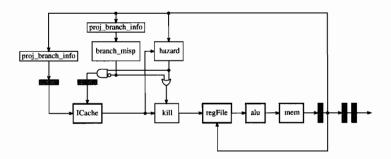

| 3.65 | Split the proj_branch_info projection, using the circuit duplication law                    | 71  |

| 3.66 | Swap the left-most proj_branch_info projection with the delay circuit                       |     |

|      | below it, using the corresponding time-invariance law                                       | 72  |

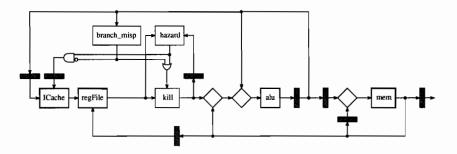

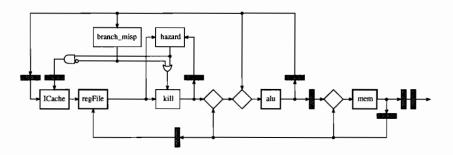

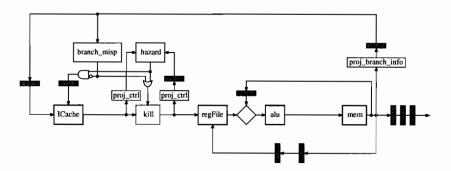

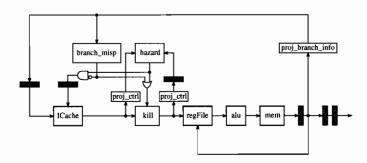

| 3.67 | The final pipeline, after removing the proj_branch_info projections using                   |     |

|      | the projection insertion laws of figure 3.32 in reverse                                     | 72  |

| 4.1  | Inference rules specific to higher order logic. $^{\dagger}(abs)$ holds if x is not free in |     |

|      | the assumptions. $(\alpha conv)$ holds if y is not free in a. $(ext)$ holds if x is         |     |

|      |                                                                                             | 80  |

|      |                                                                                             |     |

| 5.1  | The CER axioms. Each of these axioms must hold for arbitrary $i, x, y$ ,                    |     |

|      | and $f$                                                                                     | 100 |

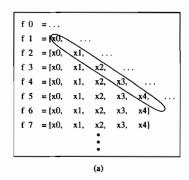

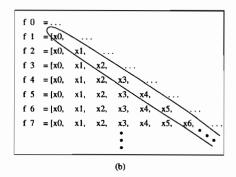

| 5.2  | The $llist\_diag$ function constructs a limit list from an approximation map.               |     |

|      | In (a) the approximation map converges to a finite list; In (b) to an infinite              |     |

|      | list                                                                                        | 102 |

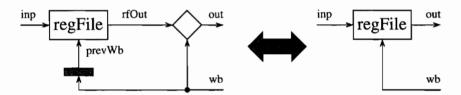

| 7.1  | register file - bypass law                                                                  | 174 |

|      | <del>-</del>                                                                                |     |

## Abstract

### Algebraic Specification and Verification of Processor Microarchitectures

John Robert Matthews

Ph.D., Oregon Graduate Institute of Science and Technology

August, 2000

Thesis Advisor: Dr. John Launchbury

The Hawk language is a domain-specific extension of the pure functional language Haskell, and is used to specify and reason about processor microarchitectures at a high level of abstraction. We apply functional language technology and reasoning principles to concisely specify pipelined microarchitectures in Hawk and verify them through a domain-specific microarchitecture algebra. We develop a remarkably simple set of local equational laws governing processor components such as register files, bypass logic, and execution units. Many of these laws are verified in Isabelle, a higher order logic theorem prover. The laws are used to incrementally simplify a complex pipelined microarchitecture, removing pipeline stages and simplifying control logic, while retaining cycle-accurate behavior with respect to the original pipelined design.

Proving these laws requires defining mutually recursive functions over coinductively defined streams. Such definitions are not directly supported in current theorem provers. We develop a generalization of well-founded recursion, called *Converging Equivalence Relations*, that allows these definitions to be added conservatively in a straightforward and modular fashion.

# Chapter 1

# Introduction

Modern processor microarchitectures can be incredibly complex. Although exact figures are kept secret, it can safely be said that leading manufacturers employ dozens if not hundreds of design and verification engineers for each new generation of processor. As semiconductor process improvements continue to deliver an exponentially increasing budget of transistors, processor architects are able to employ ever more sophisticated implementation techniques to increase the amount of useful work performed per clock cycle. Some standard examples of performance increasing optimizations are:

- **Pipelining.** Analogous to automobile assembly lines, operations that take more than one clock cycle to complete are often divided into stages. Each stage completes its work in one clock cycle. By connecting the stages with pipeline registers, multiple instances of complex operations can be processed per clock cycle.

- Superscalar execution. Multiple instructions are fetched per clock cycle. Duplicated execution units such as ALUs execute the fetched instructions concurrently.

- Caching. Long-latency communication between the processor and main memory is minimized by storing past results in local caches for faster access.

- Out-of-order execution. Fetched instructions are dynamically analyzed to determine which instructions are independent of each other. Independent instructions are executed according to when a compatible execution unit is available, even though this may cause the operations to be performed in a different order than specified by the program.

• Speculation. The results of time-consuming operations are opportunistically predicted. The processor uses the predicted result immediately, and simultaneously starts computing the real result of the operation. The processor then checks whether the prediction is correct once the operation completes. If the prediction is confirmed, the processor has saved time by parallelizing the operation. If the prediction is incorrect, the processor rolls back its internal state and then uses the correct result.

Not only does each of these techniques incur a substantial amount of design complexity, cutting edge processor designs combine them to achieve further speedups. In fact, creating and verifying these designs is a significant proportion of the total microprocessor development lifecycle. As the number of possible gates in future microprocessors increases exponentially, so too does design complexity.

It is now common for a commercial microprocessor design effort to take two years or more, as engineers resolve all of the possible interactions between microarchitectural features while trying to meet performance, area, power, and heat dissipation goals.

Resolving all of these issues while trying to complete the project as quickly as possible almost always results in design defects, some of which may slip through testing efforts and end up in released products. Of course, similar defects routinely occur with large commercial software products. But whereas software faults can be easily fixed by downloading patches through the internet, a microprocessor defect may require the entire device to be replaced. These mistakes can become exceedingly expensive, both financially and in lowered customer confidence. Such mistakes have also become more widely publicized in recent years, as personal computers are increasingly sold to mass consumer markets.

# 1.1 Hardware description languages

One way to gain intellectual control over design complexity is to employ a formal modeling language. Such a language can provide several benefits. For example, Ashenden[4] notes that assuming the language has appropriate supporting tools, an architect can:

Describe and understand the required behavior and attributes of a system unambiguously.

- Communicate these requirements to others precisely.

- Test the system by simulating it.

- Formally verify the system with respect to desired properties.

- Automatically synthesize implementations from the description.

Of course, most description languages are not designed to support all of the above activities, at least initially. For example, the VHDL hardware description language[4] has a large set of language features for specifying circuits behaviorally. A user can simulate any behavioral VHDL description, but must describe circuits using a strict subset of these features to automatically synthesize a circuit implementation. On the other hand, low-level languages designed to describe circuits at the gate and transistor level are harder to simulate efficiently.

In practice, a design engineer will typically work with multiple specification languages during a processor development lifecycle. In the early stages, the designer is more concerned with functional correctness and the performance tradeoffs between alternative microarchitectural features at the granularity of individual clock cycles. Thus the design engineer is likely to use a high-level behavioral specification language, such as behavioral VHDL, or even C. As the overall design is solidified, lower level structural considerations, such as size and layout constraints, power consumption budgets, and sub-clock-cycle timing issues often encourage or require the engineer to develop circuit designs that can be directly synthesized and analyzed at the gate or transistor level.

#### 1.1.1 Goals of the Hawk language

At the Oregon Graduate Institute we have been interested in developing high-level domain specific programming languages based on structuring principles derived from typed functional programming languages. In particular, the *Hawk* project has been developing a behavioral specification language for processor microarchitectures. Our goal is to build a language that lets architects specify designs at a higher level of abstraction than can be done with current behavioral hardware specification languages. To achieve this we

intend to use language features that promote concision, modularity, and reusability in specifications.

- Concision. Just as a program written in a higher level language such as C is easier

for humans to understand and modify than the same program written in assembly

language, so too do microarchitectures become more comprehensible as specifications

are made more concise and abstract. Ideally we would like our specification language

to be as concise as the high-level block diagrams that architects currently use to

express microarchitectures.

- Modularity. Given the number of people required to design modern processor

microarchitectures, it is essential to be able to decompose a large specification into

separate units, with well-defined interfaces between them. In this way individual

architects can concentrate on a portion of the overall microarchitecture, without

having to understand the entire design in full detail.

- Reusability. Once a specification language has the ability to separate design elements into modular units, a natural next step is to try to reuse commonly occuring design units by defining them once and then referring to the definition at each point of use. By eliminating redundant definitions, the overall size of the specification is reduced, and defects caused by creating incompatible versions of the same design element are prevented.

However, we don't want our specification language to be so abstract that it is not executable. To gain confidence in a design's correctness and evaluate performance tradeoffs an architect may need to simulate a microarchitecture on a wide variety of programs. It is not uncommon for a microprocessor simulator to execute billions of instructions on a given design.

In addition to concrete simulation, we would also like to simulate microarchitectures in Hawk symbolically. A symbolic simulator allows the user to execute a design with some of the inputs given as symbolic variables (or more generally expressions), rather than as concrete values. The simulator then executes the design with the symbolic inputs and returns the result as a symbolic expression. In this way a single symbolic test run can replace a whole family of concrete test runs. A good introduction to symbolic simulation techniques for processors is given by Moore[67], who uses the ACL2 theorem prover to symbolically simulate a small processor at the instruction set architecture level. Symbolic simulation can sometimes detect errors simply because the returned expression "looks strange", i.e. is much larger or more complex than what was expected. This strategy was used by Greve[31] to detect microcode errors in a direct execution Java processor. Day, Lewis, and Cook[19] have developed a version of Hawk that supports symbolic simulation and have used it to symbolically simulate the data flow of a superscalar out-of-order microarchitecture.

To gain even more confidence in the correctness of a Hawk specification an architect should be able to turn to formal verification, where a mathematical proof demonstrates that a design satisfies desired correctness properties on all possible inputs. Since the design being verified can be quite large, this approach only becomes practical when the proof is carried out with the help of automated tools, such as model checkers and theorem provers. Constructing proofs requires formalizing both the design and the underlying specification language in some mathematical logic, such as set theory or higher order logic. This is not a trivial endeavor, and specification languages with complex or ill-defined semantics can substantially increase the amount of human and machine time necessary to complete the proof.

#### 1.2 Thesis statement

Hawk was created as a typed functional programming language in order to provide a good balance between abstraction and expressiveness, executability, and ease of formal reasoning. In particular, this dissertation aims to show that:

The concepts underlying lazy functional programming languages, particularly Haskell

and its Hawk extensions, allow one to specify microarchitectures concisely, modularly, and reusably, while retaining the ability to simulate them on concrete test

cases.

- Using equational reasoning principles, one can develop a microarchitecture algebra, whose laws enjoy the same degree of concision, modularity, and reusability as the microarchitecture specification.

- Such algebraic laws can be used to verify the correctness of pipelined microarchitectures.

- The Hawk specification language can be naturally formalized in higher order logic, and thus verification steps can be checked by a theorem prover.

This thesis can be thought of as a case study supporting a larger agenda: To demonstrate that the equational reasoning principles underlying lazy functional languages, and specifically the Haskell programming language, provide a good foundation for developing domain-specific algebras. The hope is that such algebras increase one's understanding of the domains, and can be used to formally verify desired properties of specifications.

### 1.3 Synopsis

Part of the content of this thesis is made up of re-edited and expanded versions of three published papers and a technical report, all written primarily by this author. These papers introduce Hawk as a specification language[55], describe how algebraic reasoning can be used to simplify and verify pipelined microarchitectures[53, 54], and show how to define recursive functions, such as Hawk circuits, over coinductive types[52].

Accordingly, we begin the dissertation by introducing Hawk as a microarchitecture specification language embedded within Haskell. We then state equational laws that hold of microarchitectural components, such as register files and ALUs, and use them to incrementally simplify a pipelined microarchitecture. Finally, we formalize a subset of Hawk in higher order logic and prove a representative set of these microarchitecture laws, using a combination of equational reasoning and induction over time.

The definition of mutually recursive functions over infinite streams is the most challenging aspect of Hawk's formalization, since such definitions are not directly supported in current theorem provers. We develop a generalization of well-founded recursion, called Converging Equivalence Relations, that allows these definitions to be added conservatively in a straightforward and modular fashion.

The remaining chapters of this thesis are as follows:

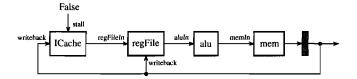

#### Chapter II: Introduction to Hawk

This chapter introduces Hawk as a specification language. We introduce a simple pipelined microarchitecture and specify it first in Hawk at the register transfer level (RTL) and then with *transactions*, an abstract datatype for representing the complete microarchitectural state associated with an instruction. We show that the language features of Hawk combined with transactions as a structuring principle lead to a concise and understandable specification.

#### Chapter III: Microarchitecture algebra

Next, we informally introduce our algebra of microarchitectural components by describing the components that comprise a more complex reference architecture than the one introduced in Chapter 2. We describe how these components are modeled in Hawk and state the laws that hold among them.

Several of the laws contain *projection* circuits. Projections are not used in either the pipelined or the reference microarchitectures, but are instead artifacts of the verification process. We motivate the usefulness of projections, and describe the conditions under which they can appear in microarchitecture laws.

Once the necessary laws have been introduced, we show how they can be used to simplify the pipelined microarchitecture. This simplification is presented graphically.

#### Chapter IV: Formalizing Hawk in higher order logic

In this chapter we introduce Higher Order Logic (HOL) and the *Isabelle* theorem prover briefly and informally. We use HOL to formalize Hawk and the microarchitecture algebra, and Isabelle to check the proofs. Since Hawk is a purely applicative functional language, many aspects of the language can be modeled directly in higher order logic itself. However, dealing with recursive Hawk definitions is more difficult. The standard semantics for

Hawk is domain theoretic, with recursive definitions modeled by least fixpoints. Although Isabelle has an object logic (HOLCF) that provides some support for reasoning about domains, there is much more support for "pure" HOL. For example, there is no syntactic support in HOLCF for pattern-matching function definitions or pointed numeric domains. We thus focus on techniques for modeling Hawk directly in HOL.

There is no natural "information order" among elements in pure HOL, and so there is no notion of a least fixpoint. However, it turns out that well-formed recursive Hawk definitions have unique fixpoints, and can therefore be uniquely defined using Hilbert's choice operator. It is a well known result of topology that unique fixpoints can be found for contracting functions in complete metric spaces. Intuitively, a metric space is a set of elements and an associated distance metric over pairs of elements. The distance metric returns a real-valued number indicating how far apart the two elements are. A contracting function over this metric space, when applied to each of a pair of elements, returns a corresponding pair of elements that is "closer" to each other than the original elements are. Banach's theorem states that contracting functions do in fact have unique fixpoints.

It is possible to define suitable distance metrics for Hawk streams, and show that recursive Hawk definitions over these streams are contracting functions. However, this often requires reasoning about division and exponentiation over real-valued domains, which relatively few theorem provers support well. Instead we adopt a different approach.

#### Chapter V: Converging equivalence relations

We develop an alternative framework, called *Converging Equivalence Relations* (CERs), for proving the uniqueness of fixpoint definitions. We develop analogs of metric spaces and contracting functions that do not require the use of continuous mathematics. Instead, reasoning proceeds by well-founded induction over discrete domains such as the natural numbers, which are well supported by all of the HOL-based theorem provers.

This chapter describes CERs with proofs of the key results. We demonstrate that this technique can be mostly automated by Isabelle's higher-order tableau proof package.

#### Chapter VI: Verifying the microarchitecture laws

In this chapter we develop some techniques to simplify the proofs of the individual laws of Chapter 3, and use them to verify representative examples. We first develop a simple theory of transactions, and make the somewhat surprising observation that although the type system of Hawk is very useful in catching errors when constructing Hawk specifications, it can be annoyingly restrictive when verifying laws about transaction fields. The statements of these theorems quantify over all of the fields in a transaction, which violates the HOL restriction that all quantifiers must range over elements of the same type. We develop a mechanism of first class field names to overcome this difficulty.

We use a combination of inductive reasoning over time and first class field names to prove two representative microarchitecture laws: a commutativity law between ALU and delay components, and a law that allows one to remove bypass circuits connected to register files.

#### Chapter VII: Retrospective

We conclude by analyzing the strengths and weaknesses of Hawk we encountered during the course of the dissertation. In particular, we discuss the relative merits of the functional basis of Hawk, the use of transactions, and the value of algebraic reasoning in the context of the Isabelle theorem prover.

We also discuss the usefulness of defining functions by converging equivalence relations, compared to defining them co-recursively. The CER framework provides a general method of defining recursive functions over a wide range of types, including coinductively defined types such as infinite lists and trees. The dissertation concludes by outlining future research directions.

# Chapter 2

# Introduction to Hawk

The *Hawk* language is designed for building executable specifications of processor microarchitectures. Currently Hawk is an embedded language (i.e. a set of libraries) within Haskell, a strongly-typed functional language with powerful abstraction capabilities, such as lazy (demand-driven) evaluation, first-class functions, and parametric polymorphism [35] [76].

### 2.1 The Hawk library

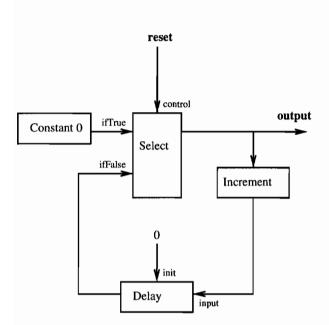

We start with a simple example that introduces several functions used in later examples. Consider the resettable counter circuit of Figure 2.1.

The *reset* wire is Boolean valued, while the other wires are integer valued. Of course, in silicon, integer-valued wires are represented by a vector of Boolean wires, but as a design abstraction, a Hawk user may choose to use a single wire. The circuit counts (and outputs) the number of clock cycles since *reset* was last asserted.

#### 2.1.1 Signals

Notice that there is no explicit clock in the diagram. Rather, each wire in the diagram carries a *signal* (integer or boolean valued) which is an implicitly clocked value. The output of a circuit only changes between clock cycles. We build signals using an abstract type constructor called Signal. As a mental model we could think of a value of type Signal a as a function from non-negative integers to values of type a, as is often done in the hardware verification community[62, 92].

Figure 2.1: Resettable Counter. A simple circuit that counts the number of clock cycles between reset signals.

#### type Signal a = (Int -> a)

We can sample a signal s at a given clock cycle n simply by evaluating s applied to n. Alternatively a signal could be thought of as an infinite stream of values  $\langle x_0, x_1, x_2, \ldots \rangle$ . Clearly the two views are interchangeable. In either case circuits are represented as functions from signals to signals.

In the resettable counter example above, the constant  $\theta$  circuit outputs zero on every clock cycle. The select component chooses between its inputs on each clock cycle depending on the value of reset. If reset is asserted on a given cycle (has value true), then the output is equal to select's top input, in this case zero. If reset is not asserted, then its output is the value of its bottom input. In either case, select's output is the output of the entire circuit, as well as the input to the increment component, which simply adds 1 to its input. The output of increment is fed into the delay component. A delay component outputs whatever was on its input in the previous clock cycle: it "delays" its input by one cycle (delay circuits occur often enough that we draw them specially, as shaded horizontal or

<sup>&</sup>lt;sup>1</sup>Function application in Hawk is written using juxtaposition, so that f applied to x and y is written as f x y

vertical bars). However, on the first clock cycle of the simulation there is no previous input, so on the first cycle *delay* outputs whatever is on its *init* input, which is zero in this circuit.

#### 2.1.2 Components

The components used in the resettable counter are trivial examples of the sorts of things provided by the Hawk library, but let's look at a specification of each component in turn.

The simplest component is constant

```

constant :: a -> Signal a

```

The constant function takes an input of any type a, and returns an output of type Signal a, that is, a sequence of values of type a. For every clock cycle, (constant x) always has the same value x. Functions such as constant that can operate over more than one type are called *polymorphic*.

The next component is select:

```

select :: Signal Bool -> Signal a -> Signal a -> Signal a

```

This declares select to be a function. In a Hawk declaration, anything to the left of an arrow is an argument to a function. Thus, the expression (select bs xs ys), where bs is a Boolean signal, and xs and ys are signals of type a, will return an output signal of type a. The values of the output signal are drawn from xs and ys, decided each clock tick by the corresponding value of bs. For example, if

```

bs = <True,False,True,False,...>,

xs = <x1,x2,x3,x4,...>,

ys = <y1,y2,y3,y4,...>

then (select bs xs ys) is equal to the signal <x1,y2,x3,y4,...>.

```

Hawk treats functions as first-class values, allowing them to be passed as arguments to other functions or returned as results. First-class functions allow us to specify a generic lift primitive, which "lifts" a normal function from type a to type b into a function over the corresponding signal types:

```

lift :: (a -> b) -> Signal a -> Signal b

```

The expression (lift f xs), where xs =  $\langle x1, x2, x3, \ldots \rangle$ , is equal to the signal  $\langle f x1, f x2, f x3, \ldots \rangle$ .

The increment component is defined in terms of lift:

```

increment :: Signal Int -> Signal Int

increment xs = lift (+ 1) xs

```

Given the xs input signal, increment adds one to each component of xs and returns the result.

The delay component is more interesting:

```

delay :: a -> Signal a -> Signal a

```

This function takes an initial value of type a, and an input signal of type Signal a, and returns a value of type Signal a (the input arguments are in reverse order from the diagram). At clock cycle zero, the expression (delay initVal xs) returns initVal. Otherwise the expression returns whatever value xs had at the previous clock cycle. This function can thus propagate values from one clock cycle to the next.

#### 2.1.3 Using the components

Once we have defined primitive signal components like the ones above, we can define the resettable counter:

```

resetCounter :: Signal Bool -> Signal Int

resetCounter reset = output

where next = delay 0 (increment output)

output = select reset (constant 0) next

```

The resetCounter definition takes reset as a Boolean signal, and returns an integer signal. The reset signal is passed into select. On every clock cycle where reset returns True, select outputs 0, otherwise it outputs the result of the next signal. On the first clock cycle next outputs 0, and thereafter outputs the result of whatever (increment output) was on the previous clock cycle. The output of the whole circuit is the output of the select function, here called output. Notice that output is used twice in this

function: once as the input to increment, and once as the result of the entire function. This corresponds to the fact that the output wire in Figure 1 is split and used in two places. Whenever a wire is duplicated in this fashion, we must use a where statement in Hawk to name the wire.

#### 2.1.4 Recursive definitions

There is something else curious about the output variable. It is being used recursively in the same place it is being defined! Most languages only allow such recursion for functions with explicit arguments. In Hawk, one can also recursion to define data-structures and functions with implicit arguments, such as the one above.

If we didn't have this ability, we would have had to define resetCounter as follows:

```

resetCounter reset = output

where next t = (delay 0 (increment output)) t

output t = (select reset (constant 0) next) t

```

Every time we have a cycle in a circuit, we would have to create a local recursive function, passing an explicit time parameter. This breaks the abstraction of the Signal ADT. In fact, in the real implementation of signals, we don't use functions at all. We use infinite lists instead. Each element of the list corresponds to a value at a particular clock cycle; the first list element corresponds to the first clock cycle, the second element to the second clock cycle, and so on. By storing signals as lazy lists, we compute a signal value at a given clock cycle only once, no matter how many times it is subsequently accessed.

Haskell allows recursive definitions of abstract data structures because it is a lazy language, that is, it only computes a part of a data structure when some client code demands its value. It is lazy evaluation that allows Haskell to simulate infinite data structures, such as infinite lists.

#### 2.1.5 Other embedded Haskell languages

#### Hardware domains

The Hawk team is not the first to take advantage of Haskell as a platform for embedding domain specific languages, or even languages for modeling hardware. For example,

O'Donnell[70] has developed a Haskell library called Hydra that models hardware gates at several levels of abstraction, ranging from implementations of gates using CMOS and NMOS pass-transistors, up to abstract gate representations using lazy lists to denote time-varying values. Hydra has been used to teach advanced undergraduate courses on computer design, in which students use Hydra eventually to design and test a simple microprocessor. Hydra is similar to Hawk in many ways, including the use of higher-order functions and lazy lists to model signals. However, Hydra does not allow users to define more structured signal types, such as signals of integers or signals of transactions. In Hydra, these composite types have to be built up as tuples or lists of Boolean signals. While this limitation does not cause problems in an introductory computer architecture course, structured signal types significantly reduce specification complexity for more realistic microprocessor specifications.

More recently, the Lava hardware description language has been designed. It also models gate and word level hardware circuits within Haskell. The original version of Lava[9] modeled circuits with a special monadic syntax, however a later version[14] defines circuits using standard Haskell expression form, in the same manner as Hawk. Modern Lava has many other similarities to Hawk: Both model signals as first class entities, use polymorphism and higher-order functions to model generic wiring patterns, and model circuits with feedback as recursively-defined signals. Lava is discussed in more detail in Section 2.4.

MHDL[6] is a hardware description language for describing analog microwave circuits, and includes an interface to VHDL. Though it tackles a very different part of the hardware design spectrum, like Hawk, MHDL is essentially an extended version of Haskell, although it is not technically an embedded language. The MHDL extensions have to do with physical units on numbers, and universal variables to track frequency and time etc.

#### Other domain specific languages

Haskell has successfully been used to specify other domains. For example, Haskell compared favorably in an experiment comparing several prototyping languages[34]. The application domain involved modeling the *Geometric Region Server* module, which tracks

the regions surrounding ships and planes in a military theatre. The module is required to answer such questions as when an enemy plane will enter a friendly ship's weapons range, or whether a plane has entered a commercial airspace corridor. Experts in each of several languages including Haskell, C++, Awk, and Griffin wrote a prototype program based on the same requirements document. The Haskell solution was considered the most concise and understandable of all the submitted entries. The authors claim their major success factors were: their heavy use of higher-order functions, Haskell's simple syntax, and the availability of powerful list-manipulating primitives in the standard Haskell library.

Fran[23] is a Haskell library that models interactive multimedia animations. The authors provide ADTs for time-varying behaviors, events, and interactions between behaviors and events. Unlike Hawk, Fran's model of time is continuous. Also, a Fran function can examine the values of future events, while Hawk signals only depend on current and past signal values. This non-monotonicity of time in Fran requires a more sophisticated time-interval analysis than is required for Hawk.

### 2.2 A simple microprocessor

In the microarchitecture domain, the Hawk libraries make essential use of Haskell's features. As a test of Hawk's capabilities, the Hawk team has specified and simulated several versions of the DLX microprocessor described in Hennessy and Patterson's widely used textbook[33]. The Hawk team chose to model the DLX because it is well known, and has excellent tool support. Several DLX simulators exist, as well as a version of the Gnu C compiler that generates DLX assembly instructions. The processor includes the most common instructions found in commercial RISC processors.

The DLX architecture is too complex to explain in fine detail in an introductory chapter. Instead, for pedagogical purposes we show how to specify a simple microprocessor called SHAM (Simple HAwk Microprocessor). We begin with the simplest possible SHAM architecture (unpipelined), and then add features: pipelining, and a memory-cache. A corresponding annotated Hawk specification of the DLX itself can be found at the Hawk web page [44].

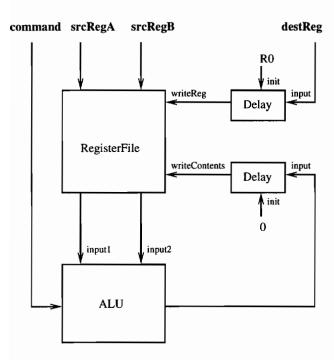

Figure 2.2: Unpipelined version of SHAM.

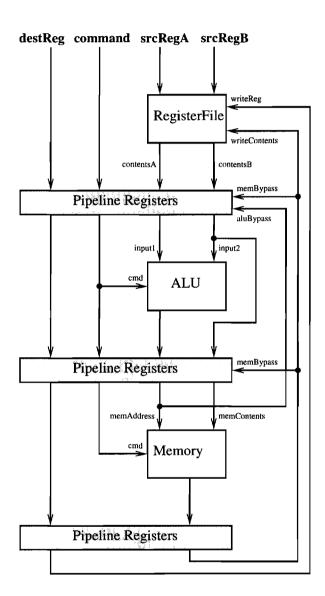

The unpipelined SHAM diagram is shown in Figure 2.2. The microprocessor consists of an ALU and a register file. The ALU recognizes three operations: ADD, SUB, and INC. The ADD and SUB operations add and subtract, respectively, the contents of the two ALU inputs. The INC operation causes the ALU to increment its first input by one and output the result. The register file contains eight integer registers, numbered RO through R7. Register RO is hardwired to the value zero, so writes to RO have no effect. The register file has one write-port and two read-ports. The write-port is a pair of wires; the register to update, called writeReg, and the value being written, called writeContents. The input to each read-port is a wire carrying a register name. The contents of the named read-port registers are output every cycle along the wires contentsA and contentsB. If a register is written to and read from during the same clock cycle, the newly written value is reflected in the read-port's output, at least abstractly. This is consistent with the behavior of most modern microprocessor register files.

SHAM instructions are provided externally; in our drive for simplicity there is no notion of a program counter. Each instruction consists of an ALU operation, the destination register name, and the two source register names. For each instruction the contents of the two source registers are loaded into the ALU's inputs, and the ALU's result is written back into the destination register.

#### 2.2.1 Unpipelined SHAM specification

Let us assume we have already specified the register file and ALU, with the signatures below:

The regFile specification takes two read-port inputs, a write-port input, and returns the corresponding read-port outputs. The alu specification takes a command signal and two input signals, and returns a result signal. Given these signatures and the previous definition of delay, it is easy in Hawk to specify an unpipelined version of SHAM:

The definition of sham1 takes a tuple of signals representing the stream of instructions, and returns a pair of signals representing the sequence of register assignments generated by the instructions. The first three lines in the body of sham1 read the source register values from the register file and perform the ALU operation. The next two lines delay the

destination register name and ALU output, in effect returning the values of the previous clock cycle. The delayed signals become the write-port for the register file. It is necessary to delay the write-port since modifications to the register file logically take effect for the next instruction, not the current one.

#### 2.2.2 Pipelining

Suppose we wanted to increase SHAM's performance by doubling the clock frequency. We will assume that, while sham1 could perform both the register file and ALU operations within one clock cycle, with the increased frequency it will take two clock cycles to perform both functions serially. We use pipelining to increase the overall performance. While the ALU is working on instruction n, the register file will be writing the result of instruction n-1 back into the appropriate register, and simultaneously reading the source registers of instruction n+1.

But now consider a sequence of instructions such as:

R2 <- R1 ADD R3

R4 <- R2 SUB R5

When the ADD instruction is in the ALU stage, the SUB instruction is in the register-fetch stage. But one of the registers that is being fetched (R2), has not been written back into the register file yet, because the ALU is still calculating the result. The SUB instruction will read an out-of-date value for R2. This is an example of a data hazard, where naive pipelining can produce a result different from the unpipelined version of a microprocessor. To resolve this hazard, we will first add bypass logic to the pipeline. Later we will abstract away from this added complexity.

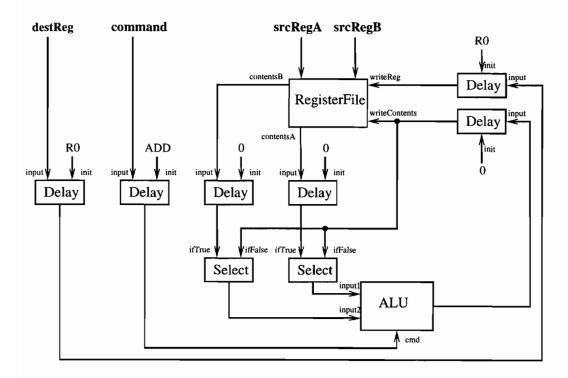

Figure 2.3 contains the diagram of a pipelined version of SHAM with bypass logic. By the time the source operands to the SUB instruction (R2 and R5) are ready to be input into the ALU, the up-to-date value for R2 is stored in the delay circuit between the ALU and the register file's write-port. The bypass logic uses this stored value of R2 as the input to the ALU, rather than the out-of-date value read from the register file. The bypass logic examines the incoming instructions to determine when this is necessary. The following code contains the Hawk specification:

Figure 2.3: Pipelined SHAM. Since the register file and the ALU each now take one clock cycle to complete, we now need extra *Delay* circuits. The *Delay* circuits in turn require us to add *Select* circuits to act as bypasses. The logic controlling the *Select* circuits is not shown.

```

sham2 :: (Signal Cmd, Signal Reg, Signal Reg, Signal Reg) -> (Signal Reg, Signal Int)

sham2 (cmd,destReg,srcRegA,srcRegB) = (destReg'',aluOut')

where

(valueA,valueB) = regFile srcRegA srcRegB (destReg'',aluOut')

valueA'

= delay 0 valueA

valueB'

= delay 0 valueB

= delay RO destReg

destReg'

= delay ADD cmd

cmd'

aluInputA = select validA valueA' aluOut'

aluInputB = select validB valueB' aluOut'

alu0ut

= alu cmd' aluInputA aluInputB

aluOut'

= delay 0 aluOut

destReg'' = delay RO destReg'

--- Control logic ---

= delay True (noHazard srcRegA)

validA

validB

= delay True (noHazard srcRegB)

noHazard :: Signal Reg -> Signal Bool

noHazard srcReg = sigOr (sigEqual destReg' (constant RO))

(sigNotEqual destReg' srcReg)

```

The data flow portion of the code is grouped according to pipeline stages:

- The first line after the where keyword reads the contents of the source registers from the register file.

- The next four lines delay the source register contents, the ALU command, and the destination register name by one cycle.

- The two select commands decide whether the delayed values should be bypassed.

The decision is made by the Boolean signals validA and validB, which are defined in the control logic section.

- The next line performs the ALU operation.

- The last two lines in the data-flow section delay the ALU result and the destination register. The delayed result, called aluOut', is written back into the register file in the register named by destReg'', as indicated in the first two lines of the section.

The control logic section determines when to bypass the ALU inputs. The signals validA and validB are set to True whenever the corresponding ALU input is up-to-date. The definition of these signals uses the function noHazard, which tests whether the previous instruction's destination register name matches a source register name of the current instruction. If they do, then the function returns False. The exception to this is when the destination register is RO. In this case the ALU input is always up-to-date, so noHazard returns True.

### 2.2.3 Transactions

The definition of sham2 highlights a difficulty of many such specifications. Although the data flow section is relatively easy to understand, the control logic section is far from satisfactory. In fact, it often takes nearly as many lines of Hawk code to specify the control logic as it does to specify the data flow, and mistakes in the control logic may not be easy to spot. We need a more intuitive way of defining control logic sections in microprocessors.

We use a notion of transactions within Hawk to specify the state of an entire instruction as it travels through the microprocessor (similar in spirit to Aagaard and Leeser [1]). A transaction holds an instruction's source operand values, the ALU command, and the destination operand value. Transactions also record the register names associated with the source and destination operands:

```

data Transaction = Trans DestOp Cmd SrcOp SrcOp

type DestOp = Operand

type SrcOp = Operand

type Operand = (Reg, Value)

```

data Value = Unknown | Val Int

An operand is a pair containing a register and its value. Values can either be "un-known" or they can be known, e.g. Val 7.

For example, the instruction (R3 <- R2 ADD R1), when it has completed, would be encoded as shown below (assume that register R2 holds the value 3, and R1 holds 4):

```

Trans (R3, Val 7) ADD (R2, Val 3) (R1, Val 4)

```

This expression states that register R3 should be assigned the value 7 as a result of adding the contents of register R2 and R1.

Not all of the register values in a transaction are known in the early stages of the pipeline. When a register name does not have an associated value yet, it is assigned the value Unknown. For example, if the above instruction had not reached the ALU stage yet, then the corresponding transaction would be:

```

Trans (R3, Unknown) ADD (R2, (Val 3)) (R1, (Val 4))

```

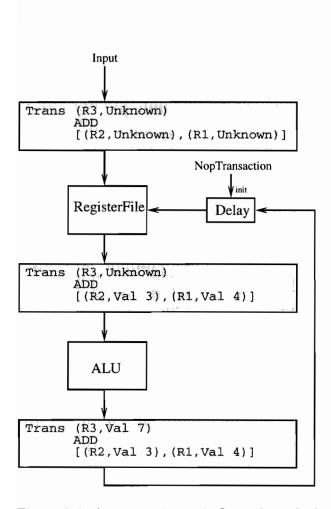

Figure 2.4 shows how a transaction's values are filled in as it flows through the pipeline.

### 2.2.4 Transaction structure

In general, the Transaction datatype contains four subfields. The first field holds the destination register name and its current state. The *state* of a register indicates the current value for the register at a given stage of the pipeline. Possible state values are Unknown, or (Val k). The second field is the instruction's ALU operation, in this case the ADD command. The third and fourth fields hold the source operand register names and their corresponding states. In this example, it holds the names and states for the source operands R2 and R1. If an instruction has less than two source operands, the extra operand fields are set to a default value of (R0, Val 0).

The instruction (R3 <- R2 ADD R1), before it enters the SHAM pipeline, is encoded as the transaction:

Trans (R3, Unknown) ADD (R2, Unknown) (R1, Unknown)

Figure 2.4: A transaction as it flows through the pipeline. As the transaction progresses, its operands become more refined.

At this point, none of the register values are known.

## 2.2.5 Changes to handle transactions

We change the regFile and alu functions so that they take and return transactions:

```

regFile :: Signal Transaction ->

Signal Transaction ->

Signal Transaction

alu :: Signal Transaction ->

Signal Transaction

```

Because the register file needs to both write new values to the CPU registers and read values from them, the regFile function takes a read transaction and a writeback

transaction as inputs. The function first examines the destination register field of the writeback transaction and updates the corresponding register in the register file. It then outputs the read transaction, modified so that all of the source register fields contain current values from the register file. For example, suppose regFile is applied to the completed write-transaction (the second source operand is not used here):

```

Trans (R1, Val 4) INC (R1, Val 3) (R0, Val 0)

and uses as its read transaction

Trans (R3, Unknown) ADD (R2, Unknown) (R1, Unknown)

```

If we further assume that register R1 is assigned 20 and R2 is assigned 3 before regFile's application, then regFile will update R1 to contain 4 from the writeback transaction, and will output a new transaction that is identical to the read transaction, except that all of the source registers have been assigned current values from the register file:

```

Trans (R3, Unknown) ADD (R2, Val 3) (R1, Val 4)

```

The revised alu function takes a transaction whose source operands have values, performs the appropriate operation, and outputs a modified transaction whose destination field has been filled in. Thus if the ADD transaction above were given to alu, it would return:

```

Trans (R3, Val 7) ADD (R2, Val 3) (R1, Val 4)

```

### 2.2.6 Unpipelined SHAM

Using transactions, the unpipelined version of SHAM is even easier to specify than it was before.

```

aluOutput' = delay nop aluOutput

nop = Trans (RO, Val O) ADD (RO, Val O) (RO, Val O)

```

But the real benefit of transactions comes from specifying more complex micro-architectures, as we shall see next.

### 2.2.7 SHAM2 with transactions

Transactions are designed to contain the necessary information for concisely specifying control logic. The control logic needs to determine when an instruction's source operand is dependent on another instruction's destination operand. To calculate the dependency, the source and destination register names must be available. The transaction carries these names for each instruction. Because of this additional information, bypass logic is easily modeled with following combinator:

```

bypass :: Signal Transaction ->

Signal Transaction ->

```

At any cycle, the bypass function usually just outputs its first argument. Sometimes, however, the second argument's destination operand name matches one or more of the first argument's source operand names. In this case, the matching source operand's state values are updated to equal the destination operand state value. The updated version of the first argument is then returned.

So if at clock cycle n the first argument to bypass is:

```

Trans (R4,Unknown) ADD (R3,Val 12) (R2,Val 4)

```

```

Trans (R3, Val 20) SUB (R8, Val 2) (R11, Val 10)

```

and the second argument at cycle n is: