# The Microstructural Effects of Metallization and Heat Treatment on Thin Gate Oxide for Use in Sub-Micron MOSFETs

John M. Mc Carthy

B.S. Physics, State University of New York at Stony Brook, 1969

M.S. Materials Science and Engineering Washington State University,1987

> A thesis submitted to the faculty of the Oregon Graduate Institute

> > of

Science & Technology in partial fulfillment of the requirements for the degree Doctor of Philosophy in Materials Science and Engineering January 1996 The dissertation "The Microstructural Effects of Metallizations and Heat Treatment on Thin Gate Oxide for Use in Sub-Micron MOSFETs" by John M. Mc Carthy has been examined and approved by the following Examination Committee:

Jack Devletian, Advisor, Professor Dr. Ken Cadien, Intel James T. Stanley, Assistant Professor Milt Scholl, Assistant Professor Lemmy Meekisho, Assistant Professor

Raj Solanki, Associate Professor

# **Dedication**

I dedicate this work to my wife Karen whose patience, support and advice helped me complete this difficult task.

### ACKNOWLEDGEMENT

Bill Wood for the opportunity to pursue a doctorate in materials science

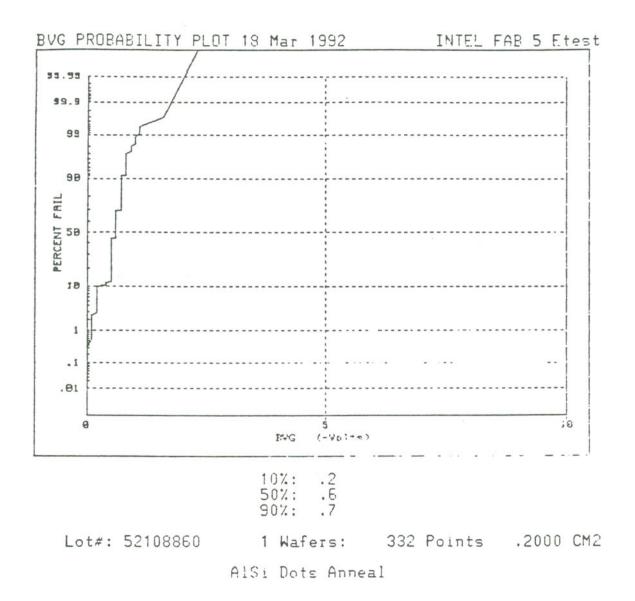

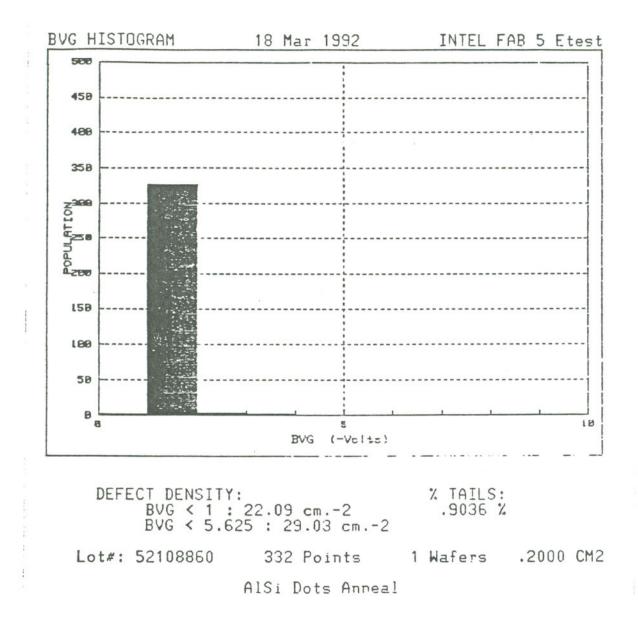

Leo Yau and his group at Intel for the electronic devices, BVG measurements, guidance and an interesting problem

Ken Cadien of Intel for his patient mentoring

Uhle Dahmen and his group at the National Center for Electron Microscopy at Berkley for the atomic resolution images of the SiO<sub>2</sub>/Si interface and planar sections of the SiO<sub>2</sub>

Jim Cser for his help with focused ion beam milling of TEM cross sections

Locke Christman of FEI Company for the FIB produced SIMS profile of the AI-.5Cu electrode

Glenn Ramirez for his micro-hardness measurements in Appendix III

# TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION                                                  | 1 |

|--------------------------------------------------------------------------|---|

| CHAPTER 2: OUTLINE OF EXPERIMENTS                                        | 5 |

| CHAPTER 3: BACKGROUND                                                    | 7 |

| The Microstructure of SiO <sub>2</sub> 10                                | ) |

| Barrier Layers                                                           | 4 |

| The Microstructure of Metallizations                                     | 6 |

| Interface Microstructures and Effects on Performance 16                  | 6 |

| The Thermodynamics of Interfacial Reactions 19                           | 9 |

| Gate Leakage Currents and Breakdown Voltage                              |   |

| Measurements 20                                                          | 0 |

| Analytical Electron Microscopy 22                                        | 2 |

| High Resolution Electron Microscopy                                      | 3 |

| Summary                                                                  | 3 |

| CHAPTER 4: EXPERIMENTAL PROCEDURES                                       | 5 |

| CHAPTER 5: RESULTS                                                       | 4 |

| SiO <sub>2</sub> /Si as Deposited 36                                     | 6 |

| SiO <sub>2</sub> /Si Heat Treated for 2hrs at 400°C in N <sub>2</sub> 39 | 9 |

| Al-1Si/SiO <sub>2</sub> /Si as Deposited 40                              | 0 |

|    | Al-1Si/SiO2/Si Heat Treated for 2hrs. at 400°C in $N_2 \hdots N_2$            | 42 |

|----|-------------------------------------------------------------------------------|----|

|    | Al-1Si/SiO <sub>2</sub> /Si, 12hrs. at 400°C in N <sub>2</sub> + Furnace Cool | 44 |

|    | Al5Cu/SiO <sub>2</sub> /Si as deposited                                       | 48 |

|    | Al5Cu/SiO <sub>2</sub> /Si, 2hrs at 400°C in N <sub>2</sub>                   | 51 |

|    | Al5Cu/SiO <sub>2</sub> /Si, 4hrs at 400°C in $N_2$                            | 54 |

|    | Al5Cu/SiO <sub>2</sub> /Si, 11.25hrs at 400°C in $N_2$                        | 63 |

|    | Cr/SiO <sub>2</sub> /Si as Deposited                                          | 66 |

|    | Cr/SiO <sub>2</sub> /Si, 2hrs at 400°C in $N_2$                               | 68 |

|    | Cr/SiO <sub>2</sub> /Si, 12hrs. at 400°C in N <sub>2</sub> + Furnace Cool     | 72 |

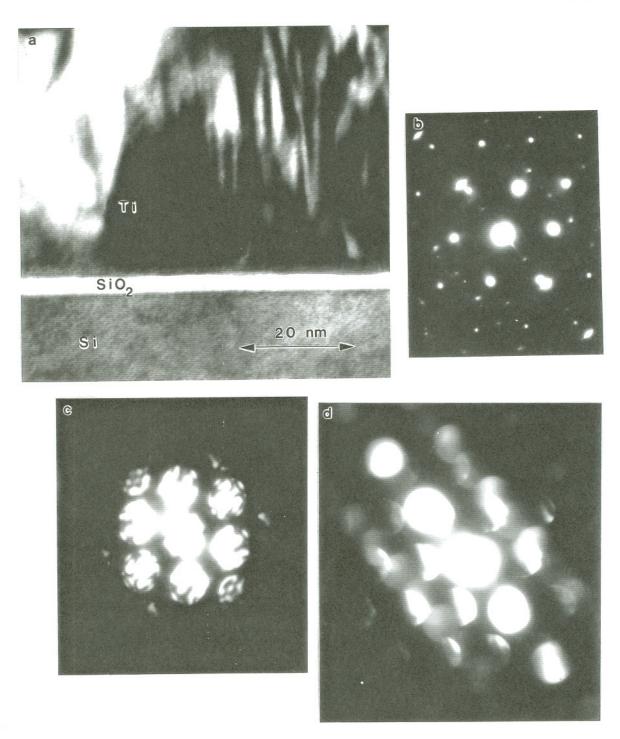

|    | Ti/SiO <sub>2</sub> /Si, as Deposited                                         | 75 |

|    | Ti/SiO <sub>2</sub> /Si, 2hrs at 400°C in N <sub>2</sub>                      | 76 |

|    | Al Deposited on 7nm TCA SiO <sub>2</sub> Electron Beam Irradiated             | 78 |

|    | W Deposited on Heat Treated SiO <sub>2</sub> Electron Beam Irradiated         | 81 |

|    |                                                                               |    |

| Cŀ | HAPTER 6: DISCUSSION                                                          | 83 |

|    |                                                                               |    |

|    | Comparison of the Al-1Si and Al5Cu Results                                    | 83 |

|    | Cr on SiO <sub>2</sub> Results                                                | 87 |

|    | Tables and Graphs of Results                                                  | 88 |

|    | Si Diffusion in the SiO <sub>2</sub> and BVG Performance                      | 07 |

|    | The Reduction of Si Diffusion into the Al5Cu Electrode 1                      | 08 |

|    | Microstructural Effects on the $\mathrm{SiO}_2$ Caused by Si Diffusion 1      | 12 |

|    | Electrode Grain Growth and BVG Performance 1                                  | 14 |

|    | The Effect of Voids, Pores and Channels on Electrodes 1                       | 19 |

|    | The Effects of Si Diffusion on the Electrodes                                 | 19 |

| Microstructural Changes in the $SiO_2$ Due to Heat Treatment . 123                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface Roughness and Heat Treatment                                                                                                             |

| Reaction Layers at the Interfaces 127                                                                                                              |

| Summary                                                                                                                                            |

| CHAPTER 7: Conclusions                                                                                                                             |

| References                                                                                                                                         |

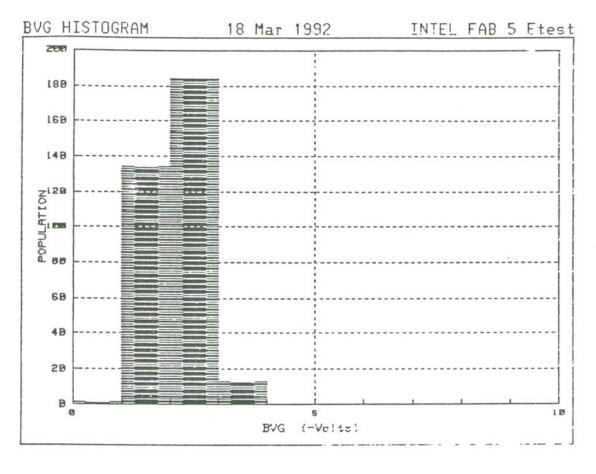

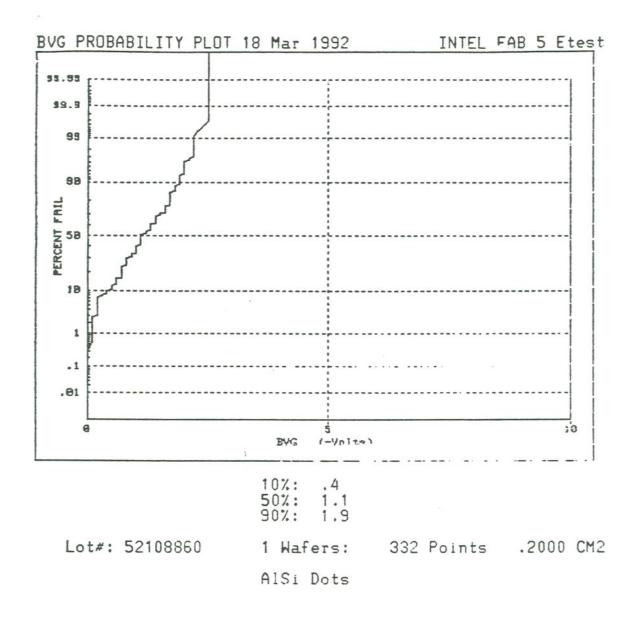

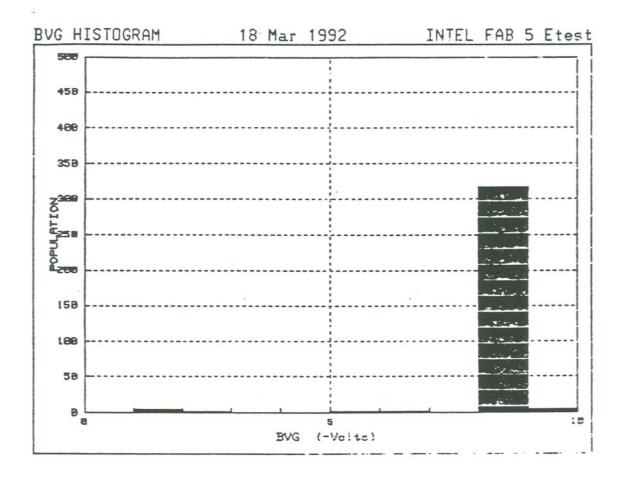

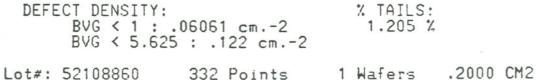

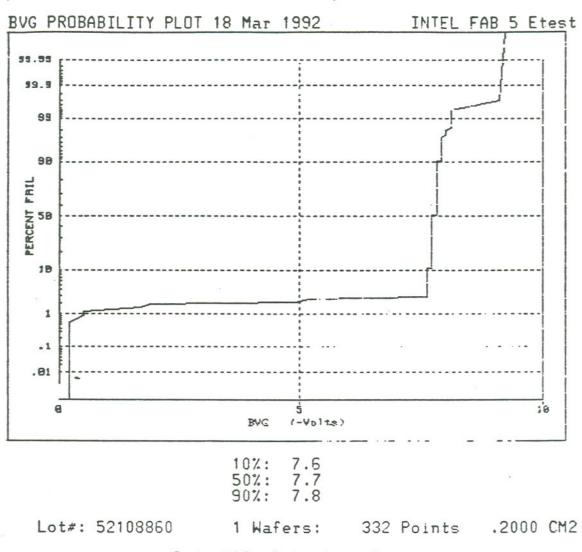

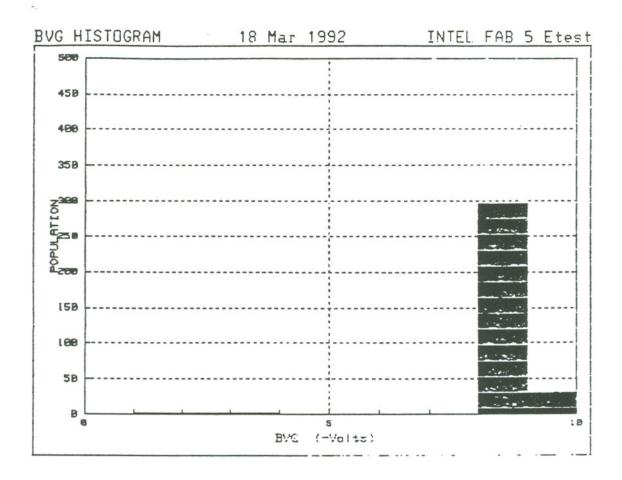

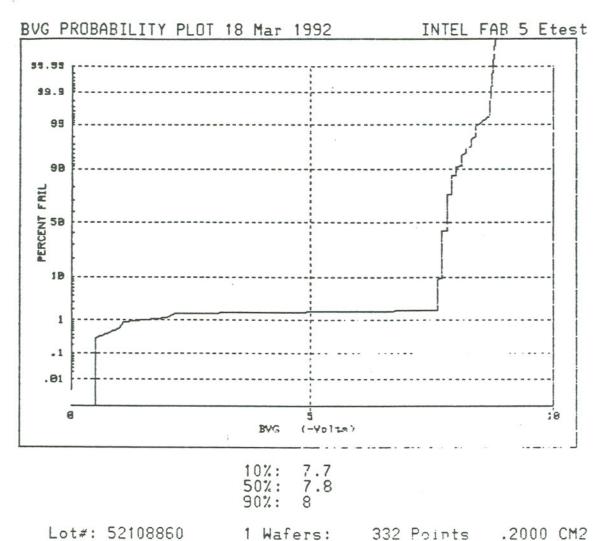

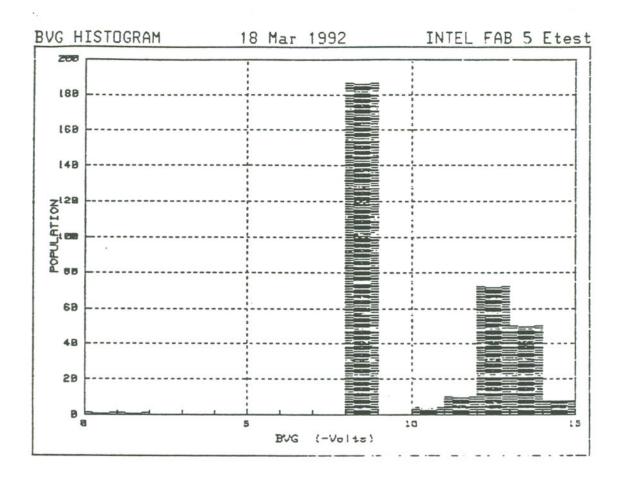

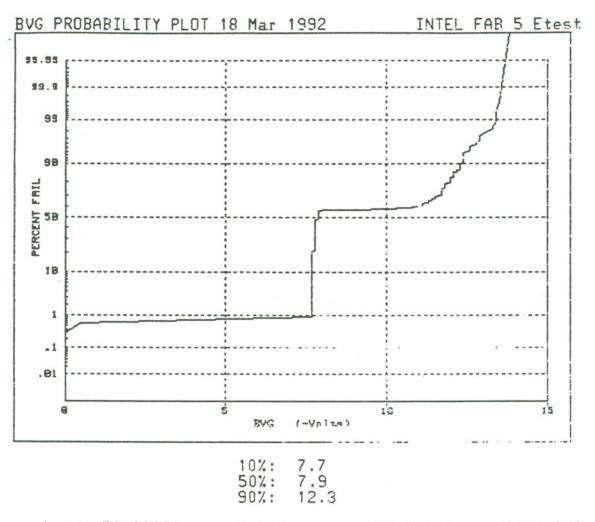

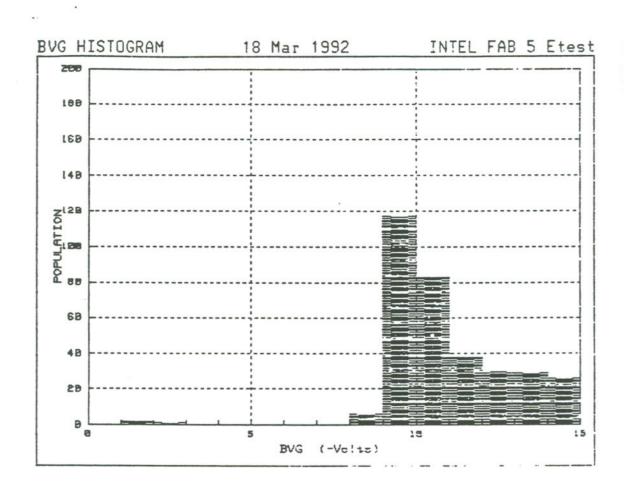

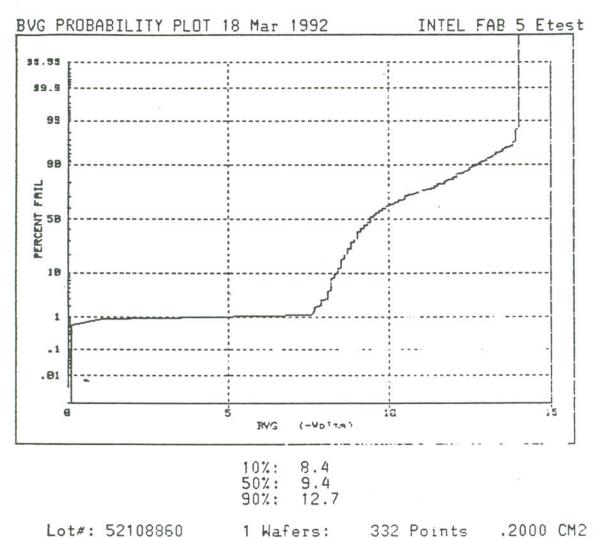

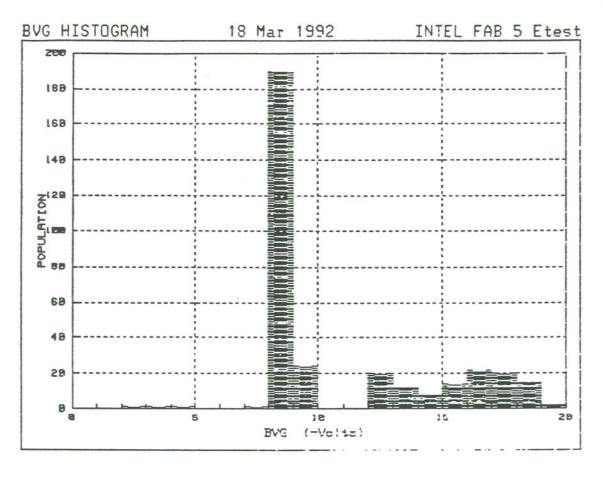

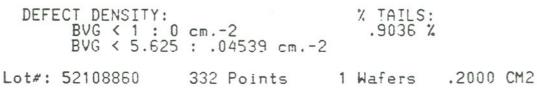

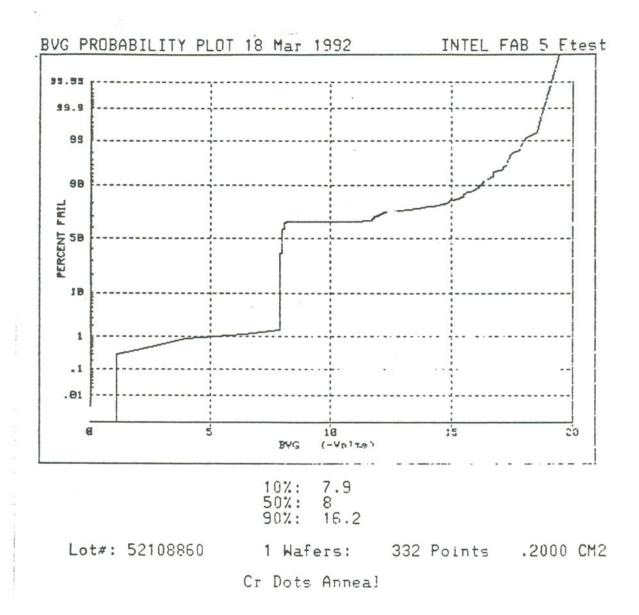

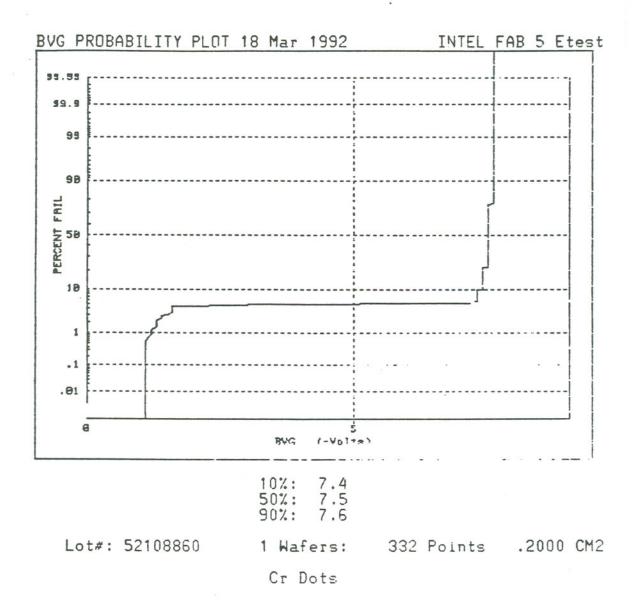

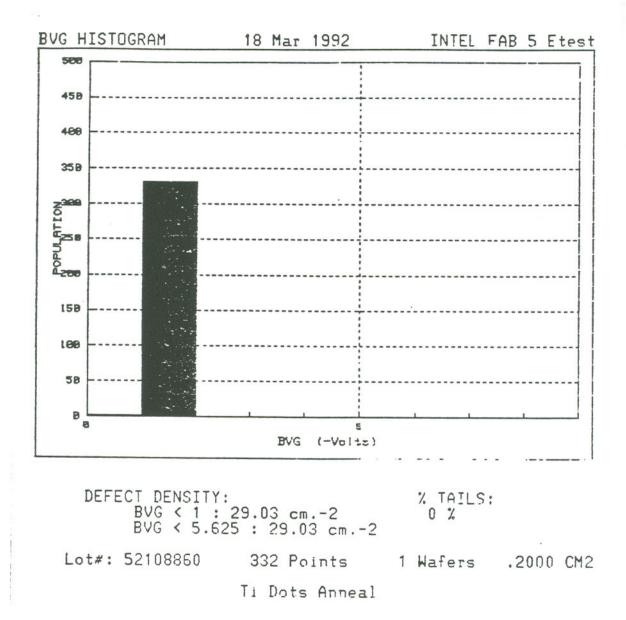

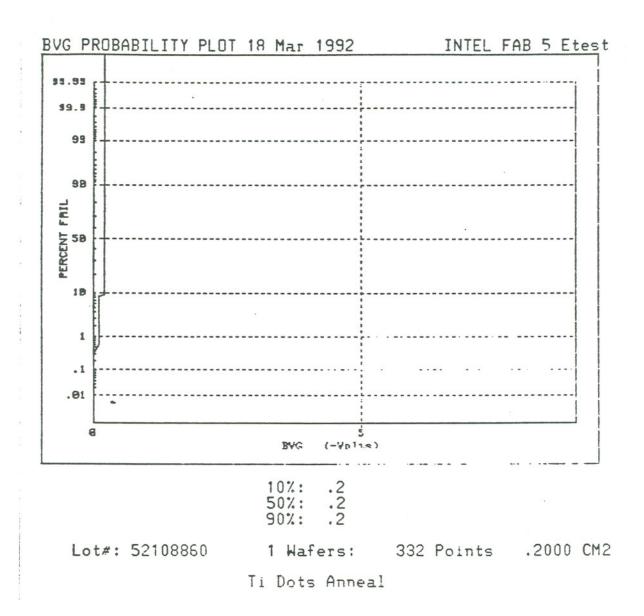

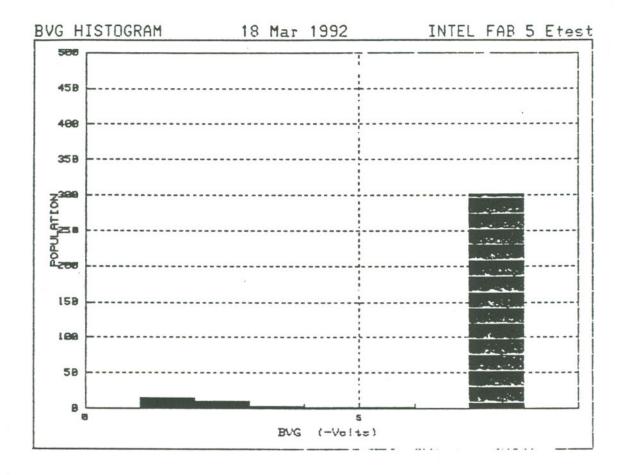

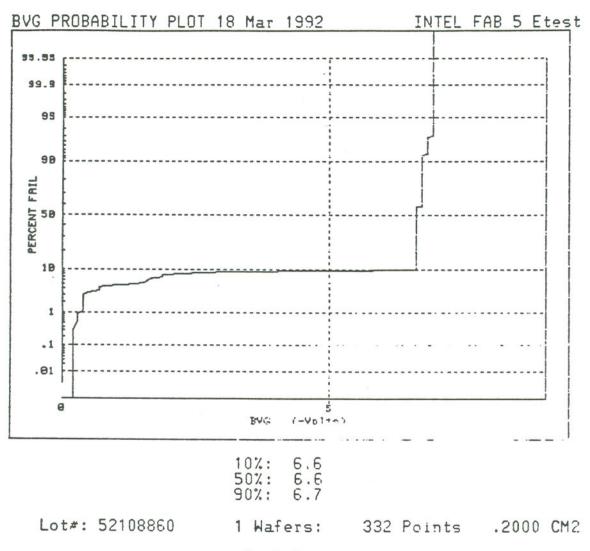

| Appendix i. BVG oxide Measurements, Histograms, Probability<br>Plots and Wafer Maps                                                                |

| Appendix ii. Hardness Measurements for AI, AI-Cu and AI-W 170                                                                                      |

| Appendix iii. Determination of the Stress Levels in the SiO <sub>2</sub><br>Heat Treated for 4hrs. with a Directly Deposited<br>Al5wt%Cu Electrode |

| Biographical Note                                                                                                                                  |

# LIST OF TABLES

| 1. Resistivities of Conductors                                    |

|-------------------------------------------------------------------|

| 2. BVG Measurements for Metallization Disk Arrays                 |

| on (100) Si Wafers with 7nm of Silica                             |

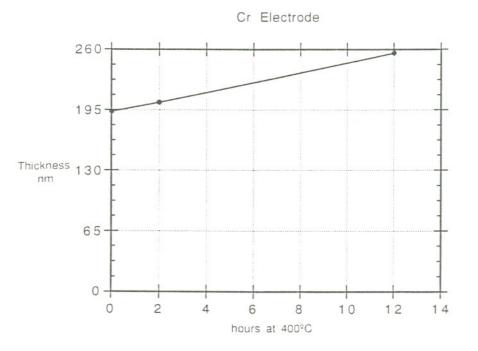

| 3. Electrode Thickness, Growth Rate and BVG vs. Hours             |

| of Heat Treatment                                                 |

| 4. The SiO <sub>2</sub> /Si Reaction Layer Thickness              |

| 5. The Metal/Silica Reaction Layer Thickness                      |

| 6. Silica Thickness and Heat Treatment                            |

| 7. Electrode Grain Diameter and Heat Treatment Duration 99        |

| 8. Post Heat Treatment Si Diffusion Depths into Electrodes 102    |

| 9. Silica/Si Interface Roughness and Heat Treatment               |

| 10. Electrode/Silica Interface Roughness and Heat Treatment . 103 |

| 11. Silica Structure and Heat Treatment 105                       |

# LIST OF FIGURES

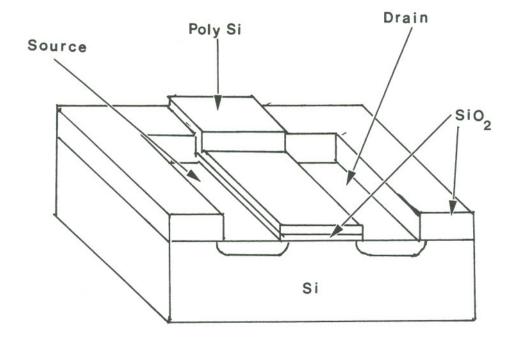

| 1 | a. Typical MOSFET 8                                              |

|---|------------------------------------------------------------------|

|   | b. High speed sub-µm MOSFET                                      |

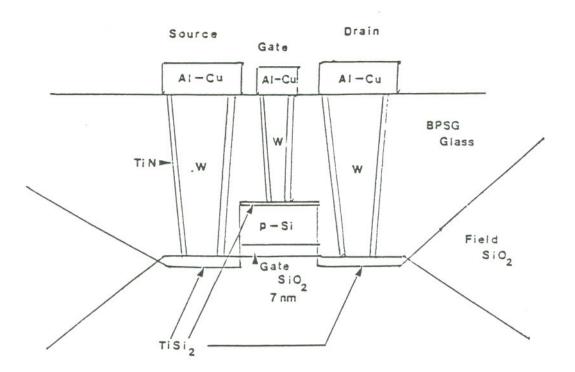

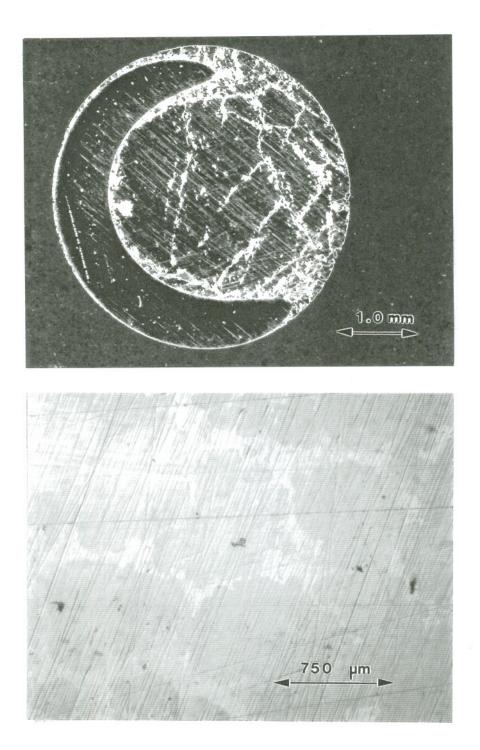

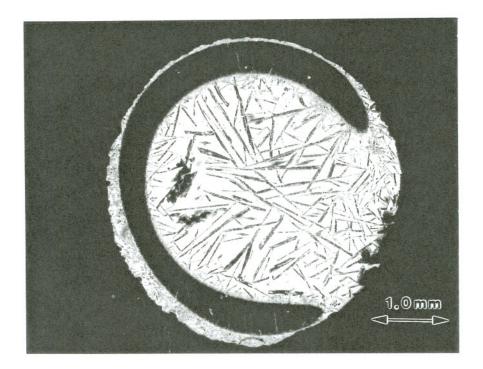

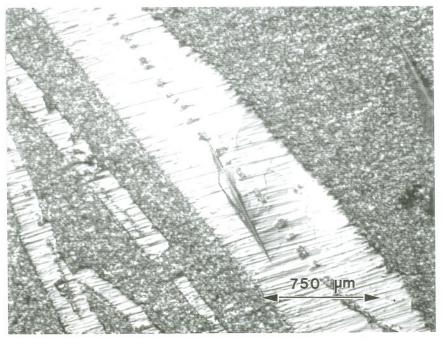

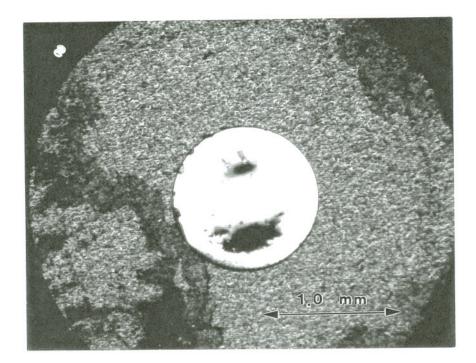

| 2 | a. Optical image of (100) Si wafers with metallization 27        |

|   | b. Enlargement of metallization disks                            |

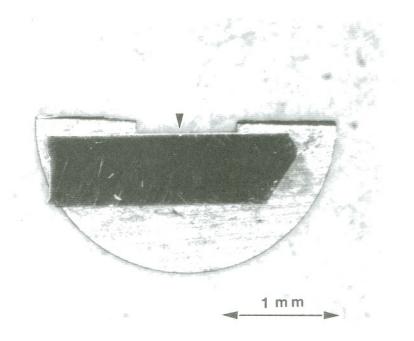

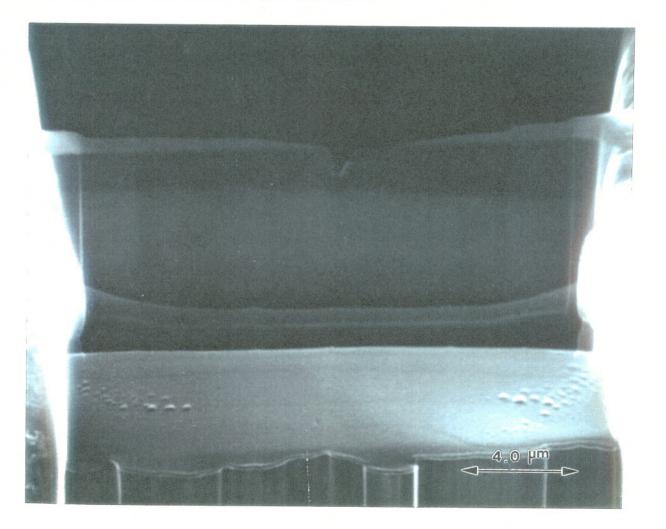

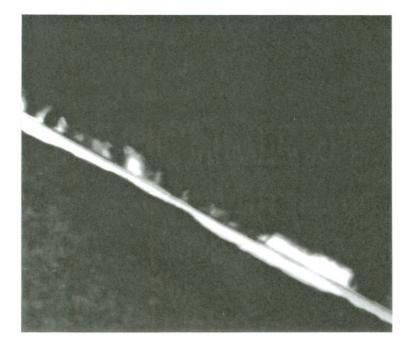

| 3 | Optical image of FIB produced TEM cross-section                  |

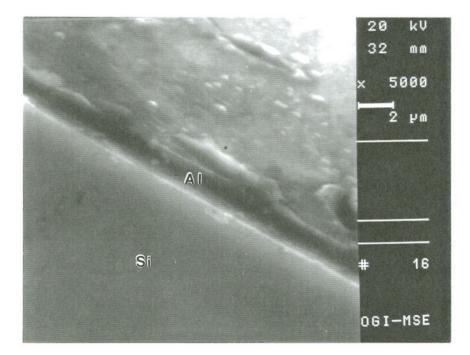

| 4 | SEM image of FIB produced TEM cross-section                      |

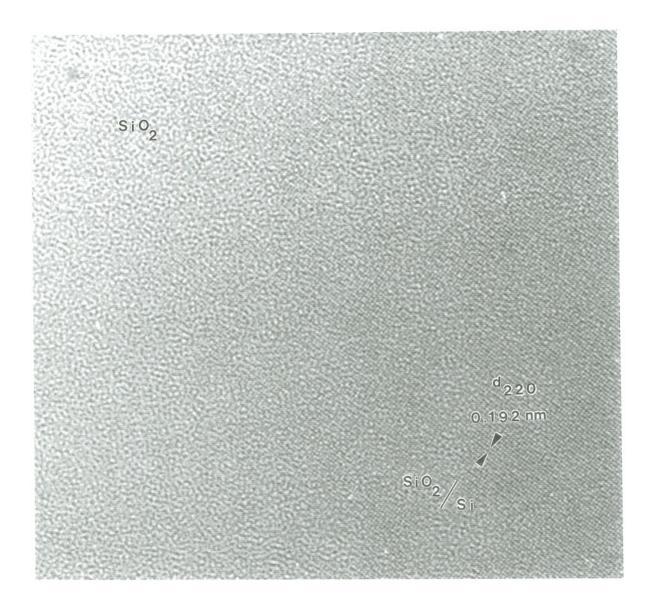

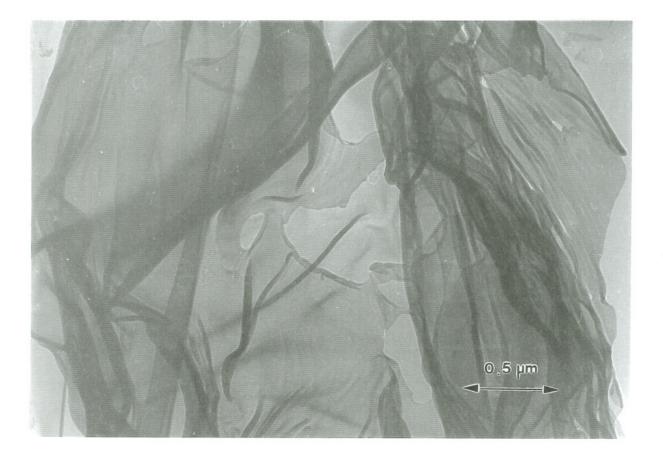

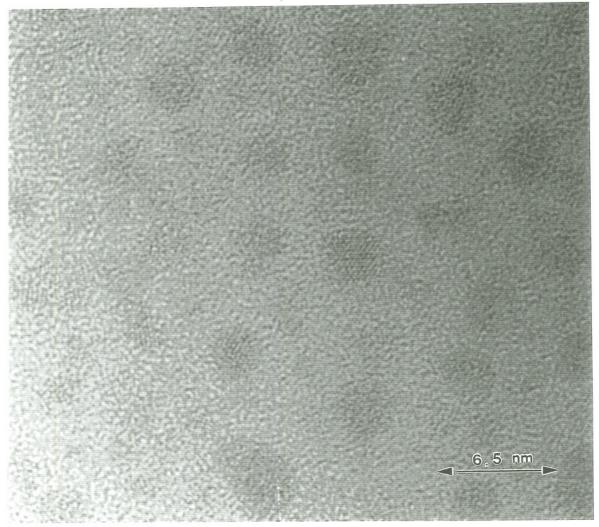

| 5 | a. Atomic resolution TEM image of $SiO_2$ as deposited           |

|   | planar section                                                   |

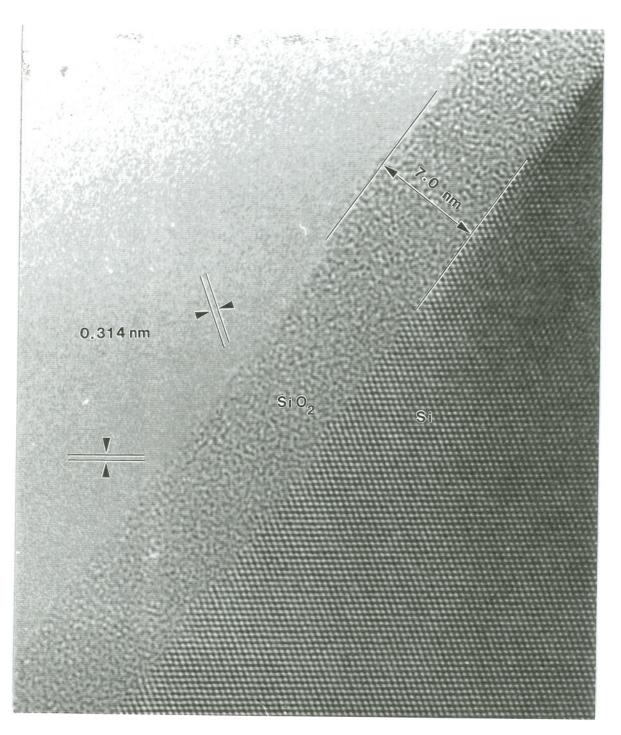

|   | b. Atomic resolution image of SiO <sub>2</sub> as deposited      |

|   | transverse cross-section 38                                      |

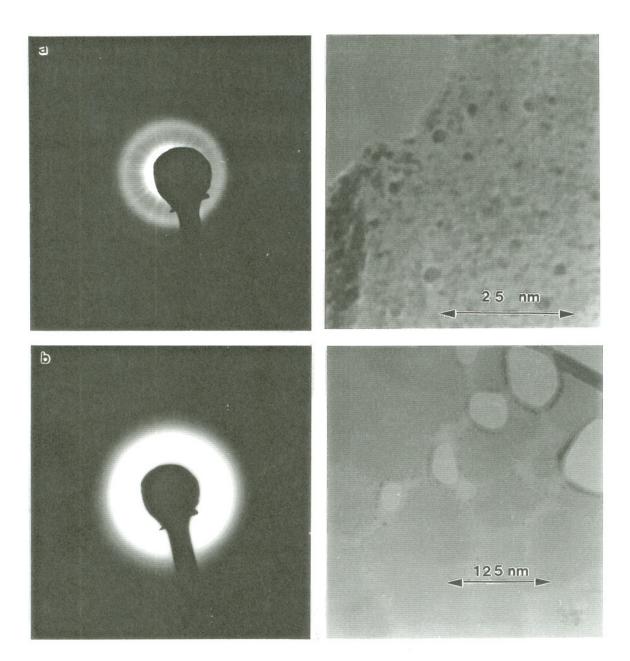

| 6 | a. TEM bright field image of planar section of SiO2              |

|   | heat treated for 2hrs at 400°C 39                                |

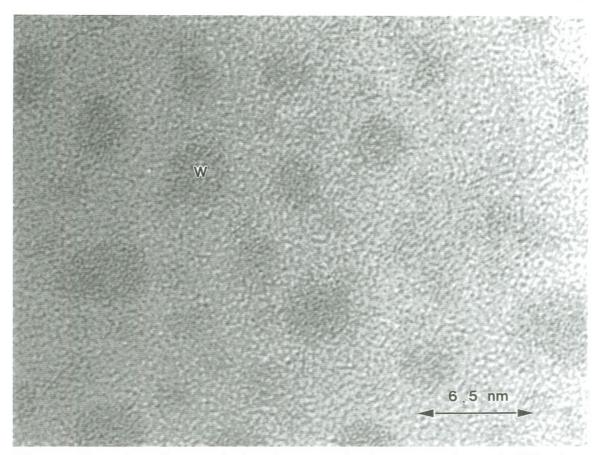

|   | b. Atomic resolution image of planar section of $\mathrm{SiO}_2$ |

|   | heat treated for 2hrs. and decorated with W islands 40           |

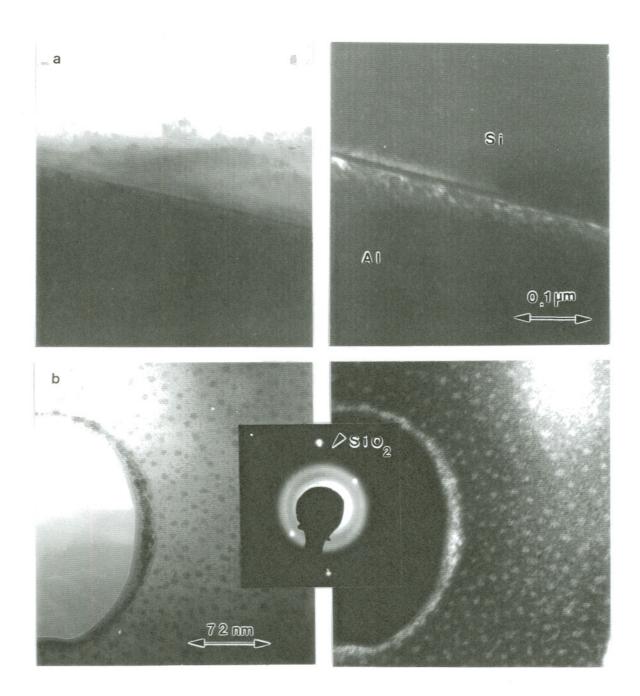

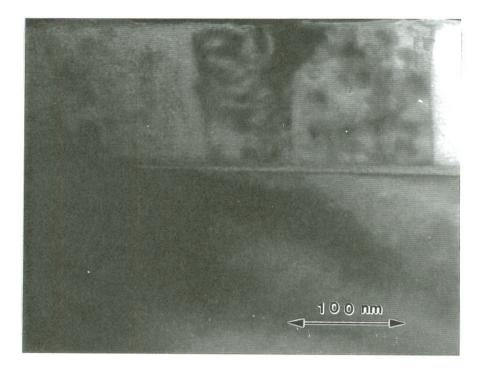

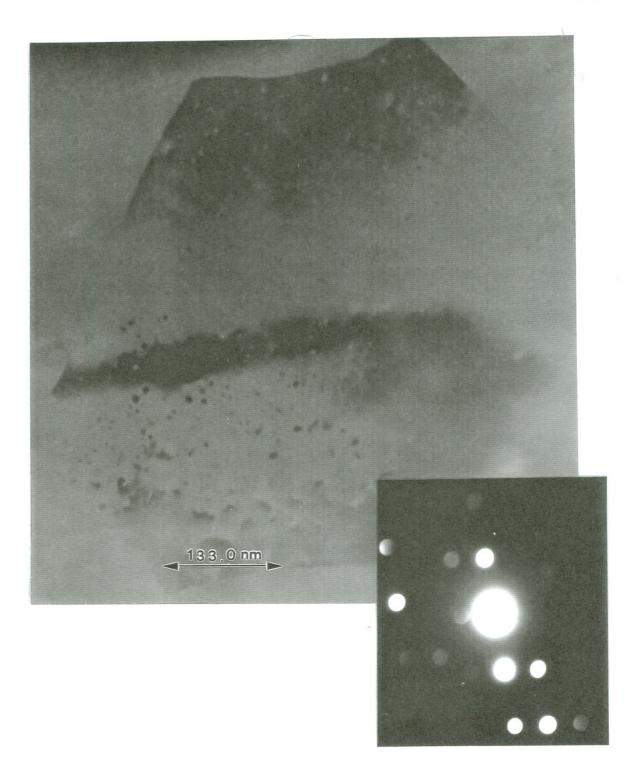

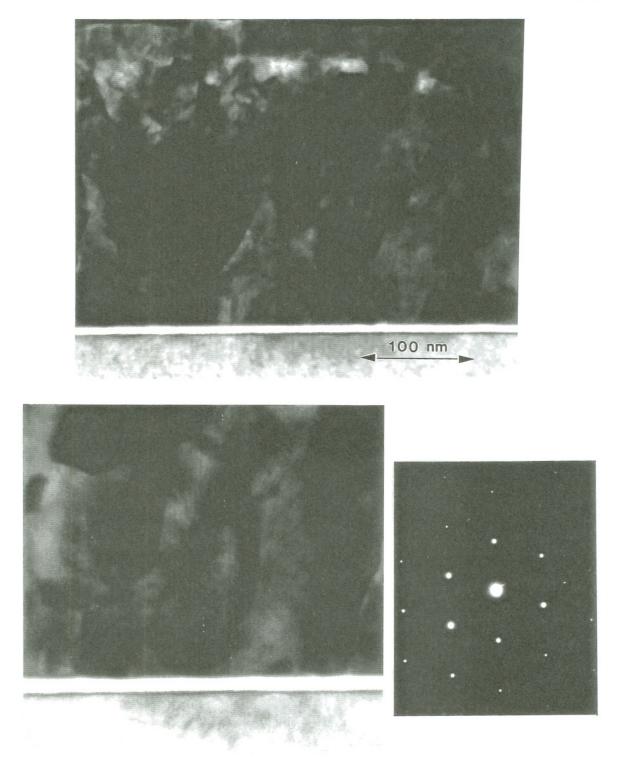

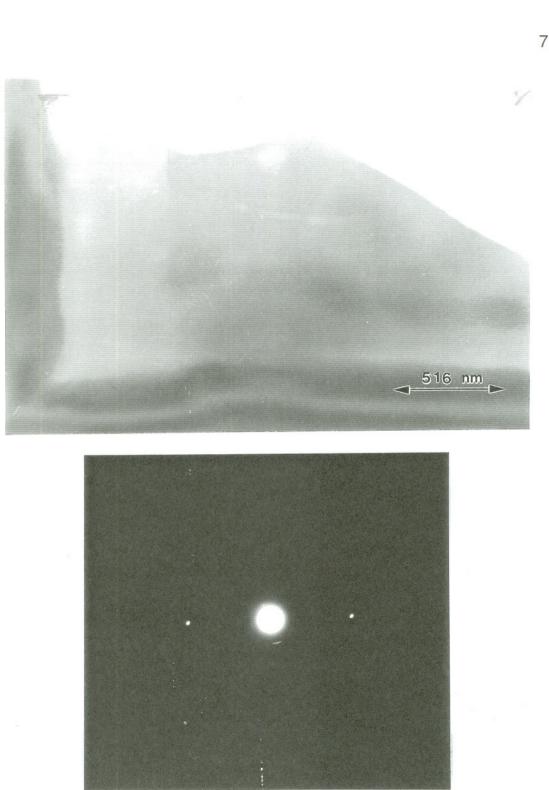

| 7 | TEM image of as deposited AI-1Si with selected area              |

|   | diffraction pattern of interfaces                                |

| 8 | a. TEM bright field and dark field of Al-1Si heat treated        |

|   | for 2hrs at 400°C                                                |

|   | b. TEM bright field and dark field images of nanocrystalline     |

|   | quartz in failed oxide 43                                        |

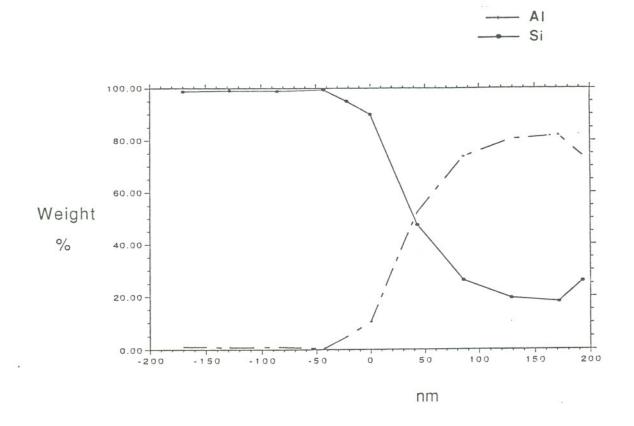

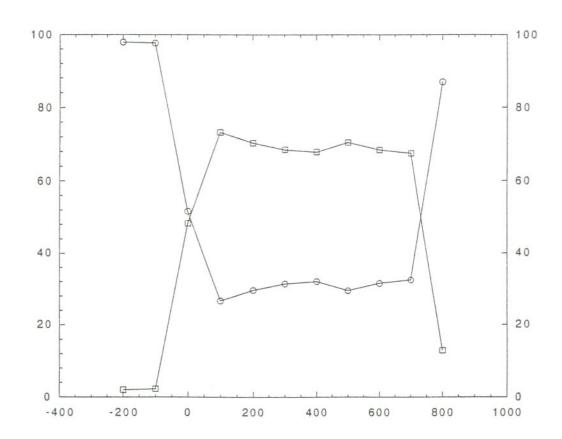

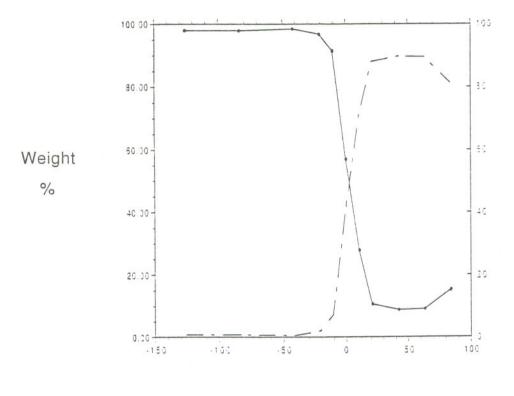

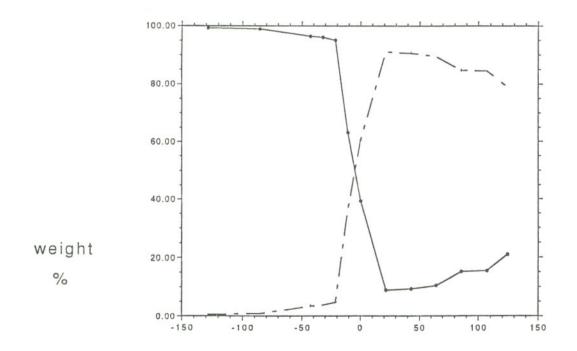

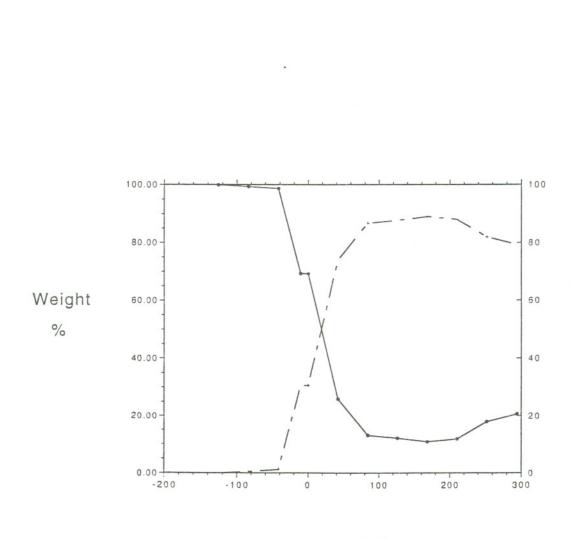

|   | c. Al-1Si-2hrs, compositional profile                            |

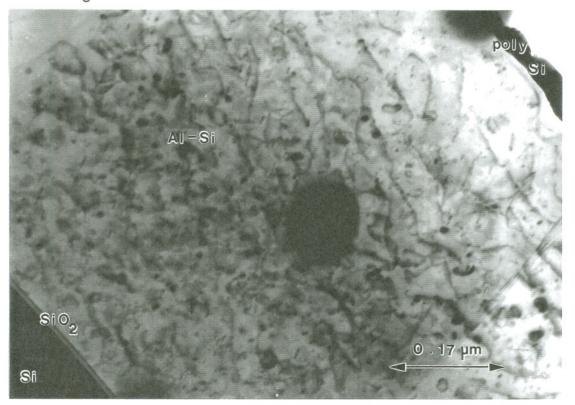

| 9 | a. Bright field TEM image of Si, $SiO_2$ , Al-1Si and            |

|   | diffusion formed poly-Si after 12 hrs at 400°C 45                |

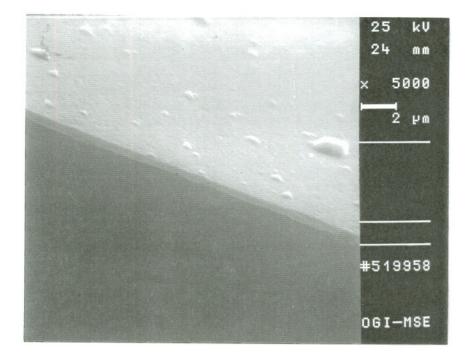

| 9 b. SEM of cleaved Al-1Si metallization disks as          |    |

|------------------------------------------------------------|----|

| deposited and heat treated for 12hrs                       | 46 |

| c. Compositional profile for Al-1Si, 12hrs at 400°C        | 47 |

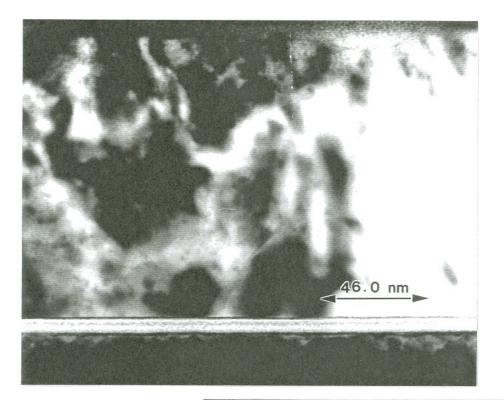

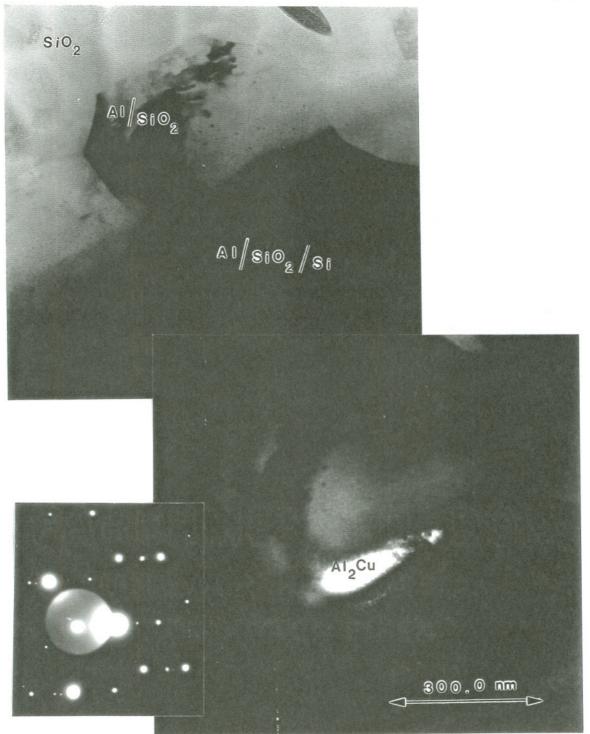

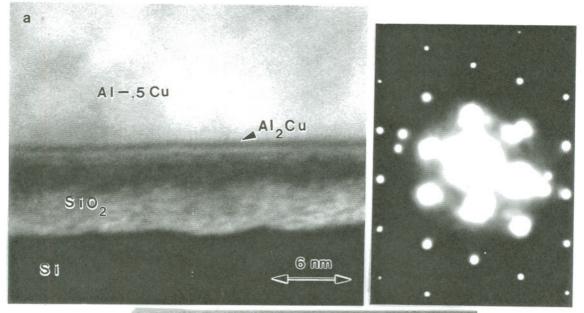

| 10a. TEM bright field image of interfacial region of Al5Cu |    |

| as deposited with diffraction pattern                      | 49 |

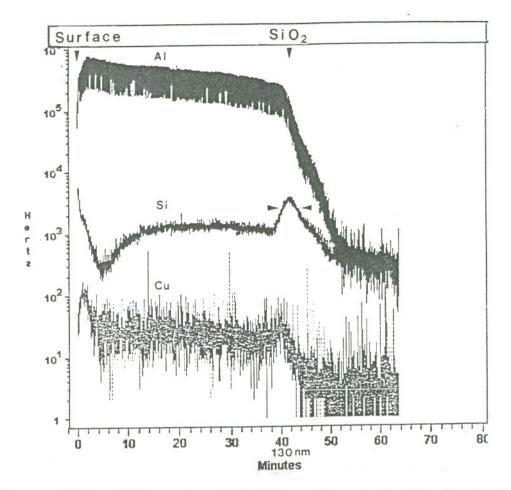

| b. Al5Cu as deposited compositional profile                | 50 |

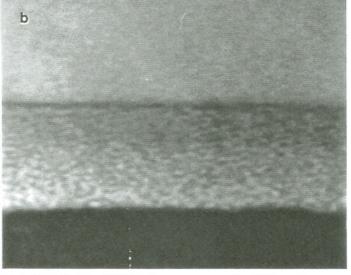

| 11a. TEM bright field image and diffraction pattern Al5Cu  |    |

| heat treated for 2hrs                                      | 52 |

| b. Compositioinal profile for Al5Cu-2hrs                   | 53 |

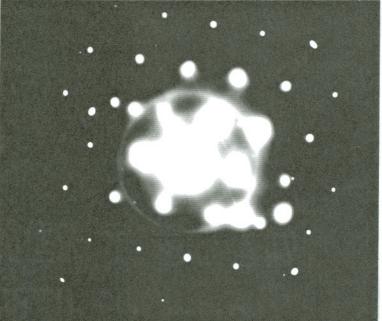

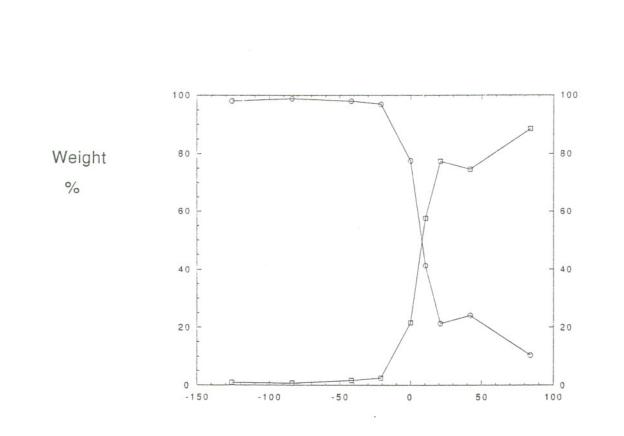

| 12a. TEM bright field image and diffraction pattern        |    |

| for Al5Cu-4hrs                                             | 55 |

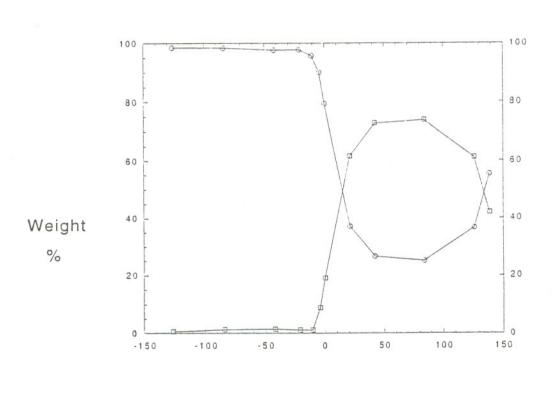

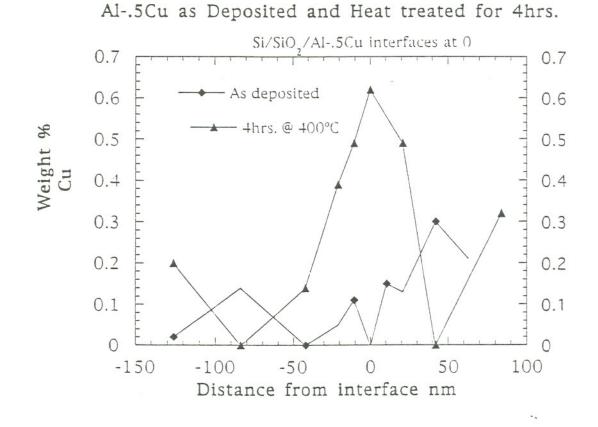

| b. Compositional profile for Al5Cu-4hrs                    | 56 |

| c. Compositional profile showing Cu segregation            | 57 |

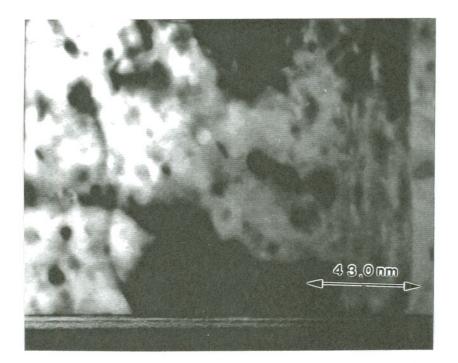

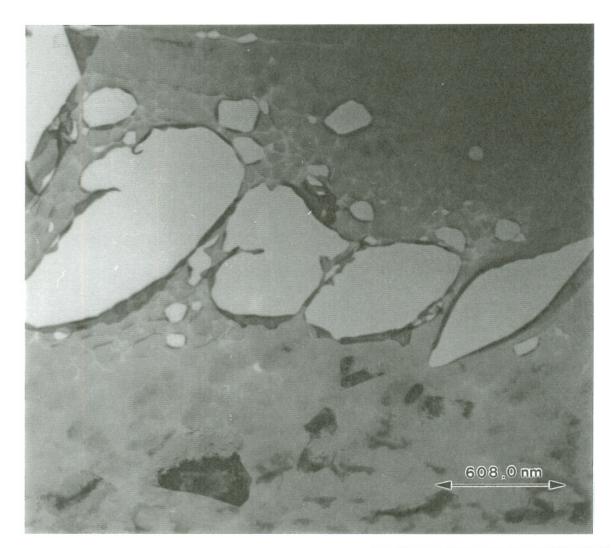

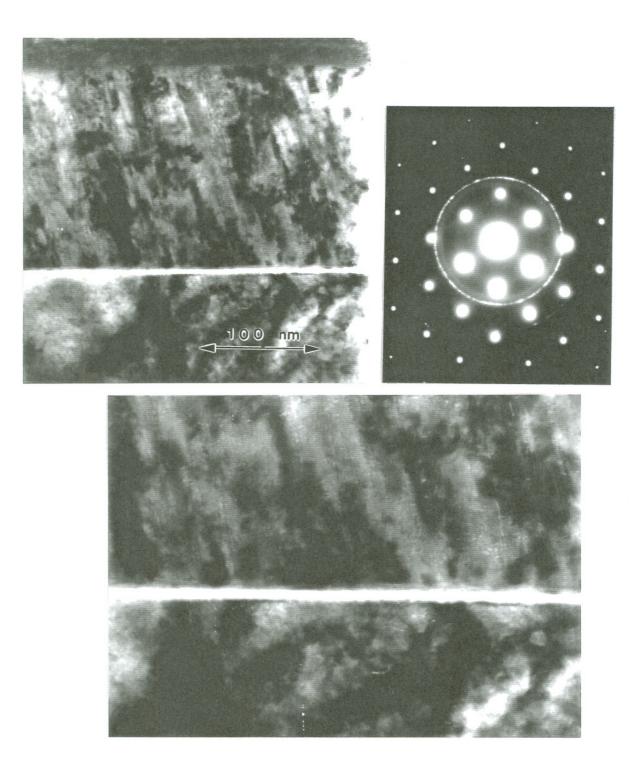

| 13a. TEM bright field image, planar section Al5Cu -4hrs    | 60 |

| b. TEM bright field /dark field pair Al5Cu-4hrs            | 61 |

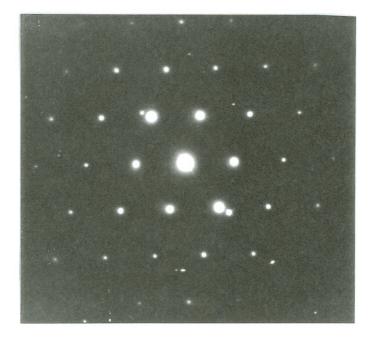

| c. Planar section of oxide showing grain like structures   |    |

| and diffraction pattern, Al5Cu-4hrs                        | 62 |

| d. FIB produced SIMS profile of Al5Cu-4hrs                 | 63 |

| 14a. Bright field TEM image and diffraction pattern for    |    |

| Al5Cu-11.25hrs                                             | 64 |

| b. Bright field TEM image for Al5Cu-2hrs with a less       |    |

| distinct diffusion zone for the AI and Cu                  | 64 |

| c. Compositional profile for Al5Cu-11.25hrs                | 65 |

| 15. Bright field TEM image and diffraction pattern for     |    |

| as deposited Cr                                            | 67 |

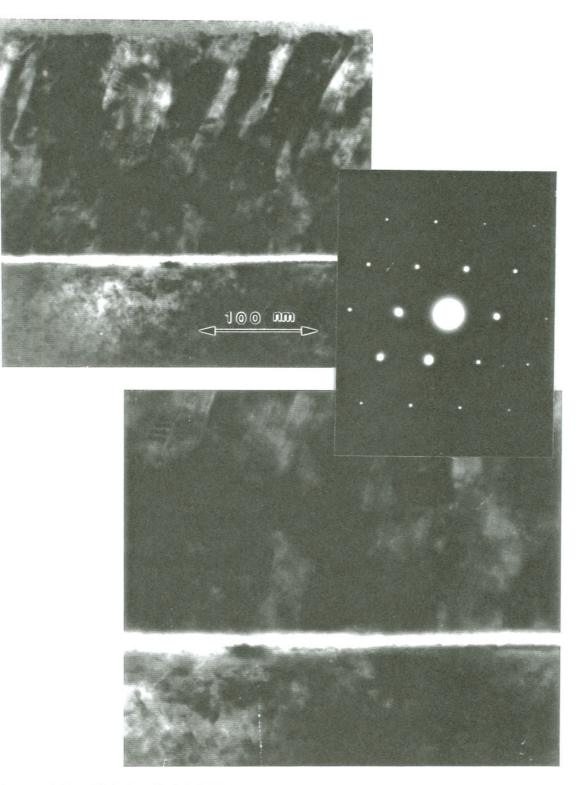

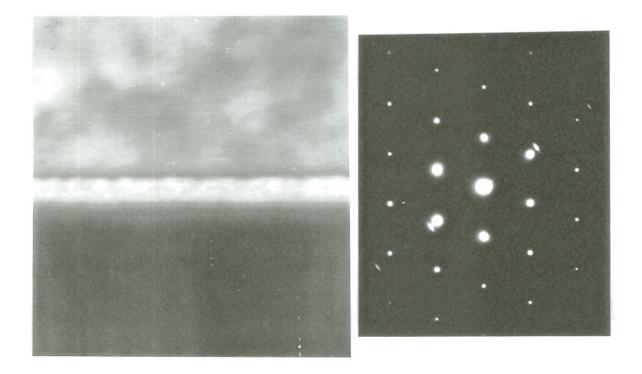

| 16a. Bright field TEM image and diffraction pattern for            |    |

|--------------------------------------------------------------------|----|

| Cr -2hrs                                                           | 69 |

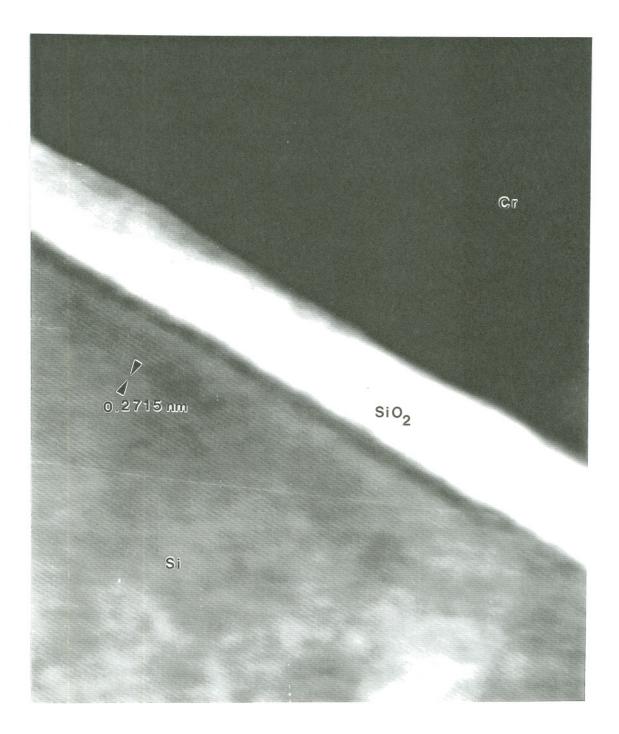

| b. High resolution image of the SiO <sub>2</sub> /Si interface for |    |

| Cr-2hrs                                                            | 70 |

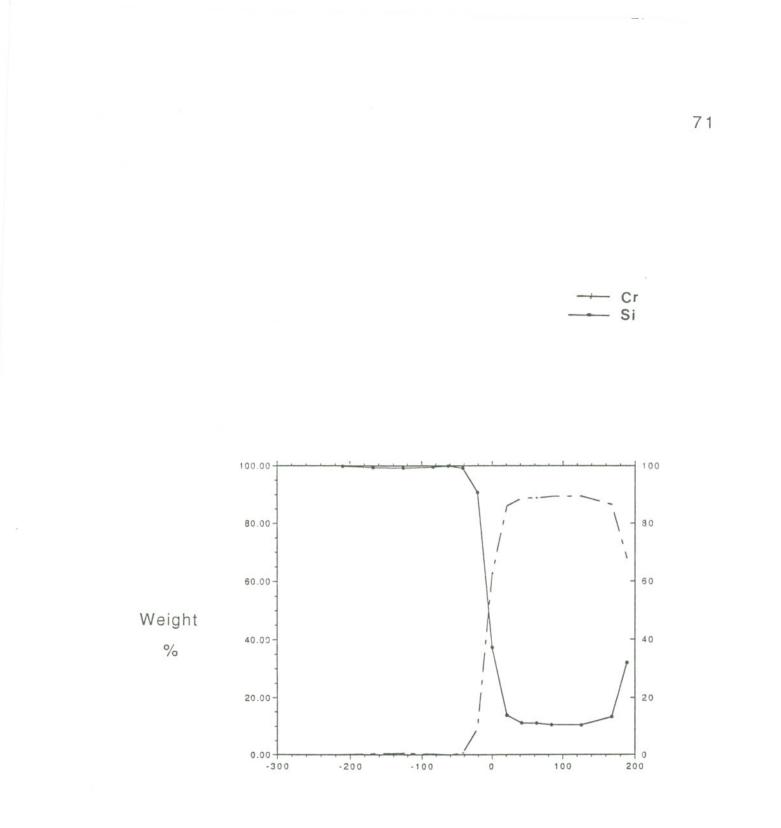

| c. Compositional profile for Cr-2hrs                               | 71 |

| 17a. TEM bright field and diffraction pattern for Cr-12hrs         | 73 |

| b. Compositional profile for Cr-12hrs                              | 74 |

| 18 TEM bright field and diffraction pattern for Ti as deposited.   | 75 |

| 19a. Bright field TEM Ti-2hrs                                      | 77 |

| b. Diffraction pattern interfacial regions                         | 77 |

| c. Diffraction pattern Si                                          | 77 |

| d. Diffraction pattern Si and $Ti_3Si$                             | 77 |

| 20. Bright field TEM image and diffraction pattern for             |    |

| as deposited SiO <sub>2</sub>                                      | 79 |

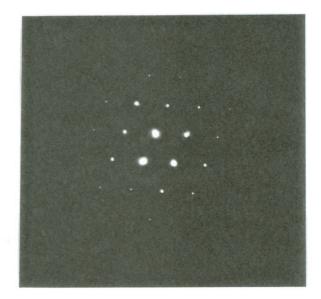

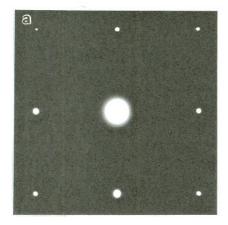

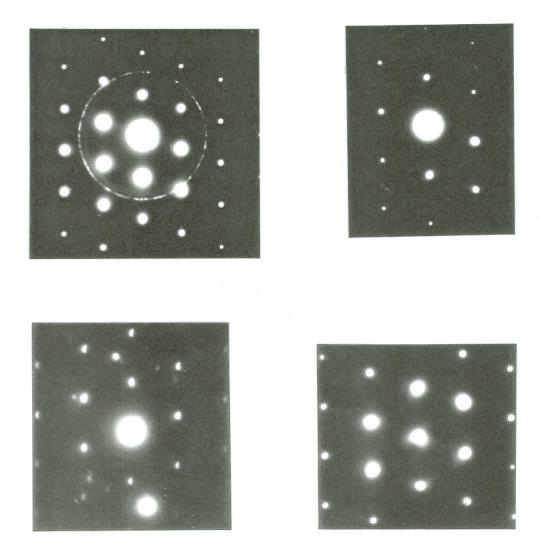

| 21. Series of diffraction patterns produced by a region of         |    |

| as deposited SiO <sub>2</sub>                                      |    |

| a. without Al                                                      | 80 |

| b. with Al                                                         | 80 |

| c. following electron irradiation                                  | 80 |

| 22. Atomic resolution TEM image of W islands deposited on heat     |    |

| treated SiO <sub>2</sub>                                           | 81 |

| 23. Diffraction patterns before and after electron irradiation     |    |

| for W on heat treated SiO <sub>2</sub>                             | 82 |

| 24. Graph of electrode thickness vs. heat treatment time           |    |

| for Cr                                                             | 90 |

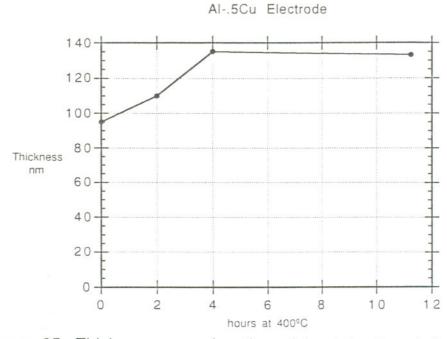

| 25. Graph of electrode thickness vs. heat treatment time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| for Al5Cu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 26. Graph of electrode thickness vs. heat treatment time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| for Al-1Si                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

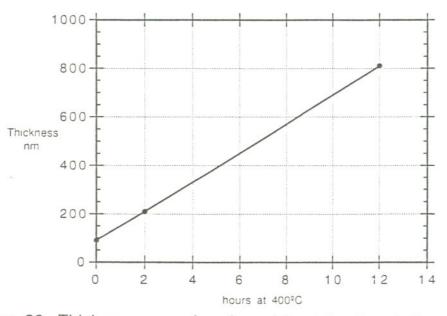

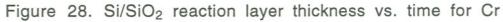

| 27. Si/SiO <sub>2</sub> reaction layer thickness as a function of time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| at 400°C in N <sub>2</sub> for Al-1Si                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

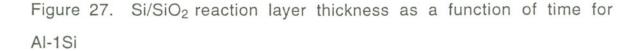

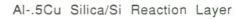

| 28. Si/SiO <sub>2</sub> reaction layer thickness vs. time for Cr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

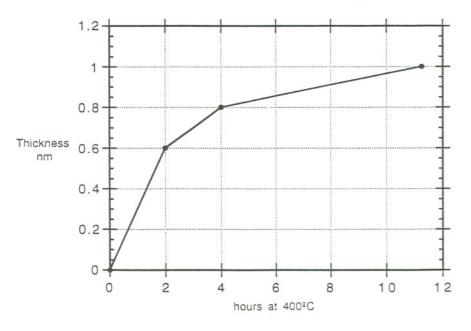

| 29. Si/SiO <sub>2</sub> reaction layer thickness vs. time for Al5Cu 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 30. Al-1Si/SiO <sub>2</sub> interface reaction layer thickness vs. time 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

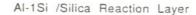

| 31. Al5Cu/SiO <sub>2</sub> reaction layer thickness vs. time 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

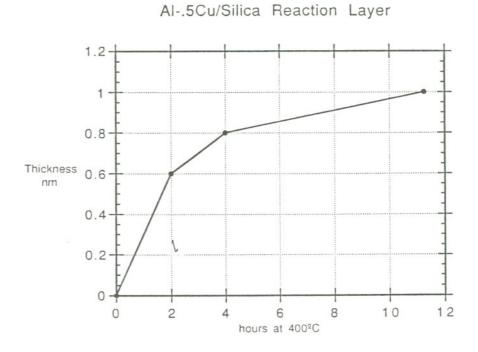

| 32. Al-1Si electrode oxide thickness vs. time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

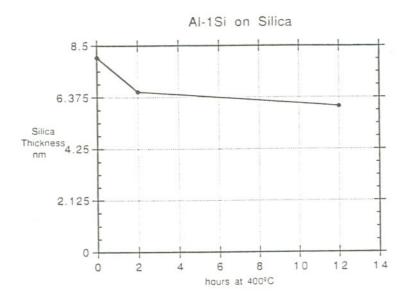

| 33. Al5Cu electrode oxide thickness vs. time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

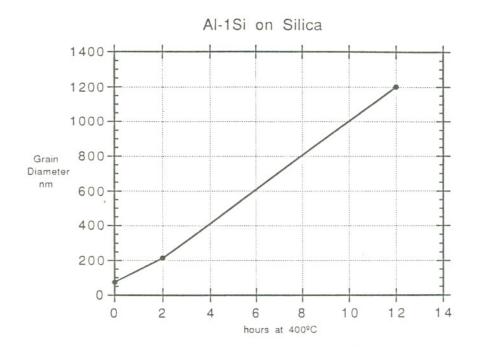

| 34. Al-1Si grain diameter vs. time at $400^{\circ}C$ in $N_2$ 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

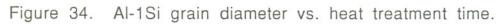

| 35. Al5Cu grain diameter vs. time at 400°C in $N_2 \hdots n_2$ 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

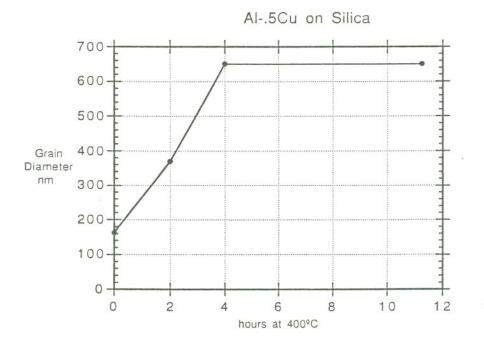

| 36. Cr grain diameter vs. time at 400°C in $N_2 \hdots n_2 \hdots n_1 \hdots$ |

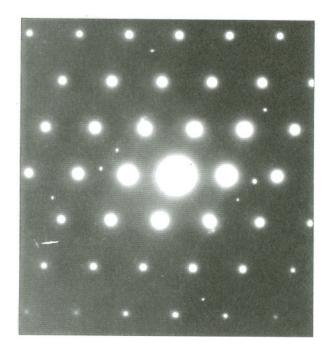

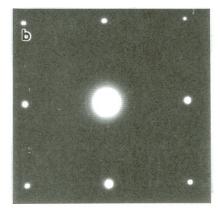

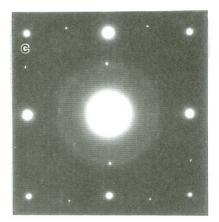

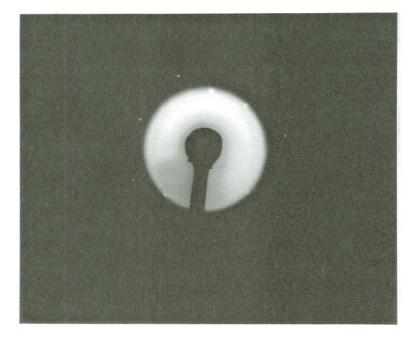

| 37a. Selected area electron diffraction pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| as deposited, high and low Si flux oxides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| b. Bright field TEM of oxide heat treated with Al5Cu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| for 4hrs., planar section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

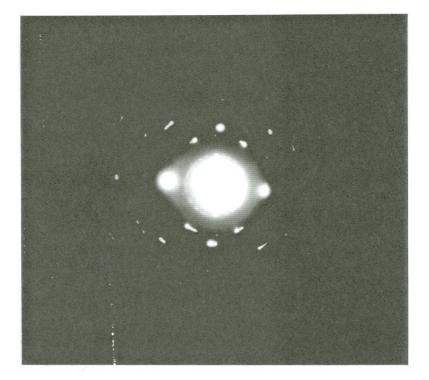

| 38. Selected area electron diffraction pattern showing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| increase in texture with increased heat treatment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

----

### ABSTRACT

# THE MICROSTRUCTURAL EFFECTS OF METALLIZATION AND HEAT TREATMENT ON THIN GATE OXIDE FOR USE IN SUB-MICRON MOSFETS

John M. Mc Carthy Supervising Professor: Jack Devletian

Metals deposited directly on thin gate oxide to test the quality of the oxide must be stable. This research tests the stability of metals for possible use in gate oxide monitor current flow tests (GOM) or as a gate electrode in sub-micron MOSFETs.

Arrays of metallization disks with 5mm and 0.8mm diameters of Al-1wt%Si, Al-.5wt%Cu, Ti and Cr were magnetron sputter deposited directly on 7nm of thermally grown SiO<sub>2</sub> on (100) Si wafers and then heat treated at 400°C in N<sub>2</sub> to determine the effect of heat treatment on break-down voltage(BVG) for the MOS thin film devices. Al-1wt%Si and Al-.5wt%Cu were also deposited on poly-Si electrodes. BVG measurements were performed on as deposited and heat treated patterned wafers. Analytical electron microscopy was performed on transverse cross-sections and planar sections of the devices to correlate good and bad BVG performance with microstructural changes that occurred during heat treatment. A mechanism of oxide breakdown was proposed based on observed changes in microstructures and chemistries of the thin films.

xiii

Metallizations that maintained a high BVG, Cr and Al-.5wt%Cu, were given extended heat treatments to test stability and to characterize their diffusion barriers, nanometer scale layers of  $Cr_2O_3$  and  $Al_2Cu$  respectively, which limited diffusion of the substrate Si into the electrode. Al-1wt%Si, the electrode with the lowest as deposited BVG, was given an extended heat treatment to characterize the mechanisms of change in the metallization, silicon dioxide and Si which lead to SiO<sub>2</sub> breakdown.

Structural changes in the oxide were detected with electron diffraction patterns following heat treatment. Nearest neighbor distances were reduced and nano-crystalline quartz appeared in the originally completely amorphous silica heat treated with an Al-1wt%Si electrode. The mechanisms of reduction of the BVG for oxides during heat treatment with a metallization is structural damage to the amorphous silica caused by the diffusion of Si from the substrate through the oxide into the electrode, the diffusion of metal into the oxide and reduction of oxide thickness by reaction with the metallization. The Al-1wt%Si as deposited directly on SiO<sub>2</sub> and heat treated, had the lowest BVG's and had sustained the greatest number of atomic displacements which resulted in quartz crystallites forming within the vitreous silica.

#### 1. INTRODUCTION

The reduction of the dimensions of structures in microelectronic devices makes the control of diffusion and nanometer scale defects crucial to the performance and reliability of these devices. The ability to produce stable, defect free thin layers of insulators and conductors reduces leakage currents, increases the break down voltage and increases service life. Interfaces that are atomically flat minimize surface states and traps which decrease the numbers of charge carriers and their mobility. A flat interface also decreases parasitic capacitance which limits the speed at which a device can run. Reactions between the metallization and the gate oxide must be eliminated or limited to preserve defect free thin films with flat interfaces. Reactions include precipitation, diffusion and phase changes within and between the component thin films which can cause the degradation of the gate electrode and oxide and may contaminate the Si substrate. In the submicron metaloxide-silicon-field-effect transistor (MOSFET) diffusion distances are smaller between metal conductors and the Si since the insulating layers have been reduced to less than 10nm bringing metals such as Ag, Au, Cu, or Al close to the Si/SiO<sub>2</sub> interface and the shallow junctions of the MOSFET where trapping states can be introduced and the performance of the device degraded. The reduced surface area of the gate electrode in the sub-micron MOSFET increases current densities in the commonly used, highly doped, high resistivity poly-Si (500µohm-cm) to the point that power limits

require the use of a lower resistivity conductor such as stable refractory W deposited directly on the gate oxide or a lower melting point metal such as AI or Cu deposited on barrier layers such as TiN or Ti-W are necessary to limit diffusion.(1) Pores, pinholes and small grain size are microstructural defects that limit the effectiveness of the barrier layer as a conductor and a diffusion barrier. The gate structure can also be degraded by pores in the oxide which serve as rapid diffusion and low resistance current paths to the silicon.(2.3) Diffusion and the proximity of dissimilar materials can lead to phase changes at interfaces (precipitates) which at best roughen interfaces and if on a scale approaching the thickness of the thin films can cause shorts or degrade diffusion The films used in semiconductor devices must not go barriers. through unexpected phase changes that may roughen the interface or introduce undesirable electronic characteristics during processing or during subsequent service. These microstructural defects and characteristics visible and measurable in an analytical TEM/STEM, can control the performance of thin films in microelectronic devices.

The deposition of microstructural and electronic defect free homogeneous oxide thin films on semiconductor substrates at low temperatures is desirable to produce predictable shallow junction devices that are less susceptible to environmental breakdown and interdiffusion. The techniques to produce such films are low pressure chemical vapor deposition, plasma enhanced chemical vapor deposition and the dry thermal growth of oxide. This research

gives a better understanding of the mechanisms of change in single and multilayered metallic electrodes on high quality thermally grown 7nm silicon dioxide through detailed TEM/STEM microstructural analysis. Understanding diffusion and phase changes in the gate structure will permit the control of degradation such as poly-Si dopant depletion(4) and the reduction of the resistivity of the gate oxide. Metals were deposited on 6 to 8nm thick oxide films on a Si substrate. Heat treatments on the MOS devices were done in a quartz lined furnace with an N<sub>2</sub> ambient. Break down voltage measurements were done on heat treated specimens and on as deposited MOS devices.

The microstructure of the metal electrode and its interface with the silica were studied. Features such as grain size and interface roughness were measured. In studying the insulator, the conductor and the diffusion barrier, if present, emphasis was placed on understanding diffusion processes, microstructural changes and phase changes at interfaces and within the thin films in these reduced vertical dimension devices. A new mechanism of oxide degradation is proposed. Defects associated with poor performance or severe breakdowns were identified.

The goal of this work is to identify conductors for use in thin films to permit the rapid fabrication of metal/oxide/Si (MOS) devices with an as deposited high oxide breakdown voltage which is maintained during heat treatment. This MOS device will permit the rapid testing of thin gate oxide during the manufacture of sub-µm

MOSFETs. Such conductors could also be used to produce MOSFETs with high speed, high charge carrier mobility and low power consumption.

### 2. OUTLINE OF EXPERIMENTS

The creation of ohmic contacts to the source and drain of a MOSFET, following Ti deposition, requires heat treatment at 400°C to form TiSi<sub>2</sub> in a N<sub>2</sub> ambient for 2 hours. Czochralski Si wafers, 6 inches in diameter with 7nm of oxide on the surface had arrays of 5mm disks of metal 0.2µm in thickness deposited by magnetron sputtering. Single film metallizations deposited directly on the oxide included Al-1wt%Si, Ti, Al-.5wt%Cu and Cr. Metallizations using doped poly-Si as an electrode include Al-1wt%Si and Al-.5wt%Cu. These wafers were given a heat treatment at 400°C in N<sub>2</sub>. In addition to complete wafers deposited with a large number of metal disks small portions of wafers deposited with Al-1wt%Si, the worst BVG performer. Cr and Al-.5wt%Cu the best performers were given extended heat treatments to better understand thermally caused microstructural changes in the Al-1Si and test the stability of the Al-.5Cu and Cr electrodes. Findings in this study establish the formation of a hard (see Appendix II) relatively high melting point AI-Cu intermetallic at grain boundaries and interfaces soft, low melting point Al. to stabilize Analytical electron microscopy was performed on planar sections and transverse crosssections of these metal-oxide-silicon(MOS) devices. Interface roughness, inter and intra film phase identification, thickness, grain size, composition and texture were measured and comparisons between the control and the heat treated specimens made. Correlations were made between heat treatment caused

microstructural changes and performance as indicated by breakdown voltage measurements.

In addition to experiments with thin metal films of the thickness to be used in devices(100-300nm), electron transparent metal films (less than 100nm) were deposited on the gate oxide. TEM/STEM in-situ experiments with planar sections of the metal, metal/SiO<sub>2</sub> and metal/SiO<sub>2</sub>/Si were performed. Planar sections of the in-situ and heat treated metal disk specimens permit the examination of hundreds of square microns of interface whereas transverse cross-sections produce interface areas limited by the thickness of the foil(<0.1µm). Selected area electron diffraction of these planar sections provided high sensitivity to small volume fraction phase changes at the interface allowing characterization of the nucleation and initial growth of new phases. Initial nucleation could also be studied if growth was interrupted in the 0 to 3nm thickness range for the metallization layer or layers. The large sample of interface insured that the microstructures observed would be representative.

### 3. BACKGROUND

A metal-oxide-silicon-field effect transistor (MOSFET) is a switch that permits current to pass between it's source and drain by applying a field through a thin oxide layer to a narrow channel of Si (gate) between the source and drain . A early design and a high performance submicron MOSFET design with W vias is shown in figure1. Notice that much of the areas of metal contacts of source, drain and gate are above the field oxide to minimize parasitic capacitance, the relatively high resistance poly-silicon electrode and the very thin 7nm gate oxide.

A thin gate oxide causes four major problems; increased leakage currents, the accelerated introduction of metal from the electrode to the doped Si substrate containing the source, the drain and the gate channel, the accelerated migration of Si and dopants into the gate electrode and possible phase changes in these diffusion zones. Leakage currents, diffusivities, the thickness of films and grain size will largely determine how soon, the degree of and types of microstructural changes that occur in these multi-layer MOS devices during processing heat treatments and service.

Phase changes will occur at interfaces and be small in volume fraction at first. Electron diffraction will permit the detection of these phases and their identification during the early stages of nucleation and growth.(5) Conventional methods of detection such as X-ray diffraction and Rutherford backscatter techniques would not detect layers of materials less than 20nm thick nor do they give morphological and exact location information available from electron microscopy.(6) Analytical electron microscopy can give a much more detailed and complete microstructural evolution of the films and reduce the thickness detection limit by an order of magnitude.(5) A large part of the research will involve identifying the sources of reactants and the reaction products following heat treatment.

Figure 1a. Typical MOSFET with a doped polysilicon gate electrode.

Figure 1b. Very high speed sub-µm MOSFET with W vias.

The commonly used, effective, thick and low conductivity polysilicon electrode adds to the series resistance of the device and adds a step to the fabrication process. A metallization that would be compatible with direct contact to the Si of the drain and the source and to the  $SiO_2$  of the gate would simplify fabrication, provide a rapidly deposited test electrode, increase read-write frequency and diminish power consumption. W and Mo, refractory metals, directly deposited on  $SiO_2$  have been successfully used as gate electrodes.(7-16) Alternatively a thin, high conductivity, diffusion barrier-electrode such as TiN or Ti-W could be used instead of a poly-silicon electrode.

In the following sections the thin film building blocks of a submicron MOSFET gate structure are discussed; the SiO<sub>2</sub>, diffusion barriers, metallizations and the interfaces. The final sections discuss the primary characterization techniques; analytical electron microscopy, high resolution electron microscopy and break-down voltage measurements.

### The Microstructure and Properties of SiO2

Thermally grown and chemical vapor deposited (CVD) SiO<sub>2</sub> used in the electronics industry is an amorphous solid with short range order having a Si atom at the center of a tetrahedron covalently bonded to 4 oxygen atoms at the vertices of this unit cell with equal O-Si-O bond angles. The tetrahedra in turn have common O atoms at their vertices with other tetrahedra producing Si-O-Si bonds with random angles. These tetrahedra at most have a common edge but never a common face forming a randomly connected network with a variable density and pores which does not tile space as do the unit cells of crystalline material.(17-19) Material with this type of short range order is referred to as vitreous. Thermally grown vitreous silicon dioxide has high resistivity, limited reactivity, diminishes the dangling bond concentration at the surface of Si from  $10^{15}$  to  $10^{10}/\text{cm}^2(17)$  and is a poor diffusion barrier compared to chemical vapor deposited (CVD) SiO<sub>2</sub>. These properties and characteristics help to define the advantages gained and problems encountered when attempting to fabricate a gate with 6 or 7nm of silicon dioxide. SiO<sub>2</sub>, thermally grown in a dry O<sub>2</sub> ambient, diminishes trapping states at the Si surface best and has the lowest trap density within the oxide. The pores provide low resistance leakage current and rapid diffusion pathways through the oxide.

$SiO_2$  is grown on a (1 0 0) Si wafer with a minimum number of electronic defects by heat treatment in a double walled guartz tube furnace containing an O<sub>2</sub> ambient. The free energy of transformation for this oxide is -180kcal/mole at 400°C making it a very stable compound.(20) Oxide grown thermally has the highest surface state reduction at the Si/SiO<sub>2</sub> interface but high diffusion coefficients for metals. A nanometer of the interfacial oxide is reported to be a suboxide where the Si/O ratio approaches 1 for the first few atomic layers. (21-24) Thermal oxide grown with water vapor present in the ambient shows no evidence of pores suggesting that it is a better diffusion barrier than dry ambient thermal oxide.(25) Chemical vapor deposited (CVD) oxide has a poor reduction of surface states but is a good diffusion barrier. CVD and "wet" oxide are not good choices for use as a gate oxide due to a high density of electronic defects that result in a high density of fixed charge, a high polarization field and trapping states. In one study stable high breakdown voltage gates were fabricated by capping the thermal gate oxide with a thin layer of CVD oxide as a diffusion barrier.(18)

The growth mechanism of SiO<sub>2</sub> is of interest in this research because it is controlled by the diffusion of molecular oxygen through the growing SiO<sub>2</sub> which does not react with the migrating O once the thickness reaches 2nm.(26,27,28) The mechanisms of diffusion for O may shed light on the diffusion mechanisms for metals or other constituent elements of the MOSFET that do not react or react weakly with the oxide. The time dependence of oxide thickness was successfully determined in the 1960's with a linear-parabolic function.(29,30,31) The mass transport during initial (0 to 10nm) oxidation is much faster than predicted by Fickian diffusion implying that the oxide is less continuous and contains defects that permit direct or easier access to the Si/SiO<sub>2</sub> interface. This suggests a connected network of pores that provide continuous paths to the interface of lengths equal or near equal to the thickness of the oxide film. The mechanism of oxygen transport to the interface becomes Knudsen-Poiseuille flow in micropores.(32)

(1) dn/dt = kC/L

atoms/cm<sup>2</sup>/sec.

k=constant,

n=number of atoms,

t=time sec.

C=concentration of O<sub>2</sub> at oxide

surface

L= average pore pathway through oxide

The connected pore networks are of a range of lengths and the number of these networks that are continuous from the  $Si/SiO_2$  interface to the outer surface decreases as the oxide becomes thicker and this causes the linear time dependence of oxide growth to become parabolic. Diffusion proceeds by a combination of pore, pore network, vacancy, interstitialcy and interstitial mechanisms. Pore and pore network mechanisms dominate when the thickness of the film is less than 20nm and the film density is low. The density of point defects in the  $SiO_2$  such as vacancies, interstitials and impurities determine the diffusion coefficient for diffusion by the vacancy or interstitial mechanisms.

An alternate description of the SiO2 structure includes the concept of disclinations. In this description the tetrahedra do fill space but these tetrahedra are distorted to varying degrees to accomplish this. This distortion means bond lengths and angles vary from the normal SiO<sub>2</sub> structure. In the (3,3,5) structure 5 tetrahedra with equilateral triangles as faces are common to each These tetrahedra miss filling space by 7.4°. This structure bond. can fill space if bond lengths and angles to nearest neighbors are not the same. This variation from the normal short range order is called disclinations.(33) In this model high diffusion coefficient paths would be in regions with high disclination densities or high strain. If a region has a high concentration of interstitials there will be an increase in the number of strained bonds(disclinations). This strain in the structure is added to the normal strain developed by the inability of the SiO<sub>2</sub> to fill space with undistorted tetrahedra.

Disclinations are a means of describing defects in amorphous materials analogous to dislocations in crystalline material. There is no means at present to measure the magnitude or direction of the strain of disclinations as there is for dislocations.

#### Barrier Layers