## A Comparative Analysis of Static Parallel Schedulers

Where Communication Costs Are Significant

Douglas Michael Pase B.S., Northern Arizona University, 1982

A dissertation submitted to the faculty of the Oregon Graduate Center in partial fulfillment of the requirements for the degree Doctor of Philosophy in Computer Science and Engineering

July, 1989

The dissertation "A Comparative Analysis of Static Parallel Schedulers Where Communication Costs Are Significant" by Douglas Michael Pase has been examined and approved by the following Examination Committee:

> Robert G. Babb II Associate Professor, Thesis Advisor Oregon Graduate Center

> > 11

Michael Wolfe Associate Professor Oregon Graduate Center

Virginia Mary Lo Assistant Professor University of Oregon

Vivek Sarkar Research Staff Member IBM Thomas J. Watson Research Center

# Dedication

To my God, who made this work possible,

To my wife Anne and daughters Kathryn and Kirja,

Who supported me while I did it,

And to my parents, who encouraged me when I was young.

## Acknowledgements

I wish to acknowledge the support and encouragement of the faculty, staff, and students of the Department of Computer Science and Engineering of the Oregon Graduate Center. Their friendship and willingness to listen have been as invaluable as their ideas and enthusiasm. Particularly I would like to thank my advisor, Dr. Robert G. Babb II, and my friend David C. DiNucci for their thoughts and opinions on technical matters, and my committee members for their constructive comments and their patience.

# Table of Contents

.

| 1. Introduction                                       | 1   |

|-------------------------------------------------------|-----|

| 2. Related Work                                       | 8   |

| 3. Definitions And Terminology                        | 15  |

| 4. Scheduler Components                               | 28  |

| 5. Experiment Description                             | 51  |

| 6. Problem Characteristics and Scheduler Performance  | 58  |

| 7. Comparison of Schedulers                           | 76  |

| 8. Conclusions                                        | 94  |

| 9. Future Work                                        | 101 |

| Appendices:                                           |     |

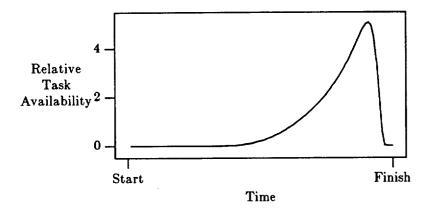

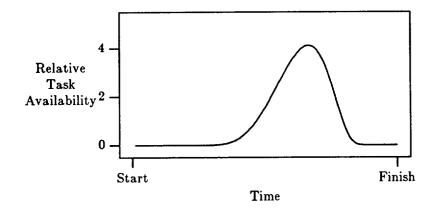

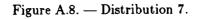

| A. Task Density Functions                             | 106 |

| B. Scheduler Performance Characteristics              | 110 |

| C. Comparison of Schedulers By Problem Characteristic | 172 |

| D. Relative Efficiencies of Schedulers                | 209 |

| E. Cumulative Histograms of Relative Performance      | 222 |

| References                                            | 246 |

## Abstract

A Comparative Analysis of Static Parallel Schedulers

Where Communication Costs Are Significant

Douglas M. Pase, Ph.D.

Oregon Graduate Center, 1989

Supervising Professor: Robert G. Babb II

Efficient multiprocessor scheduling where communication between processors is free has been studied for almost three decades. However, modern distributed architectures have communication channels for which communication is *not* free. Such channels have a nonzero latency and a finite capacity for communication. Previous work on parallel scheduling accounting for communication effects has assumed that the channels had sufficient capacity to service all transmissions without significant delay from contention. We show that the average schedule length can be significantly shortened by taking contention into account. We define families of static schedulers based on the strategy chosen for various phases, and present a performance analysis based on that classification. Because certain static schedulers are equivalent to dynamic schedulers for which perfect knowledge is available, parts of this work also apply to dynamic scheduling.

## CHAPTER 1

#### Introduction

#### 1.1. Background

Since the inception of modern mechanized computing a particular theme has occurred many times — how do we solve a given problem faster? This pursuit of greater speed has led to the development of better algorithms, more effective compiler optimization techniques, and faster hardware. Speeding up the hardware could mean improving the speed of a single processor, or it could mean replicating the processors and dividing the problem into smaller units (or tasks) which are then executed in parallel.

A particularly difficult part of executing tasks in parallel is arranging the execution of individual tasks so that the maximum benefit is gained from all the effort. It is easy to see that when there is no additional cost for executing tasks in parallel, doing so will never slow the computation down. However, when parallel execution incurs an additional expense, such as from communication, improper scheduling can actually lead to *slower* program execution.

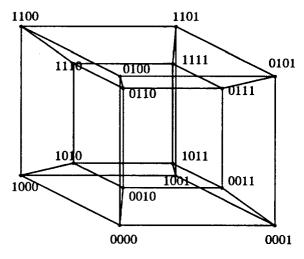

A number of approaches have been proposed to solve the problem of multiprocessor scheduling considering communication costs. Among them are processor allocation, dynamic load balancing, and static scheduling. Processor allocation problems generally take the form of mapping a program graph  $G_p = (V_p, E_p)$  to a network of processors  $G_n = (V_n, E_n)$ such that some criterion is minimized [BeS87,Bok81a,Bok81b].  $V_p$  is the set of vertices (tasks) in the program, and  $E_p$  is the set of edges (communication arcs). Similarly,  $V_n$  is the set of processors in the network, and  $E_n$  is the set of communication links which connect the processors. It is called the *mapping problem* if the objective is to minimize the number of arcs in  $G_n$  spanned by arcs in  $G_p$ . This assumes that all communication is of equal cost, and the value to be minimized is the distance over which each message must travel. It also assumes that only one task may be mapped to a processor.

Another problem related to processor assignment is called the quadratic assignment problem [Bok81a]. In this case there are n objects and n locations. The affinity between objects is recorded in a matrix A, and distances are recorded in a matrix D. The element  $a_{ij}$  records the affinity between objects i and j, and element  $d_{ij}$  records the distance between locations i and j. The objective is to find a mapping function  $p:V_p \rightarrow V_n$  such that the overall cost of communication,  $\sum_{i,j} a_{ij} d_{p(i)p(j)}$ , is minimized. The affinity between two objects can be thought of as a volume of communication between two tasks. A distance  $d_{ij}$ can be thought of as the the cost of communicating between processors i and j.

Dynamic load balancing deals with communication on an indirect level. As work becomes available, it is shipped to the processor which is best able to accept it [Cas87,Ham80,Sta84]. If a task has not received all of its input, it is not ready to be shipped. This is much like the "macro dataflow" model used in [SaH86,Sar87]. Processor selection is deferred until the task can be executed, and the best processor is selected at that moment. Processors are not left idle as long as work is available. A particularly important advantage to this approach is that the schedule adapts itself to the execution of the program as the execution takes place. Thus even programs whose execution are extremely data dependent can use this method of scheduling.

Dynamic load balancing approaches are generally classified as centralized or decentralized. Centralized load balancing has one processor (the master) which is responsible for all scheduling decisions. It tracks the work levels of all processors within the system, and supplies tasks whenever they are available to processors (workers) that need them. As tasks are completed the worker informs the master who collects and records the information. When all of a task's inputs are available, the master places the task on a ready queue, or assigns it to a worker. Although this approach is simple and effective for small numbers of processors, it does not scale well. Loading of the master is proportional to the number of the processors in the system, so increasing the network size will eventually cause it to be saturated. In addition, as networks get larger there is an increase in the communication delay between the more distant processors and the master, which causes additional processors to be less effective.

Distributed load balancing attempts to remedy these problems by making decisions locally. This means that the ability to make decisions increases with network size. It also means that the distance between the unit which makes the decisions and the unit which executes those decisions is zero. However, because each processor must make decisions about whether to accept or forward tasks, and where, each processor must now have some idea of the system state. The system state must itself be communicated through messages which are subject to communication delay, so they may not reflect that state accurately when they are received or used.

Both centralized and distributed load balancing suffer somewhat from the fact that scheduling is done at runtime, and therefore the scheduling overhead is paid for every time a program is run. Little pre-execution program analysis is normally done to aid the scheduler in making its decisions, which prevents processors from planning the execution to minimize the overall processing time.

Static scheduling attempts to solve some of these problems by analyzing the program graph and scheduling it before execution begins. This is necessarily restricted to programs or sections of programs which have little varying dynamic behavior. Our approach to static scheduling further restricts the problem to the scheduling of tasks with acyclic precedence constraints and heterogeneous task and communication weights. It is a superset of the *Precedence Constrained Scheduling Problem* (PCS) [GaJ79], in that it adds to PCS the additional problem of scheduling communication costs. In both problems the tasks have a finite lifetime and are executed once. All incoming communication must be received before a task may begin, and all outgoing transmissions are sent after the task has completed.

Because the problem in its general form is NP-complete [Ull75], solution approaches have taken two diverging paths, namely that of restricting the problem until polynomial solutions may be found, and of finding heuristic algorithms that may be computed more cheaply but still produce schedules that are frequently close to optimal.

Static scheduling may be done as the program is constructed, as a preprocessing phase prior to compilation, automatically or semi-automatically at compile time, or at the time the program is loaded onto the machine for execution. Tasks may represent individual instructions in a program, subroutines, program modules, or whole programs which are part of a script. Communication between these tasks might be the fetch of a datum from main memory, a structured message a few hundred or thousand bytes long, or the transfer of complete files between successive filters. We assume here that the only cost associated with communication is the message transmission time, which includes both the time required to transmit the message over the communication link, and the queuing delay which occurs because of competition from other messages in the system. No setup time in sending or receiving messages is included in this analysis, although there is no reason why it could not have been.

A scheduler is preemptive if execution of a given task may be interrupted and suspended to allow another task to execute. It is nonpreemptive if the reverse is true, that is, once a given task is started it runs to completion without interruption.

Scheduling strategies may be further subdivided into optimal and heuristic approaches. Optimal schedulers may use branch-and-bound techniques [KaN84,Koh75] or linear, integer, or dynamic programming [ACD74,LaL78]. These approaches produce schedules from the equivalence class of shortest length schedules (there may be more than one possible shortest schedule), but the schedulers can require running times which are exponential in the number of tasks to be scheduled.

Heuristic schedulers are more difficult to classify because of the great diversity in approaches. However, a distinction can be made between *stubborn* and *non-stubborn* schedulers. A stubborn scheduler will not move or attempt to reschedule a task once it has been scheduled. Non-stubborn schedulers will generate an initial task schedule, then perturb it in different ways hoping to find a better schedule. *List* schedulers are a special class of stubborn schedulers. In this dissertation, a taxonomy of schedulers is developed and the performance of different types is considered.

#### 1.2. Contributions of This Dissertation

This dissertation makes the following specific contributions to the study of parallel scheduling:

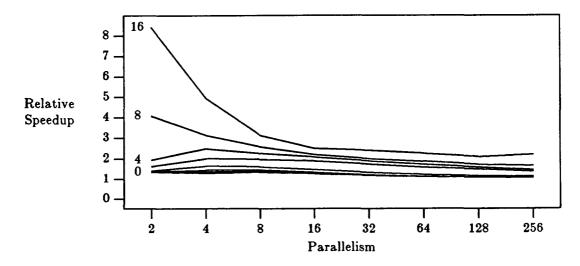

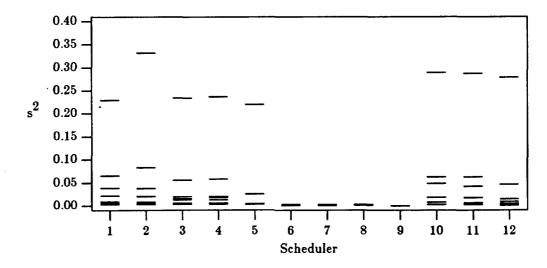

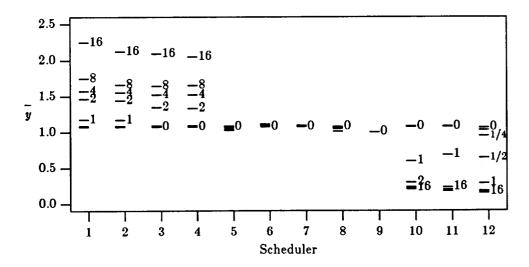

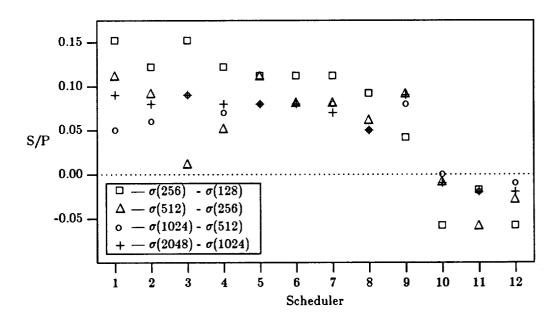

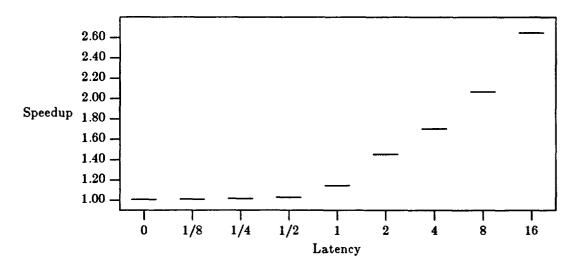

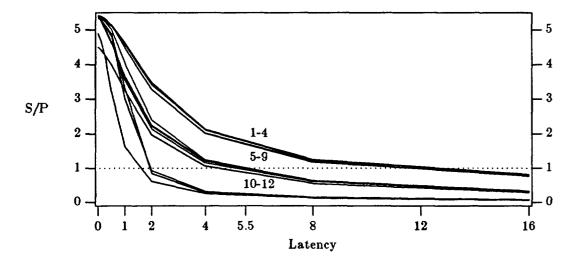

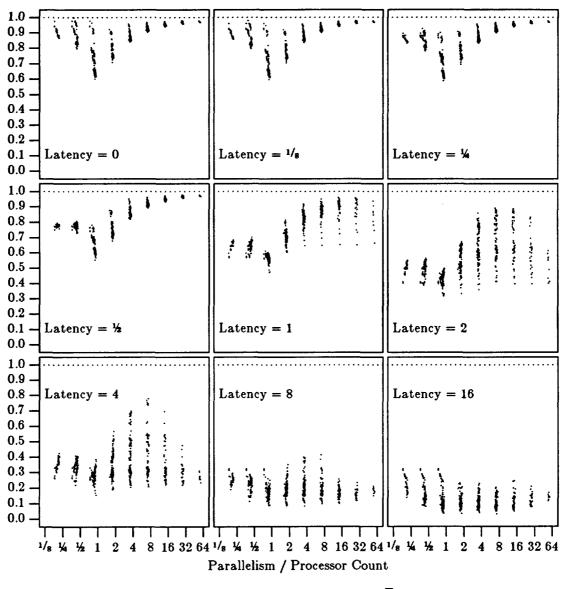

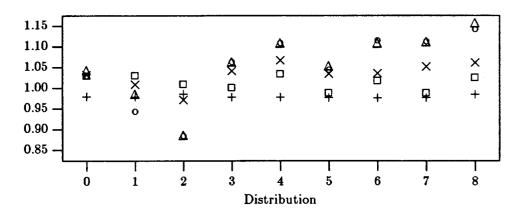

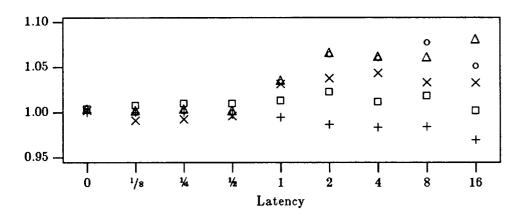

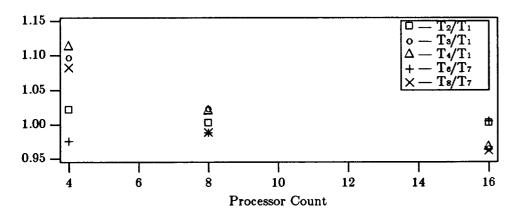

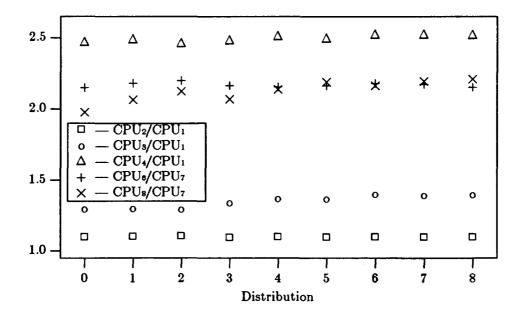

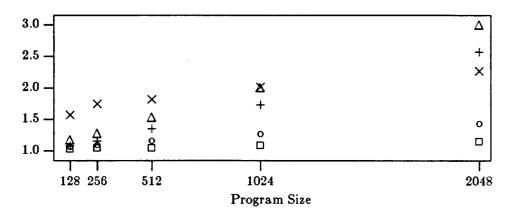

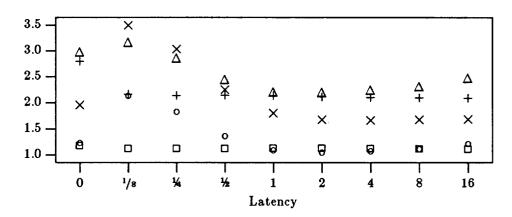

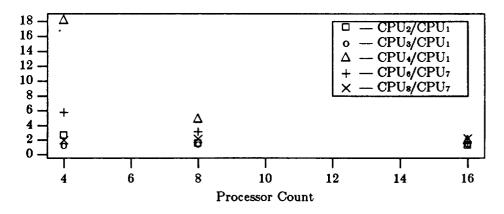

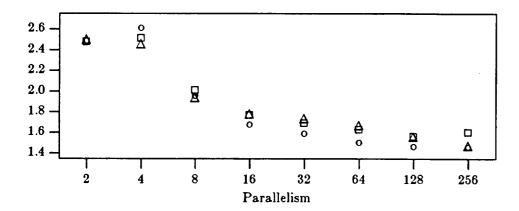

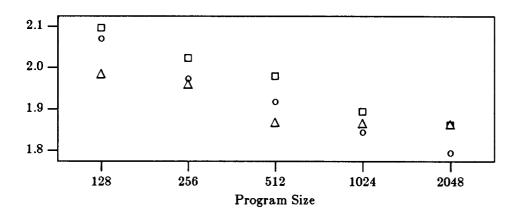

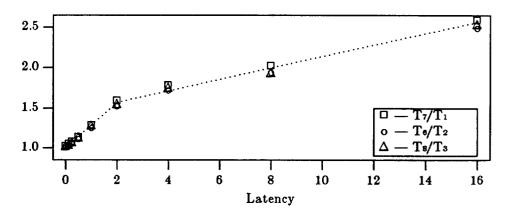

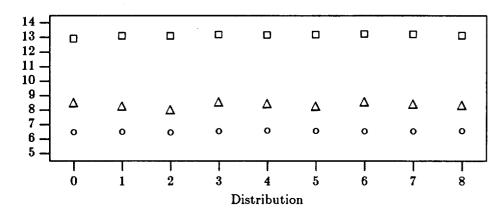

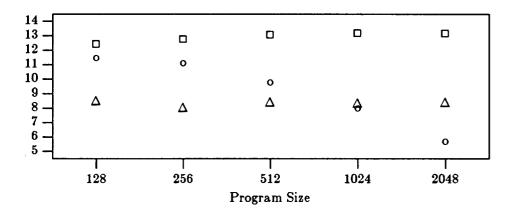

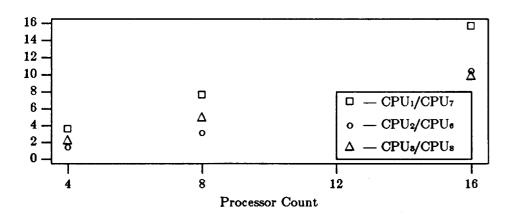

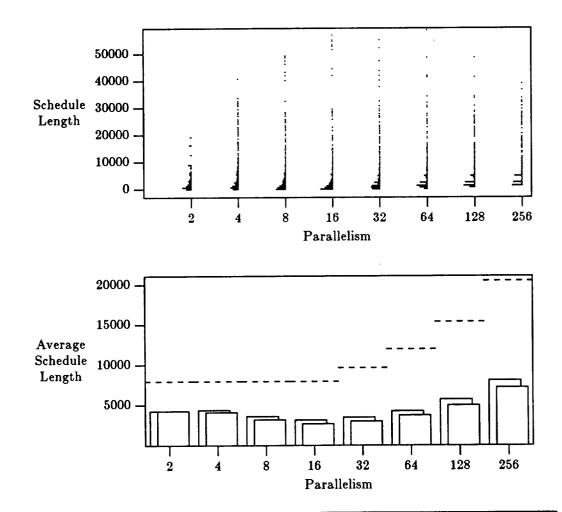

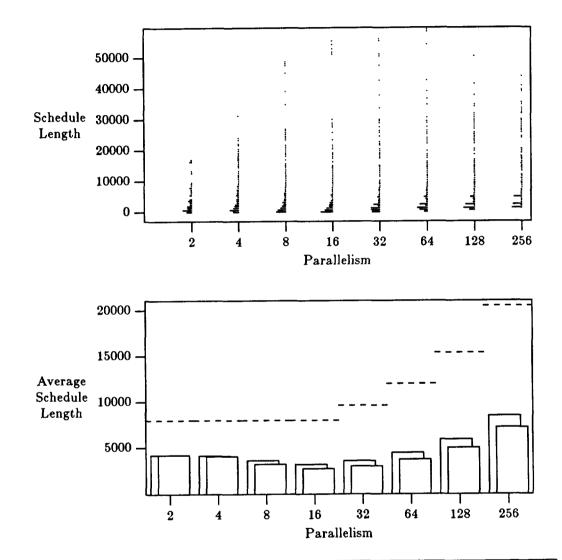

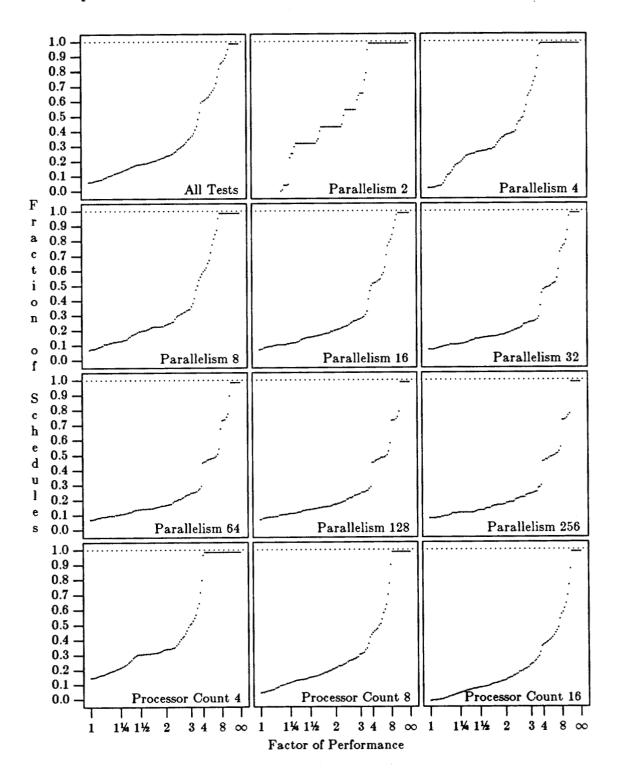

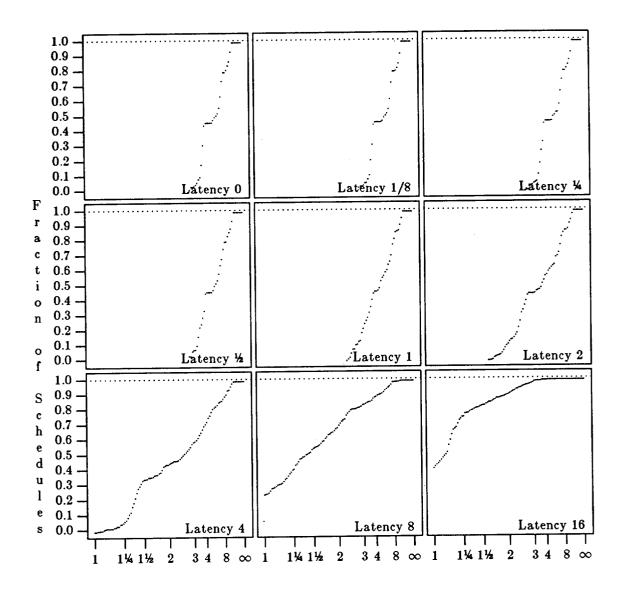

- (1) We examine five variables in the program/architecture system for their effect on scheduler performance. The program variables are: the distribution of tasks within a program, the number of subtasks within a program, and the average parallelism. The architecture variables are: the average time (latency) required to communicate over empty links and the total number of processors available.

- (2) We decompose static parallel scheduler algorithms into three basic parts and examine how different designs for the parts affect scheduler performance. The

subdivisions we consider are: task selection, processor selection, and schedule generation. The task selection strategies we consider include those used in critical path scheduling and in diffusion dynamic load balancing. Processor selection includes strategies where only processor load is considered, where processor load and empty channel communication latency are considered, and where load, latency, and contention are considered.

(3) Several of the static schedulers we examine resemble dynamic (diffusion type) load balancing schedulers. The static schedulers are similar in all important respects except (1) there was no runtime overhead for scheduling, and (2) the static scheduler has complete and accurate information about the entire system at each time a decision about task placement is made. As such the static schedulers delineate the best average performance that could be expected from similar dynamic schedulers.

#### 1.3. Dissertation Outline

The remainder of this dissertation is organized as follows:

Chapter 2 summarizes much of the relevant work which has been done in static scheduling, and particularly in list scheduling. In Chapter 3 we present a precise definition of the multiprocessor scheduling problem. Chapter 4 describes a taxonomy of our 12 schedulers based on their modular decomposition. The construction of each of the 12 schedulers used in later chapters is also given, along with a worst case complexity analysis for each.

A complete description of the scheduler experiment setup, inputs, and environment is given in Chapter 5. We describe the five variables considered to be most relevant to scheduler performance, and the range of values used for each. Chapter 6 analyzes the

6

effects of each experimental variable on scheduler performance. Chapter 7 analyzes the effects of variables used in scheduler construction on scheduler performance. Our conclusions and recommendations are presented in Chapter 8, and Chapter 9 presents some ways in which this work might be extended.

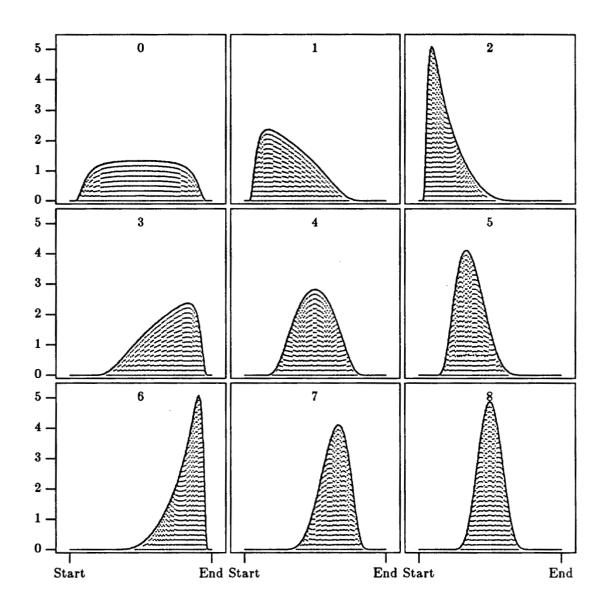

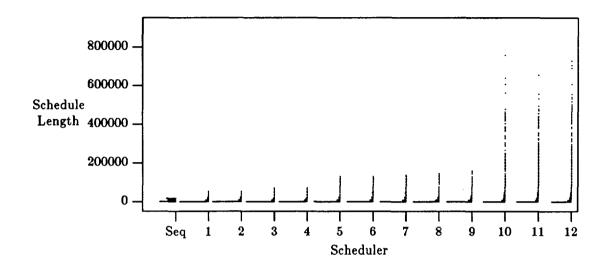

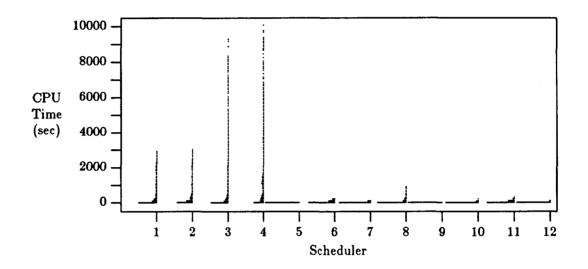

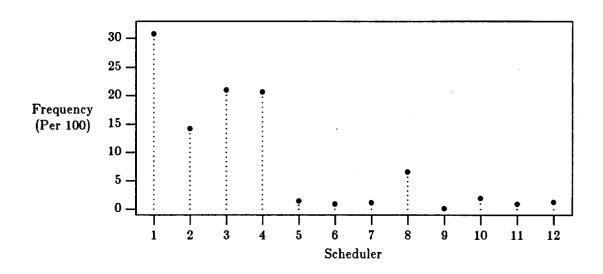

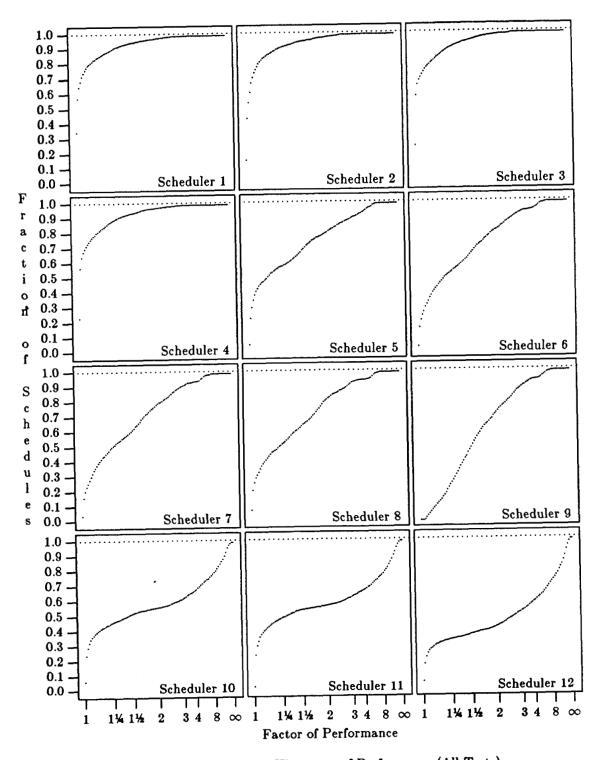

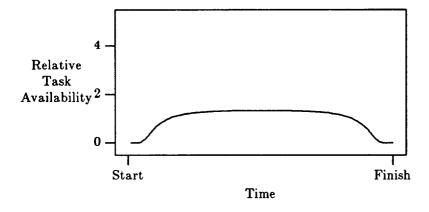

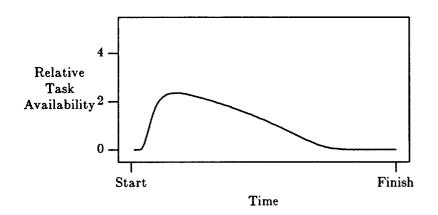

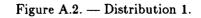

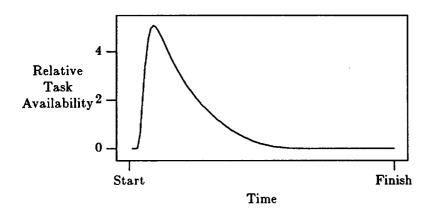

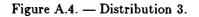

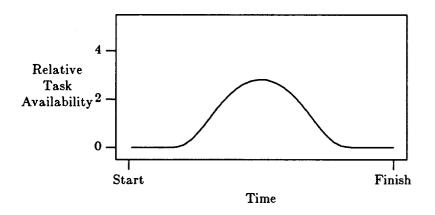

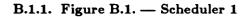

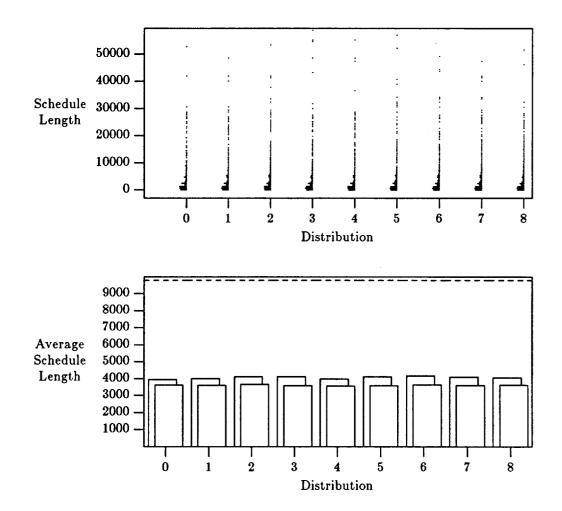

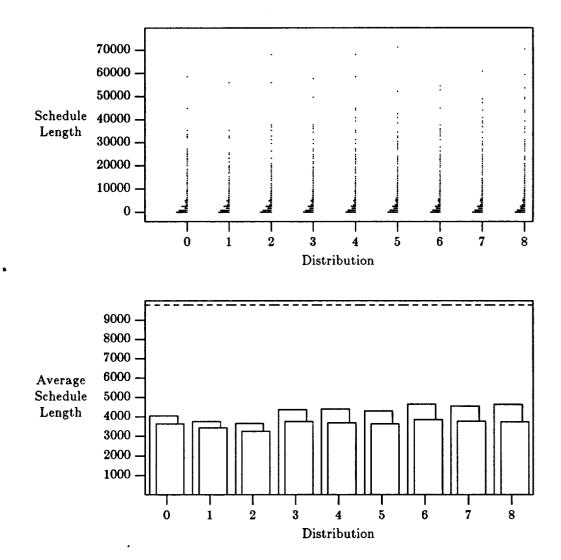

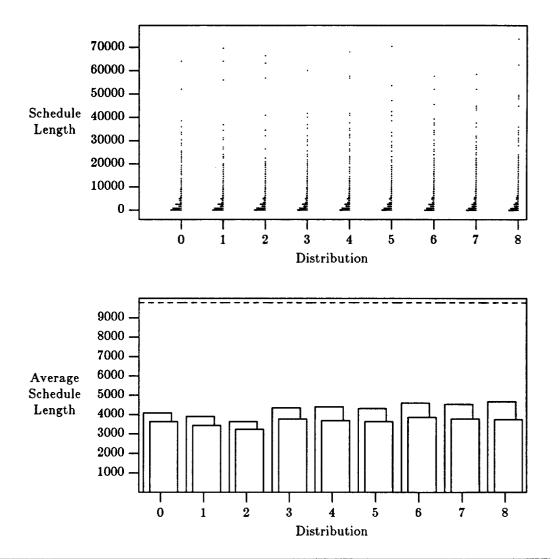

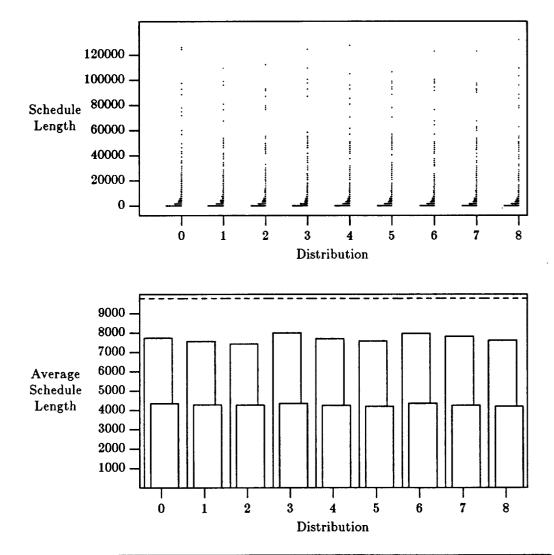

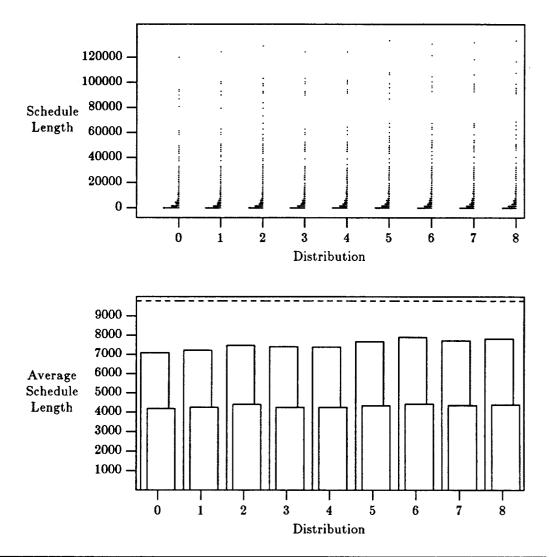

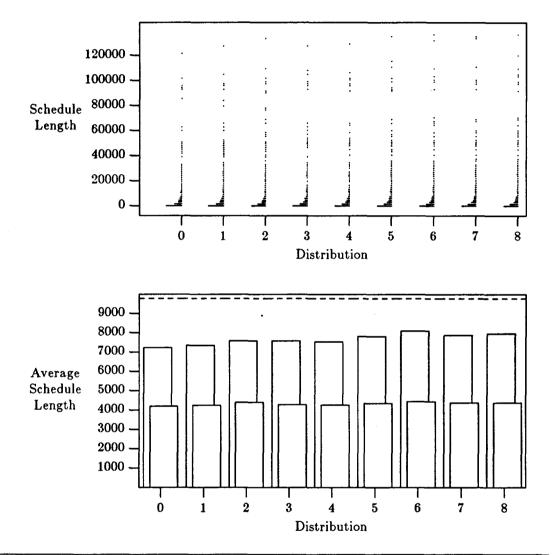

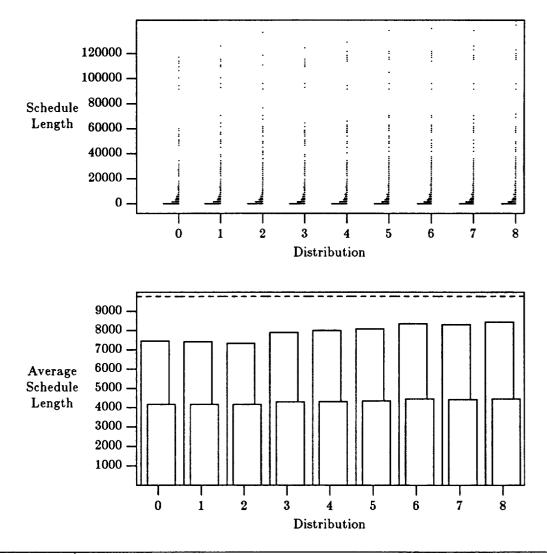

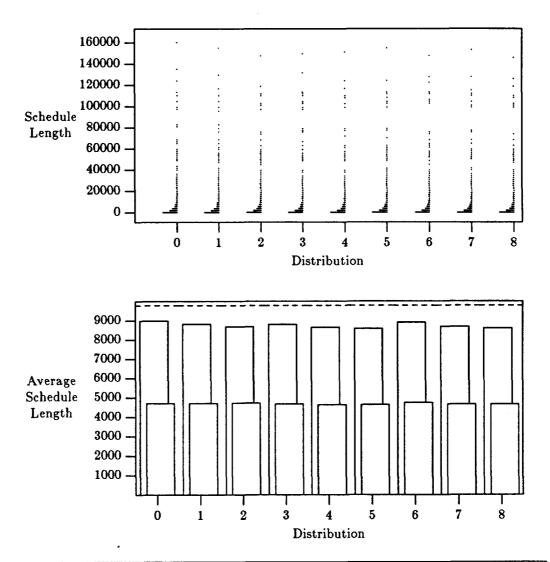

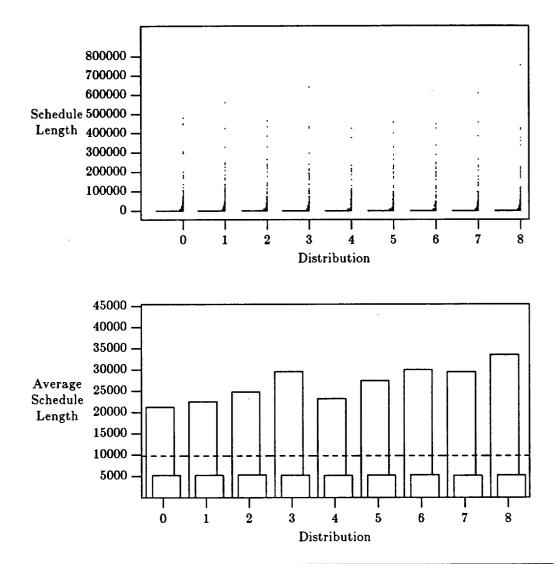

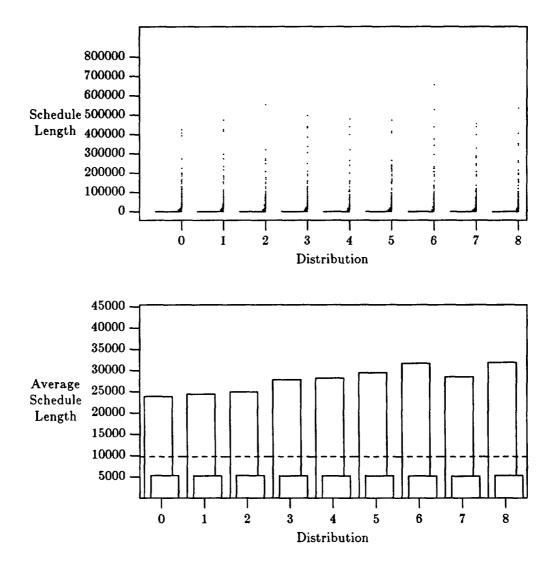

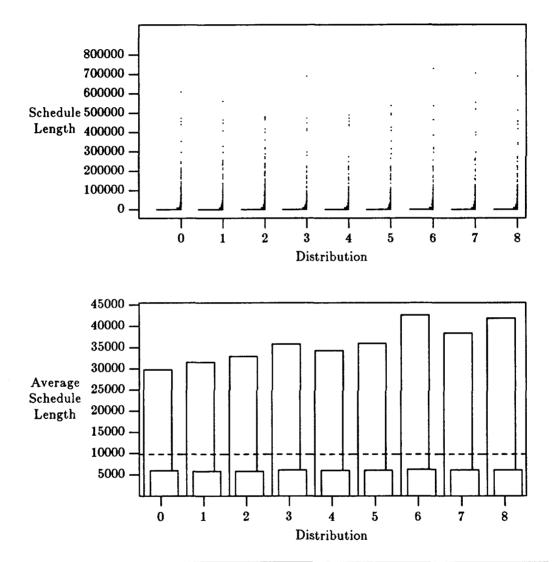

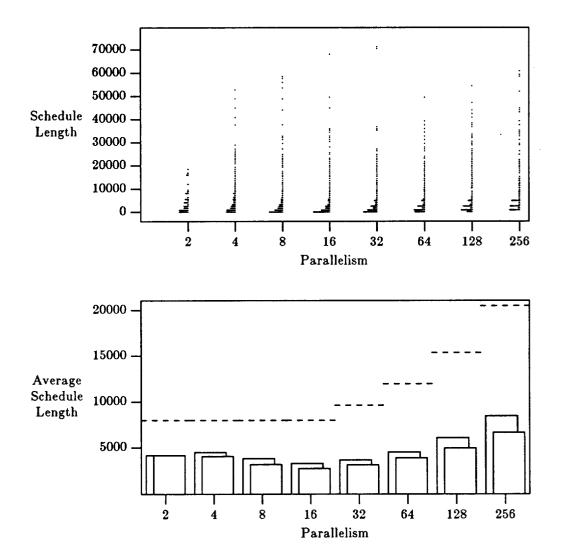

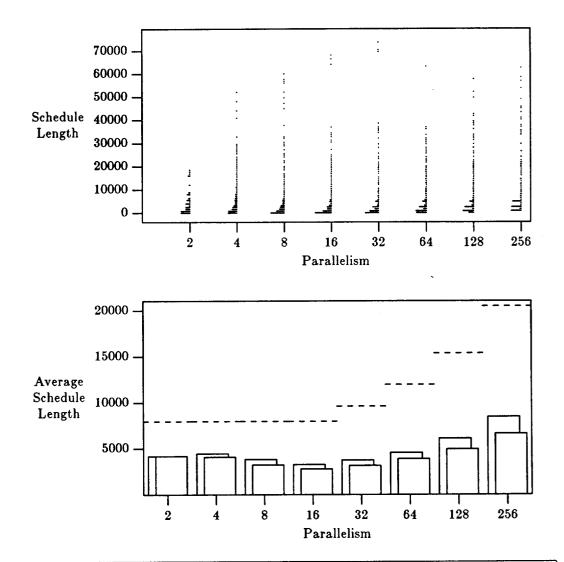

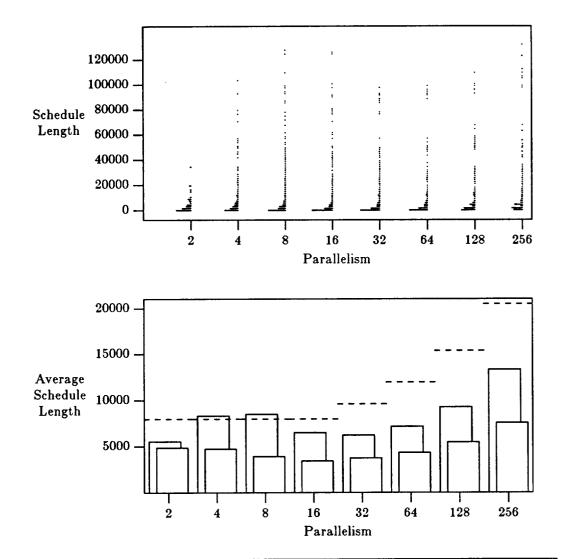

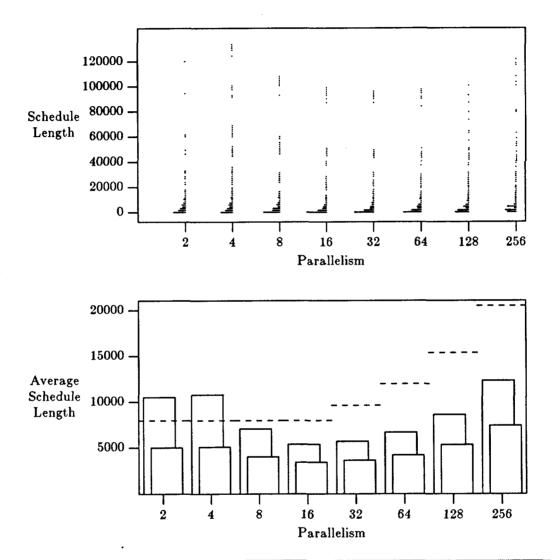

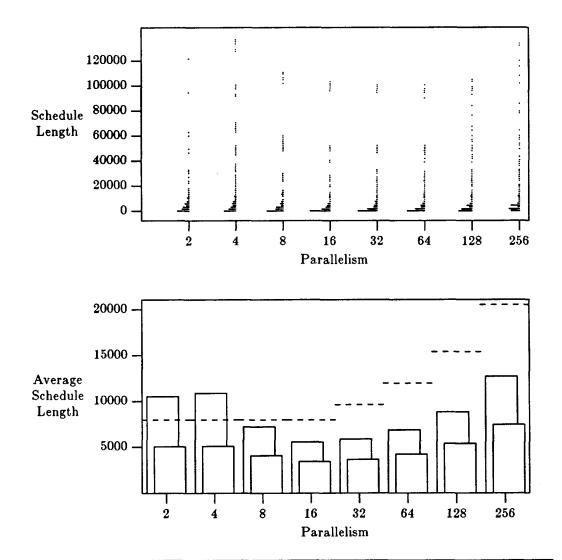

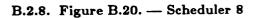

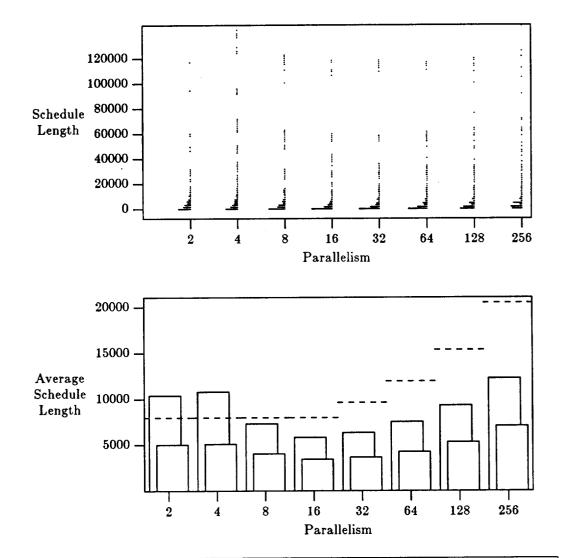

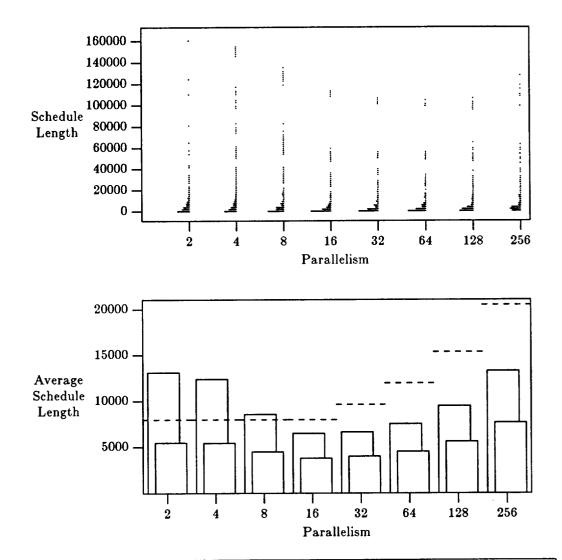

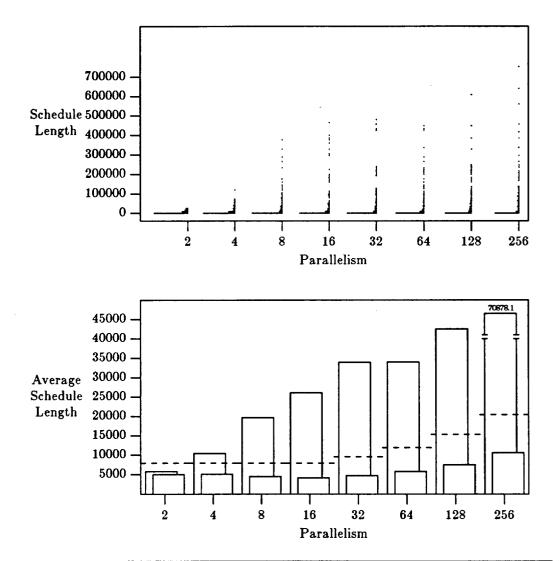

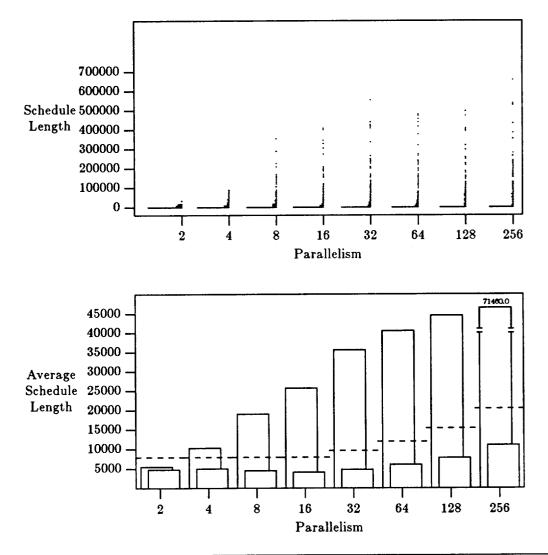

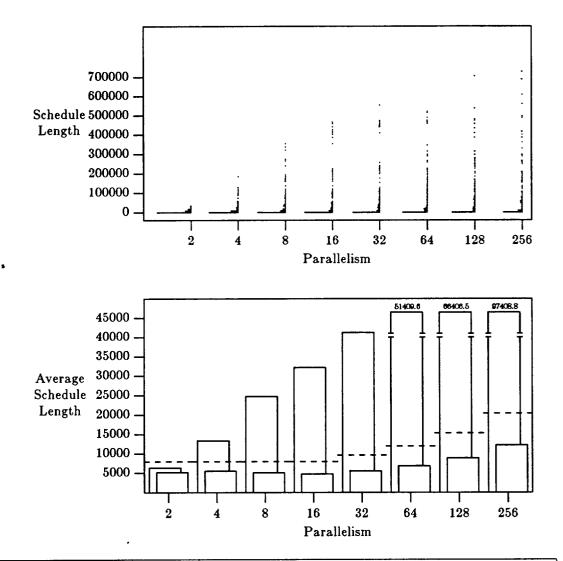

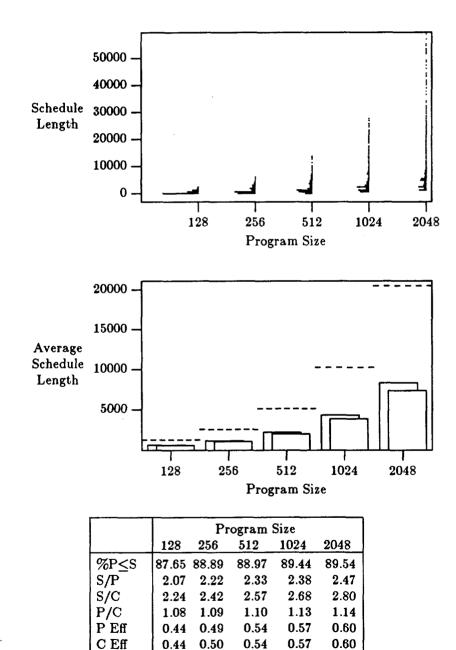

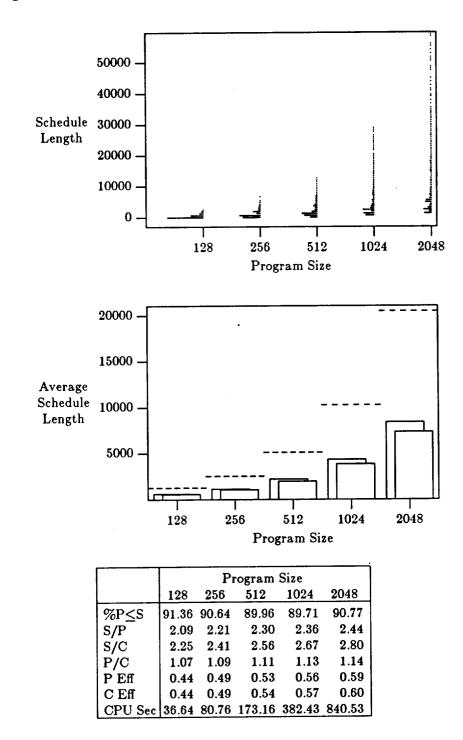

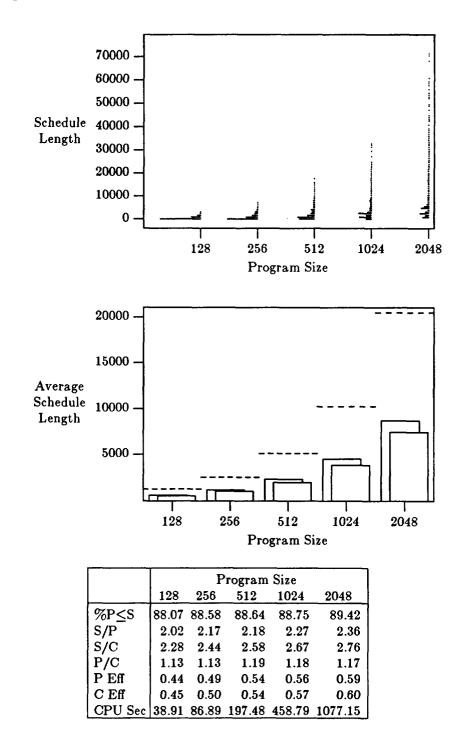

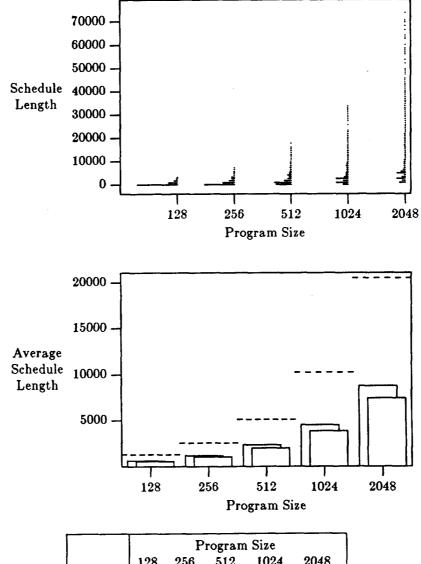

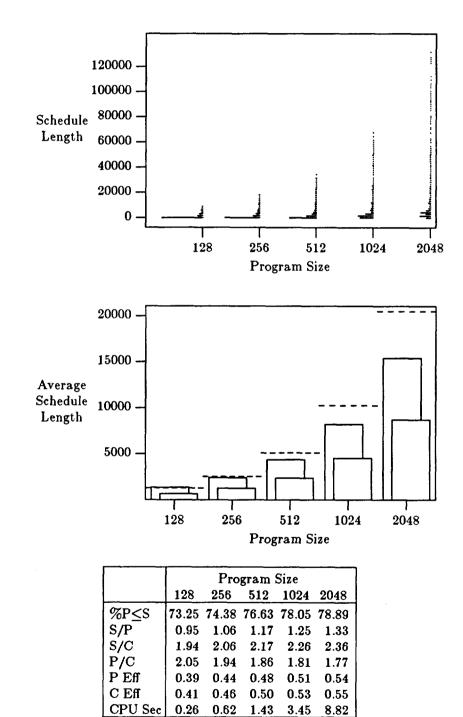

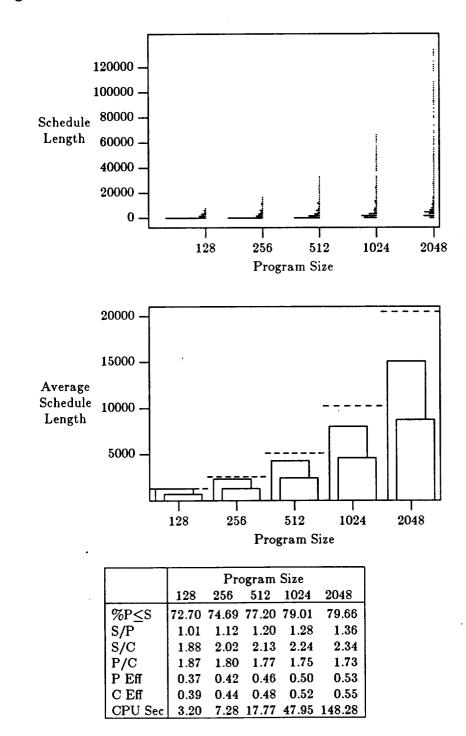

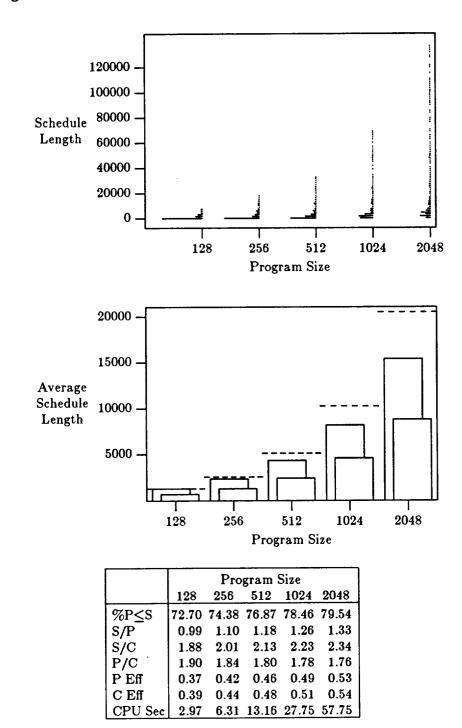

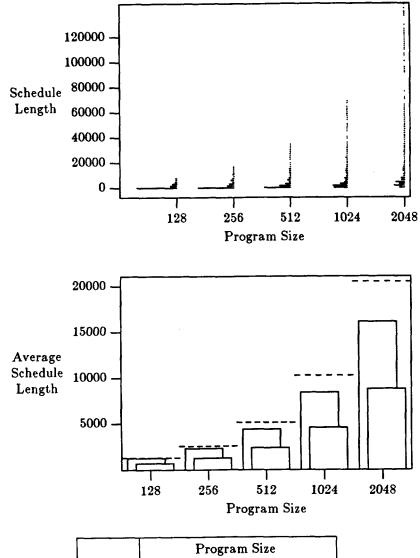

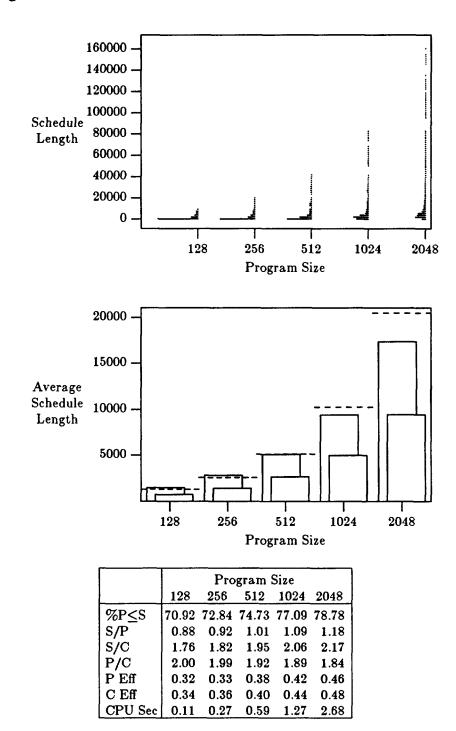

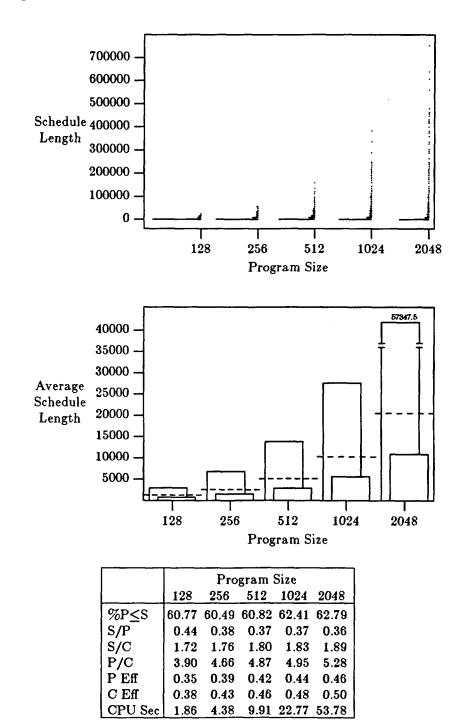

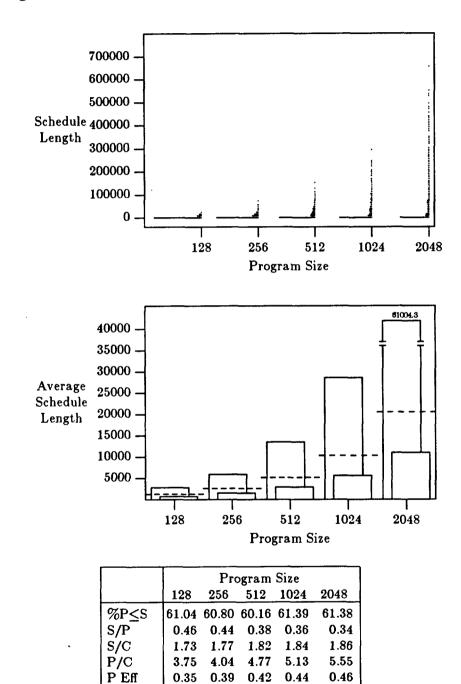

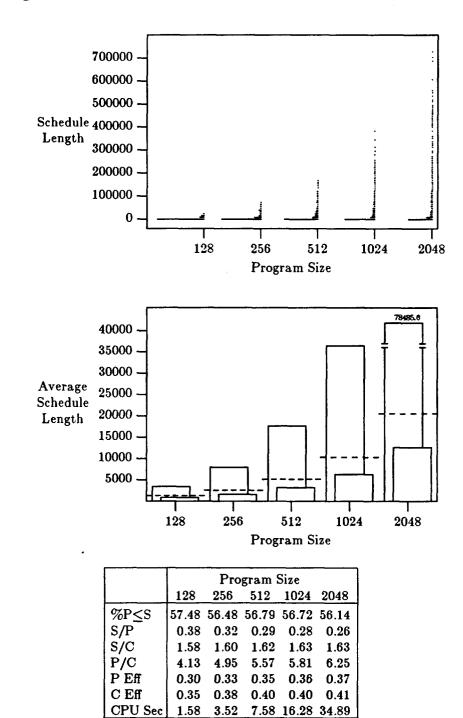

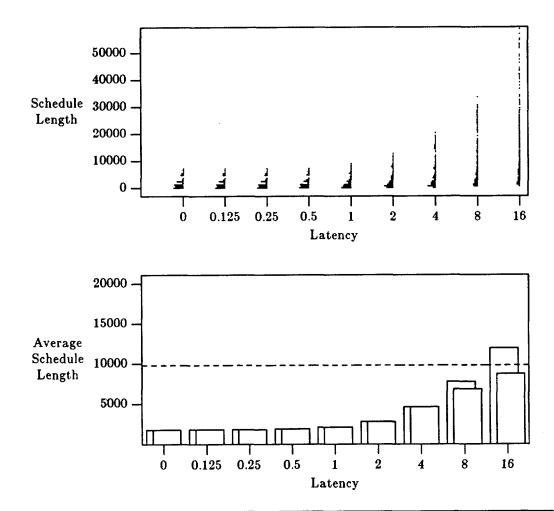

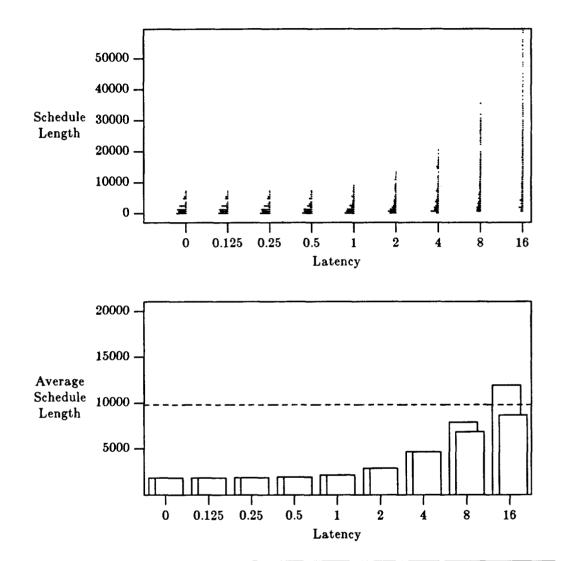

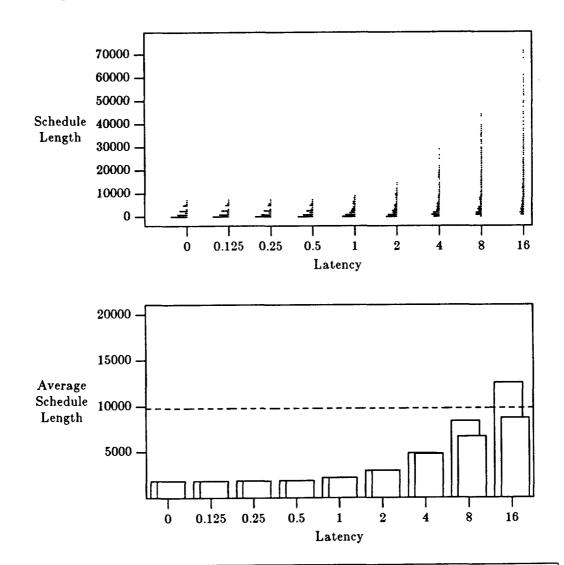

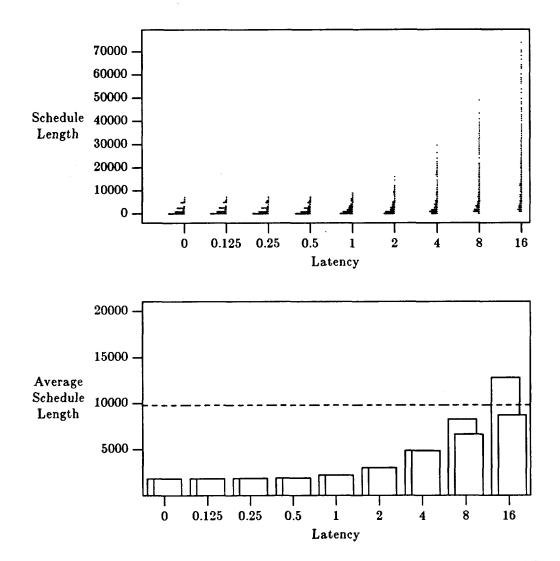

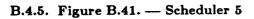

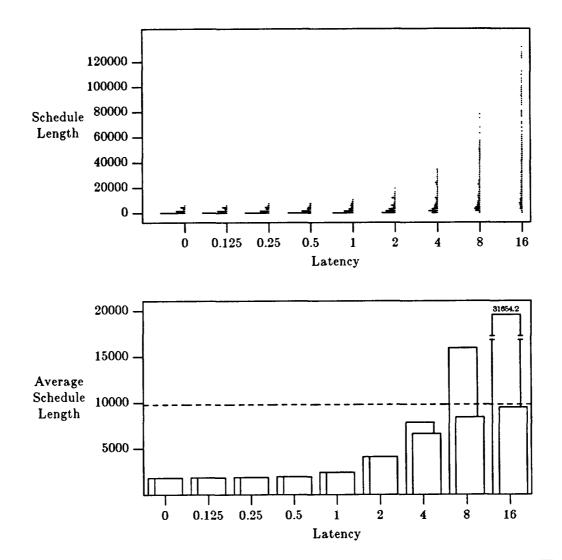

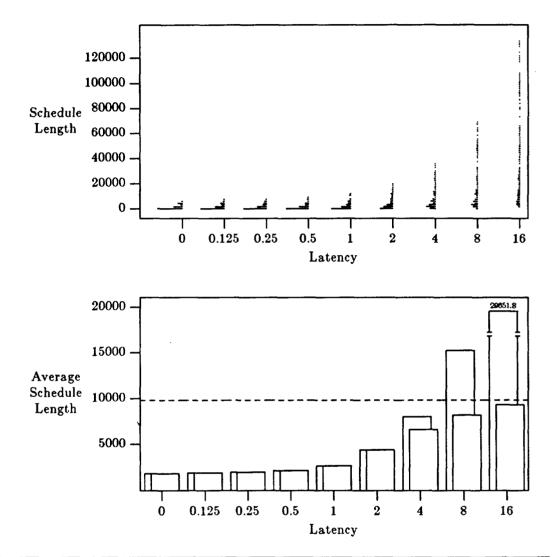

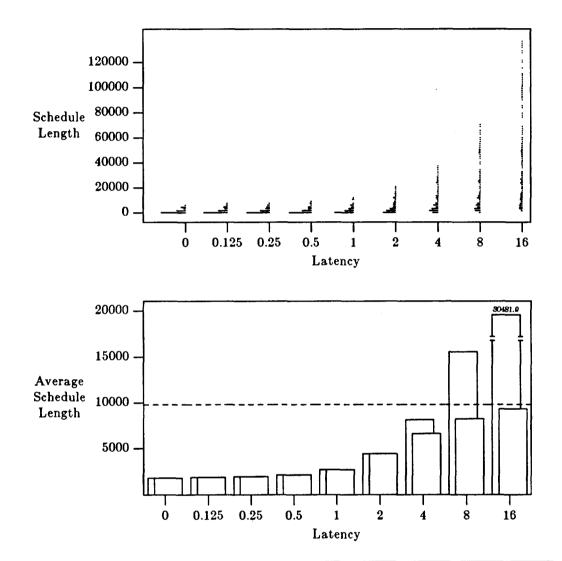

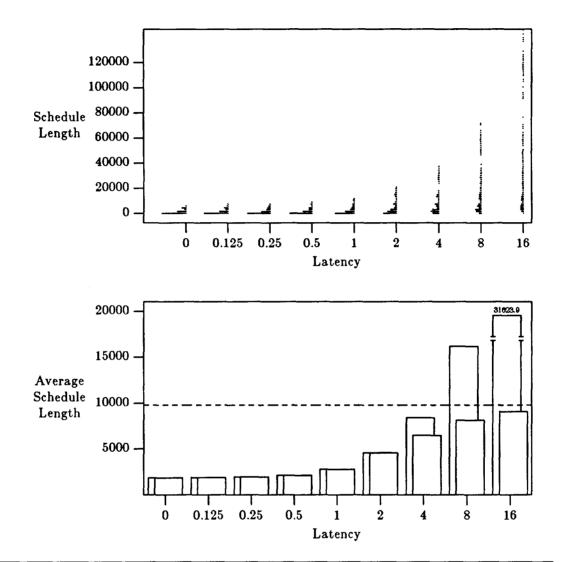

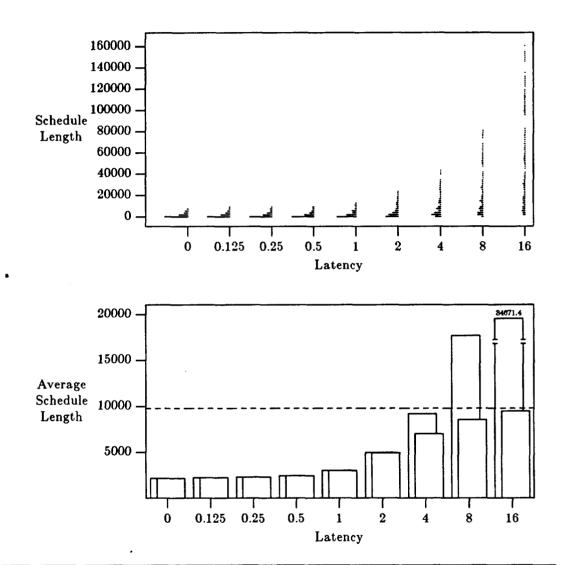

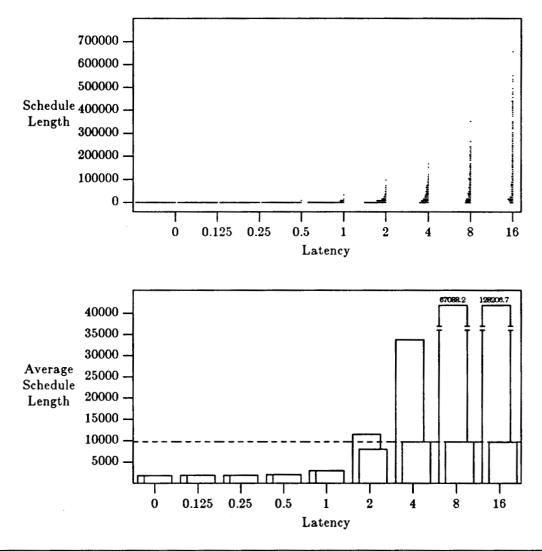

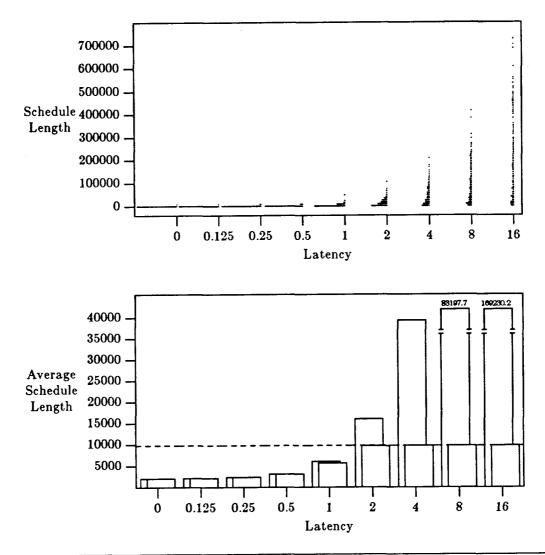

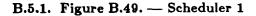

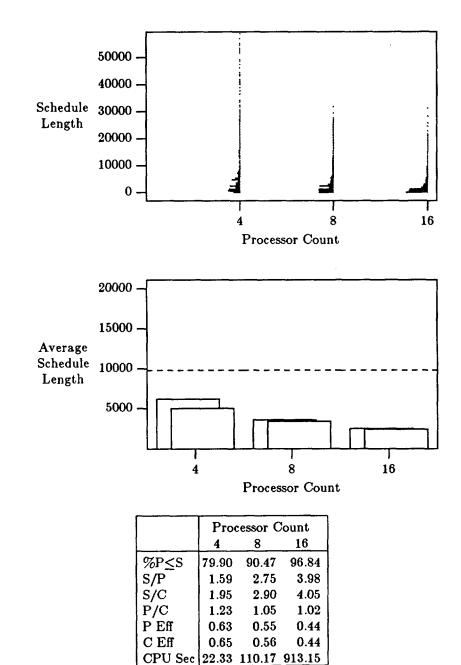

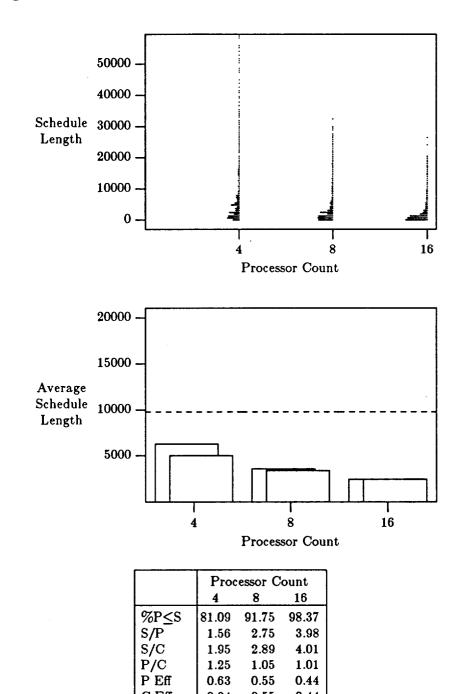

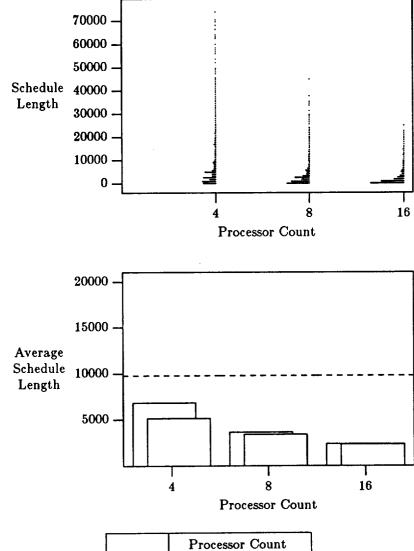

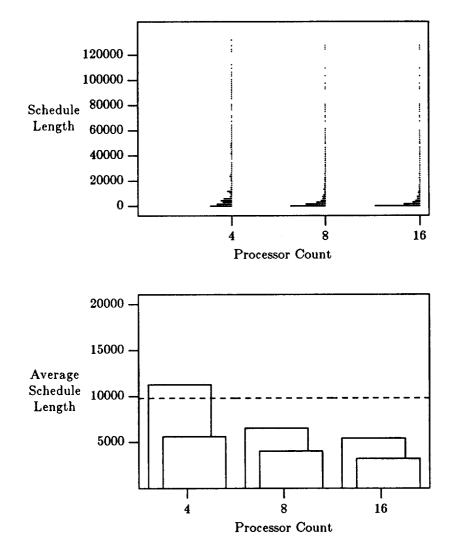

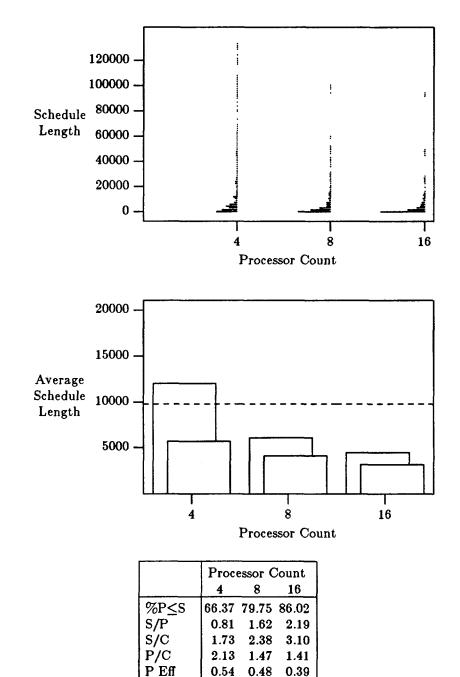

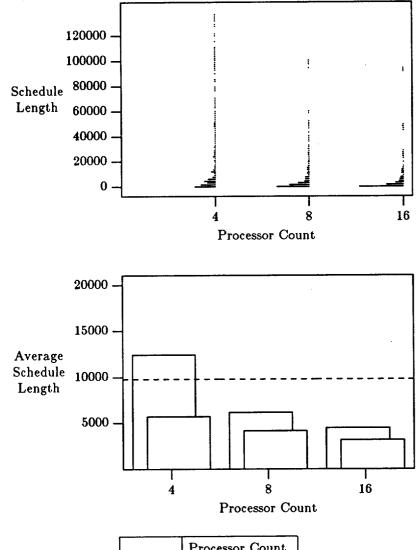

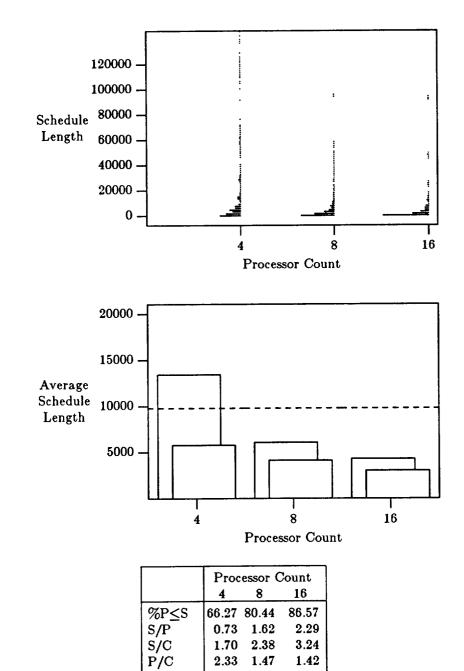

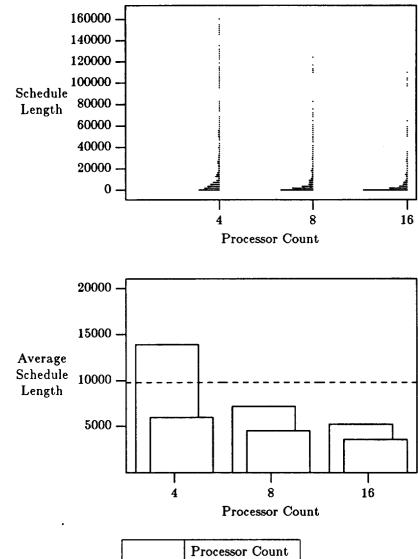

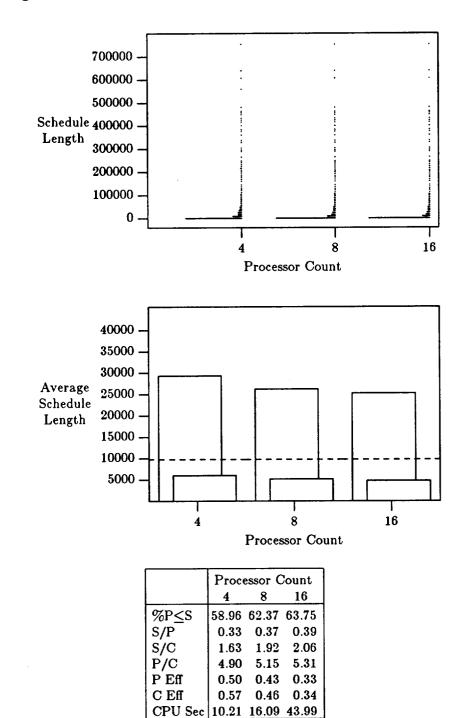

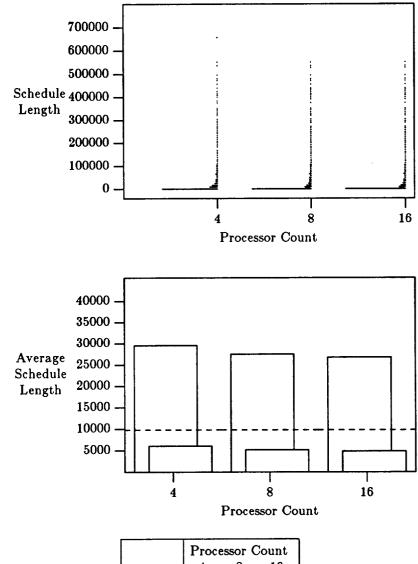

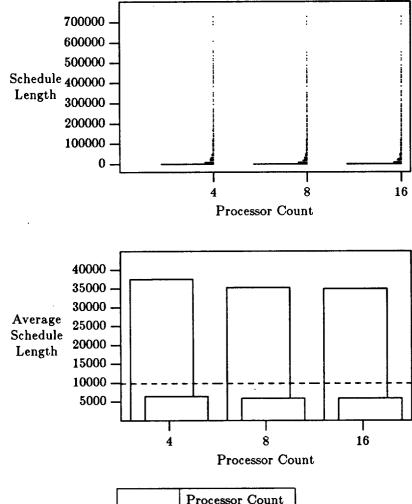

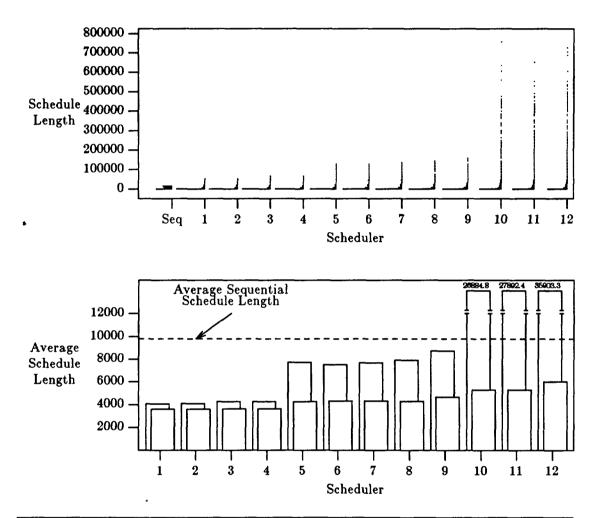

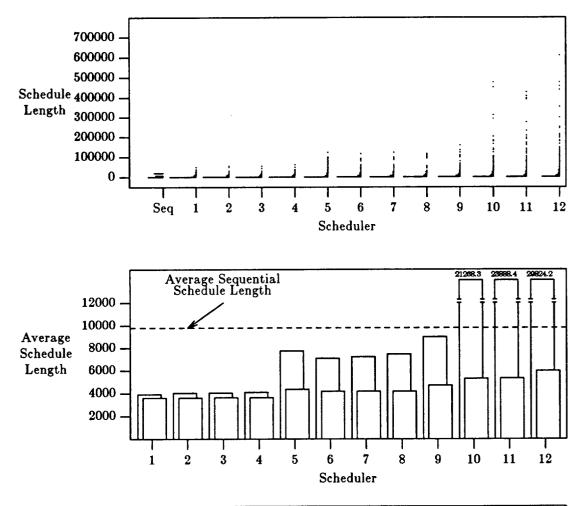

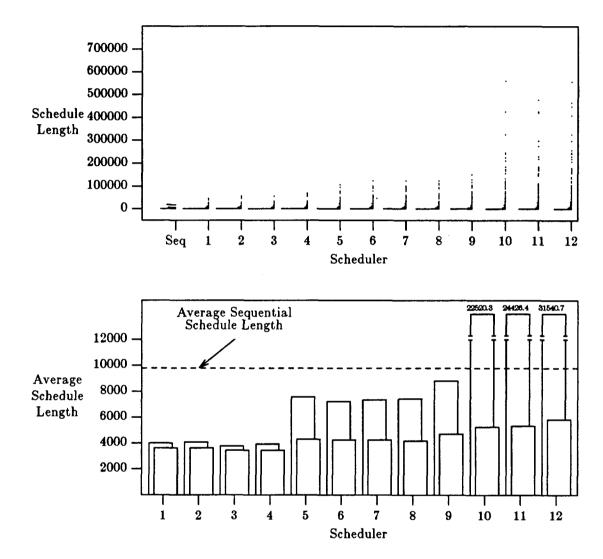

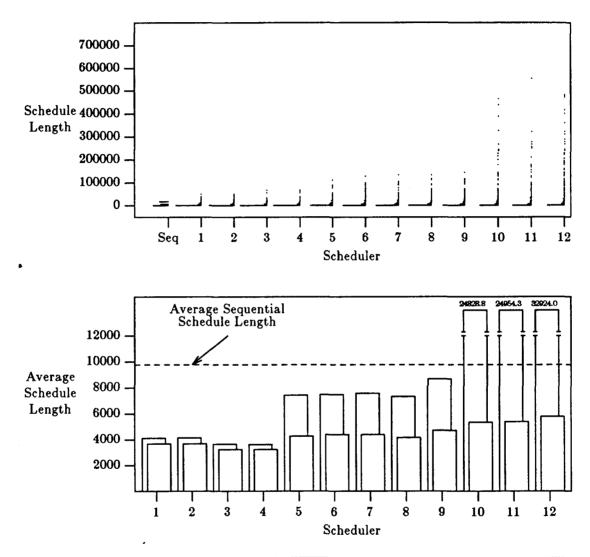

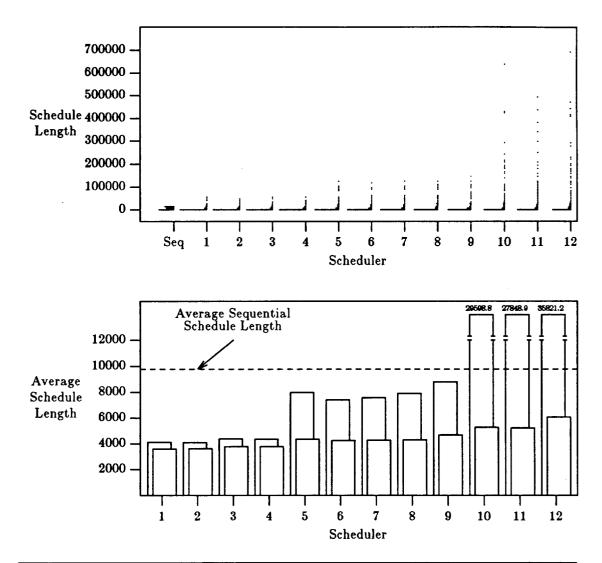

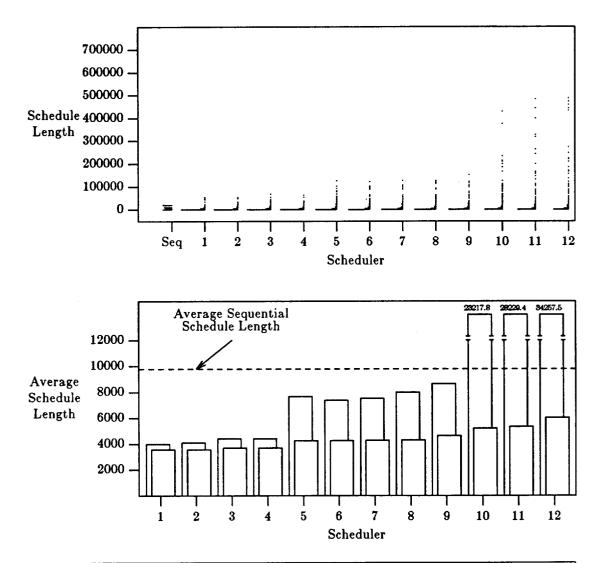

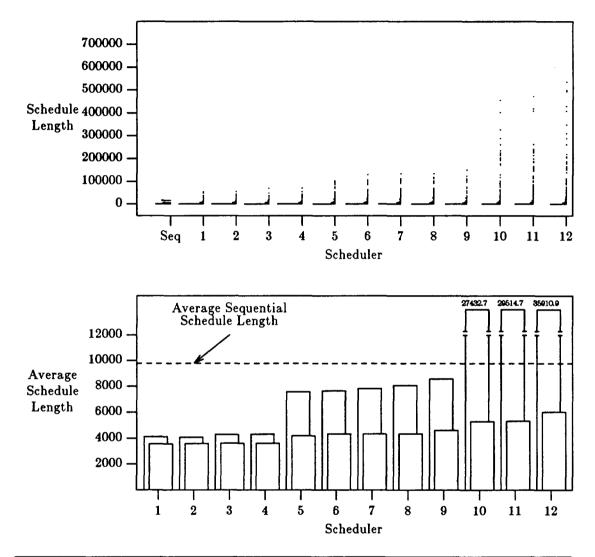

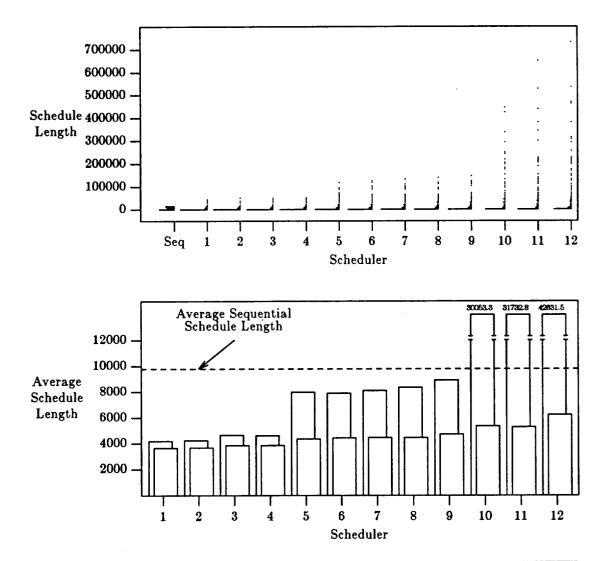

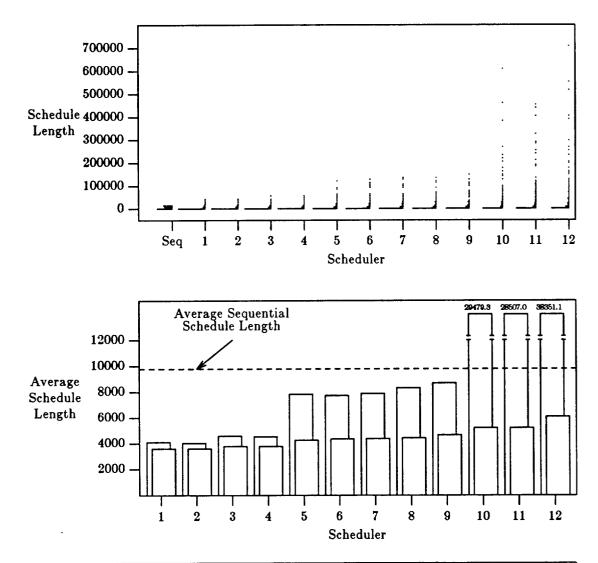

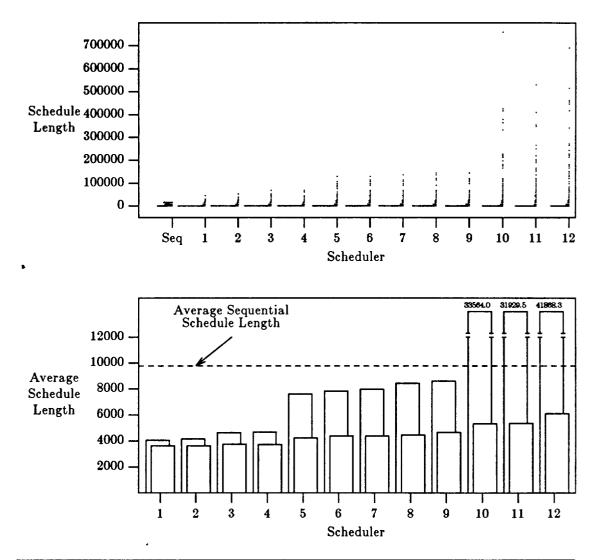

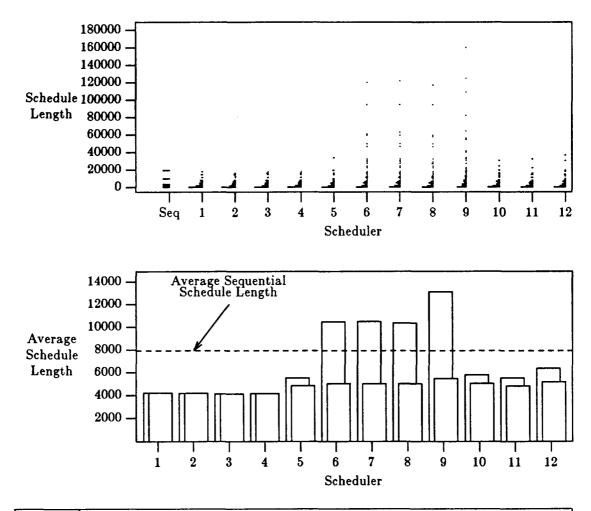

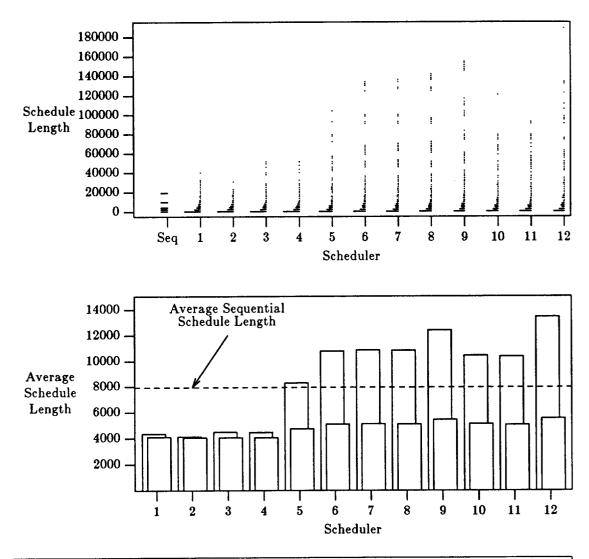

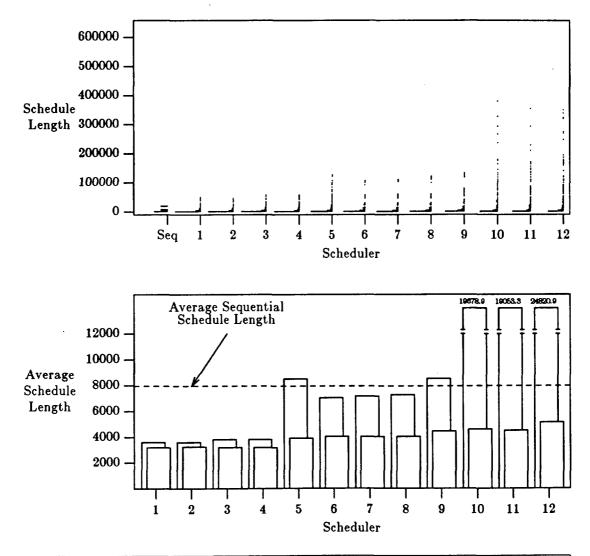

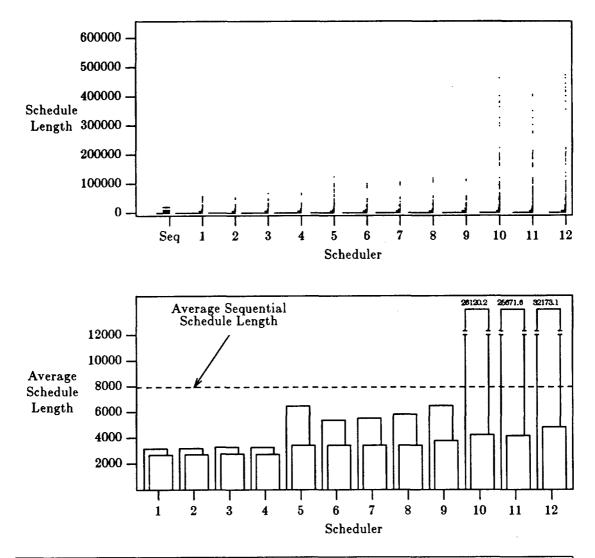

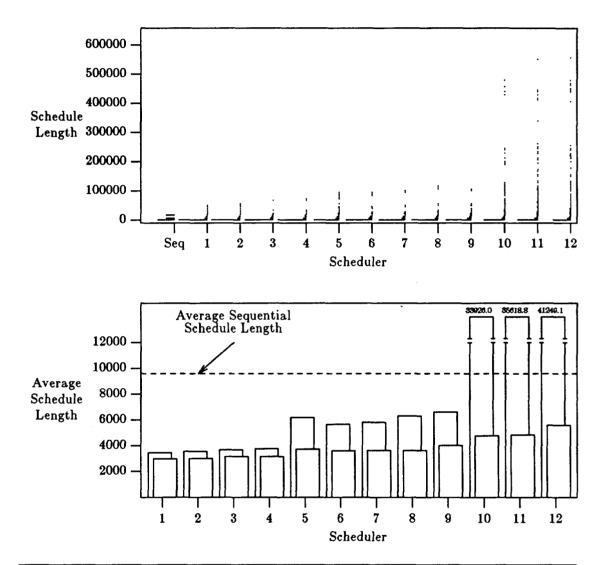

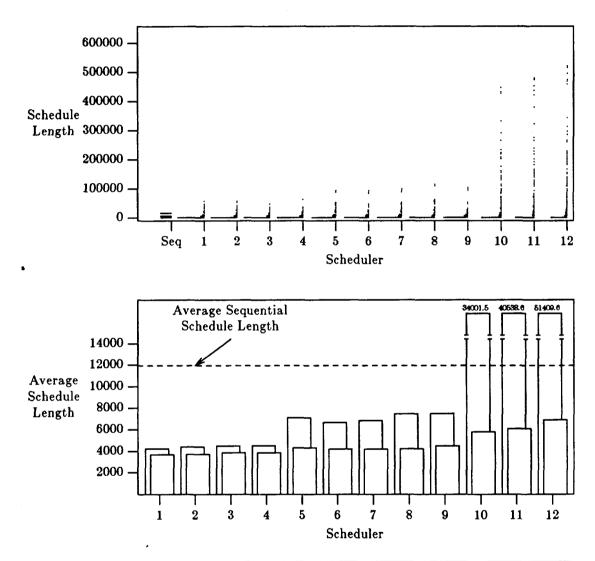

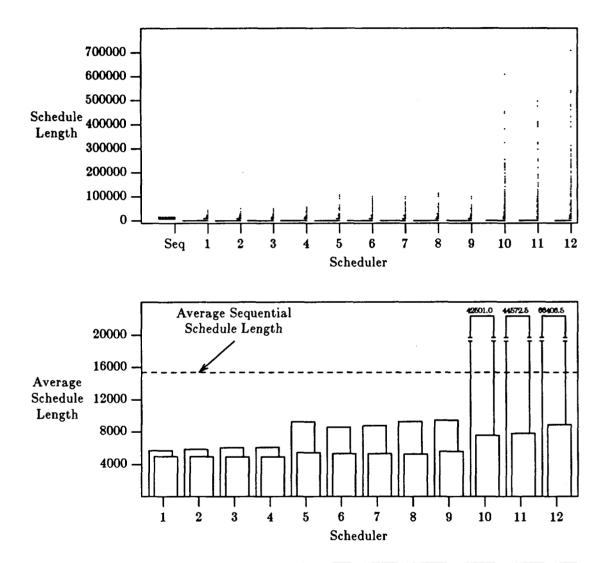

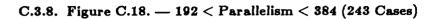

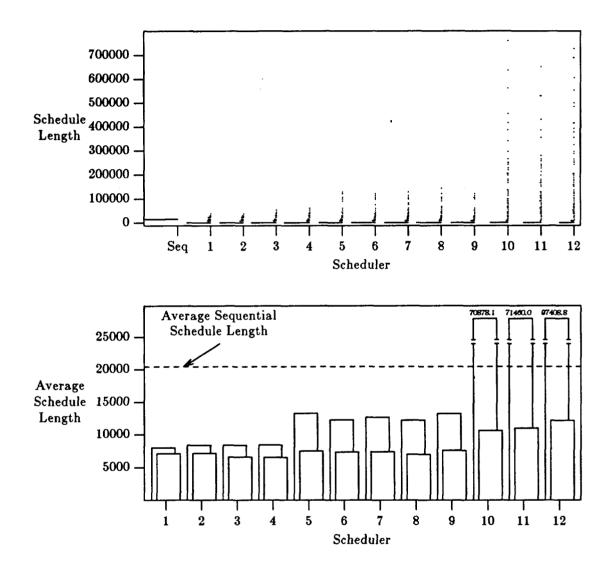

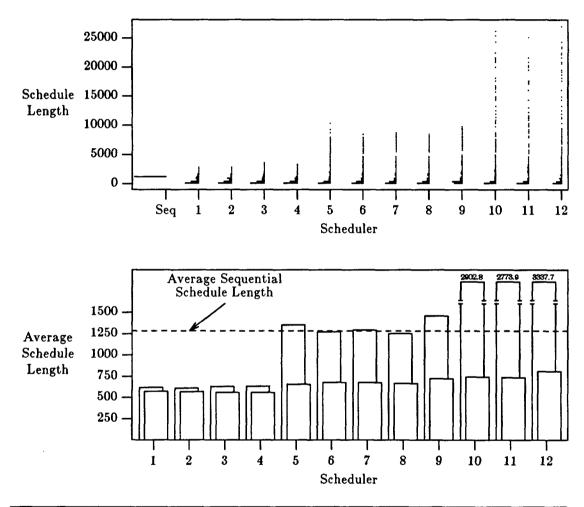

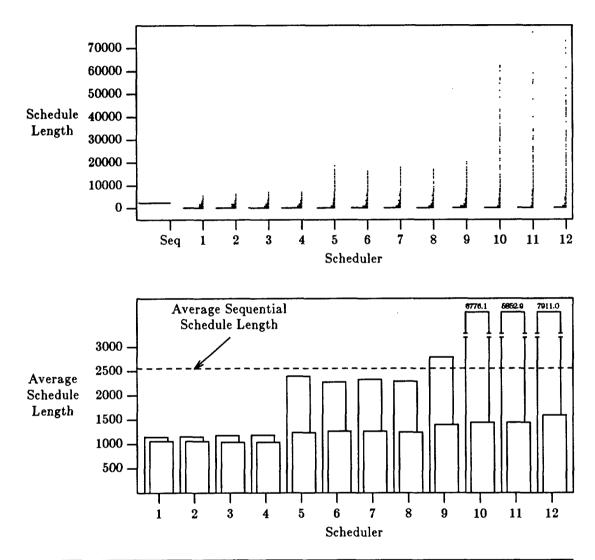

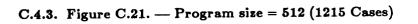

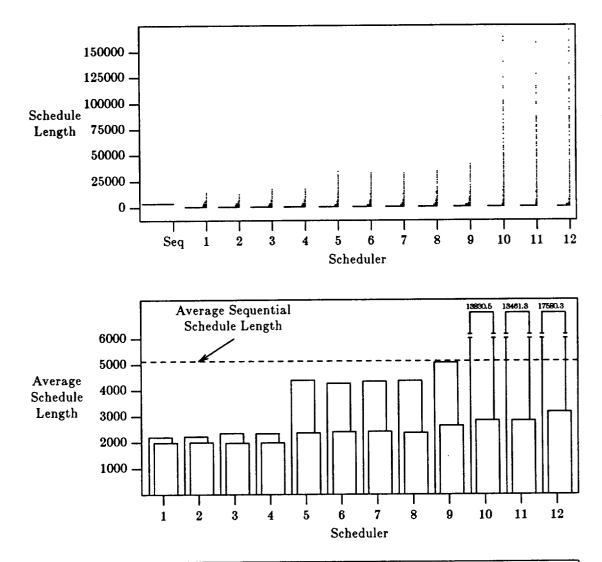

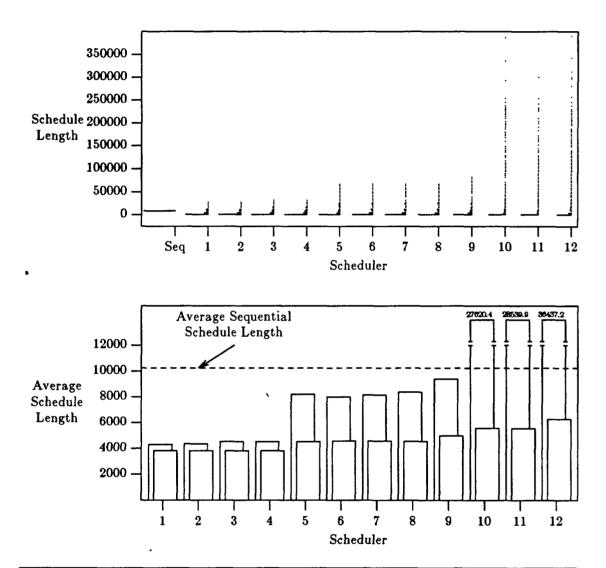

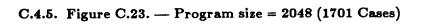

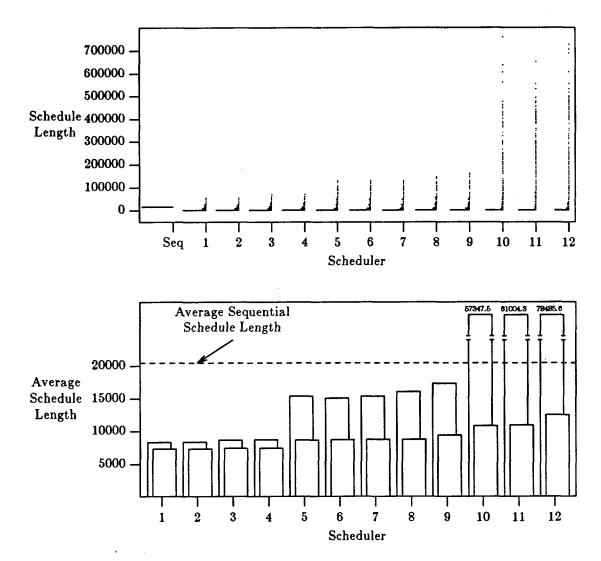

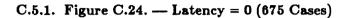

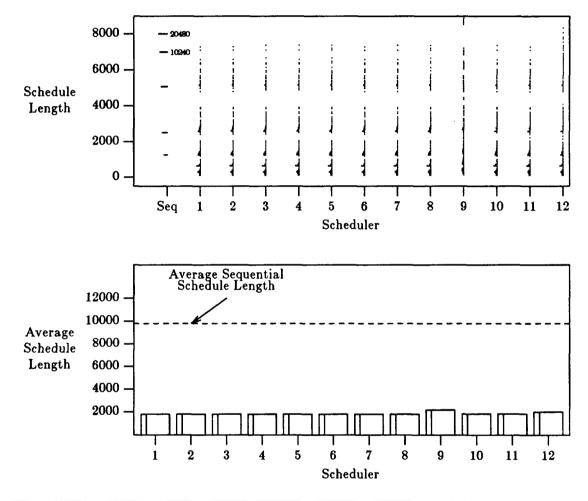

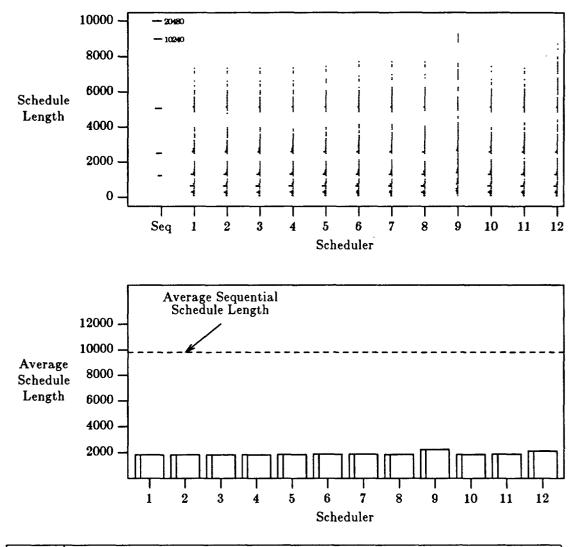

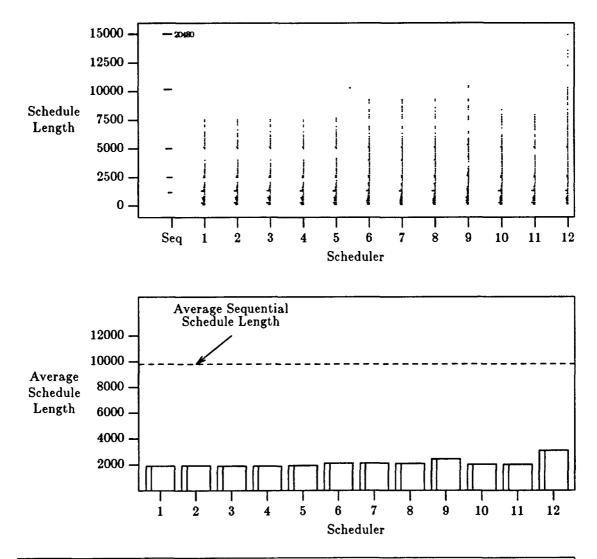

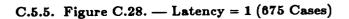

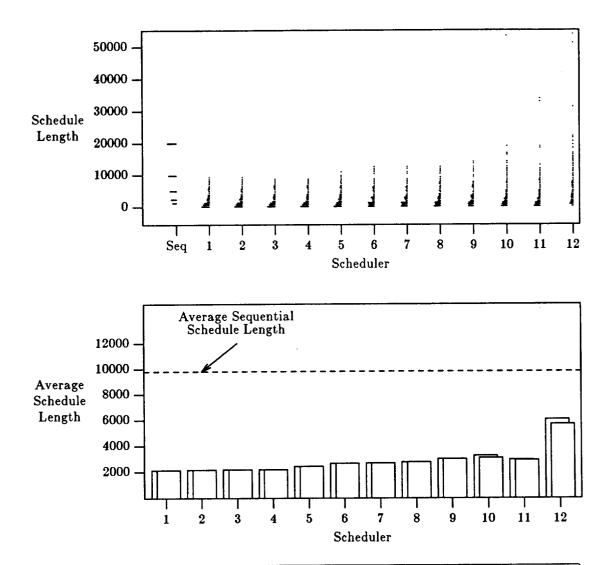

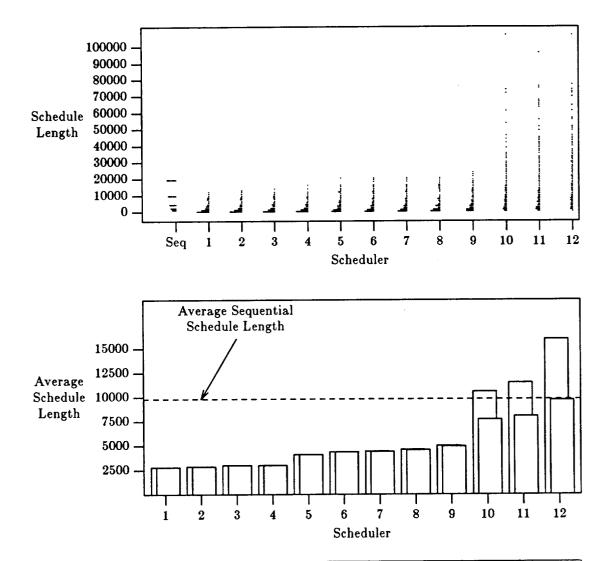

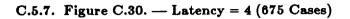

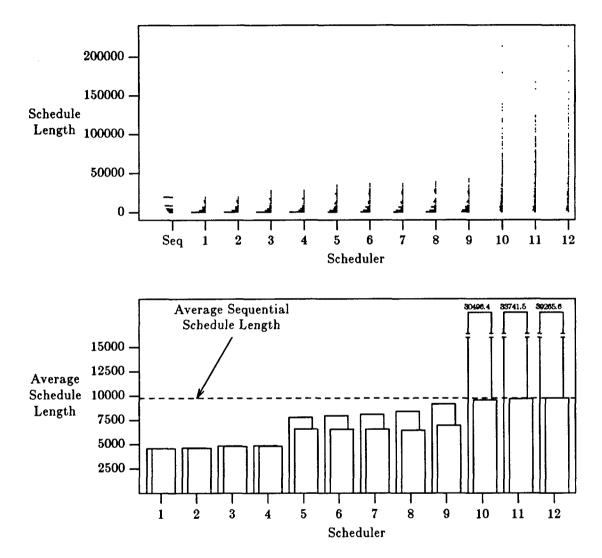

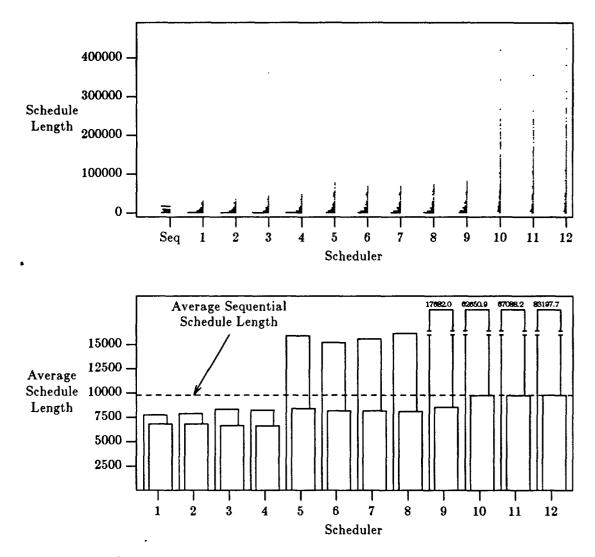

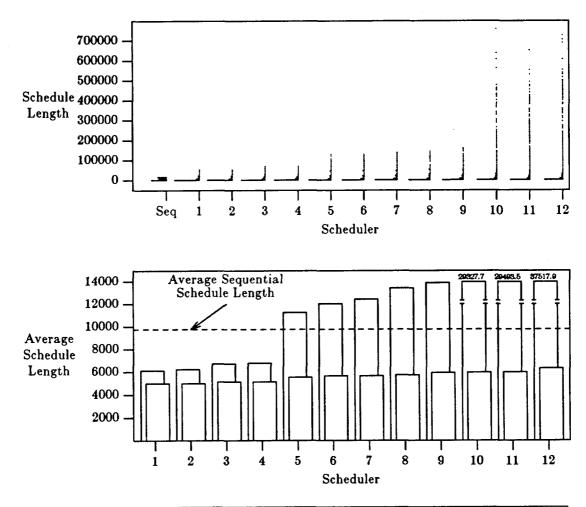

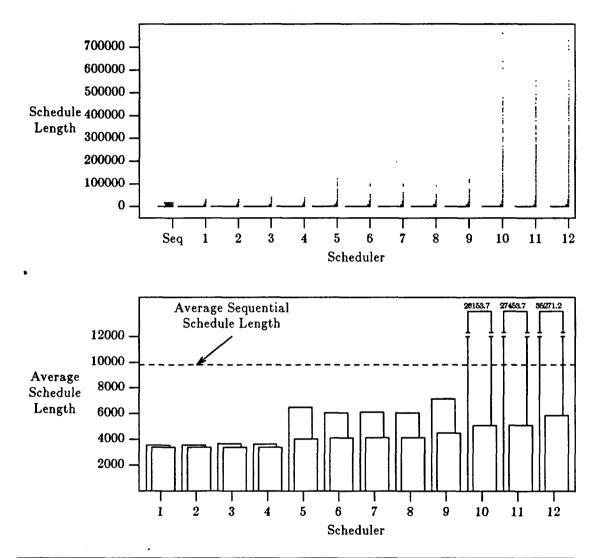

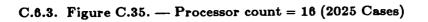

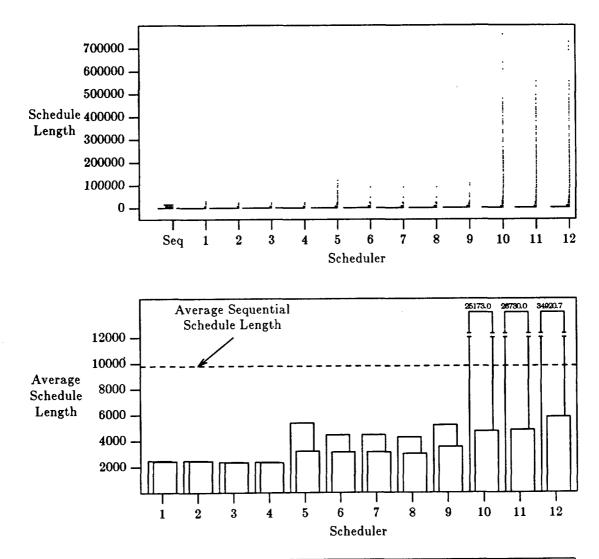

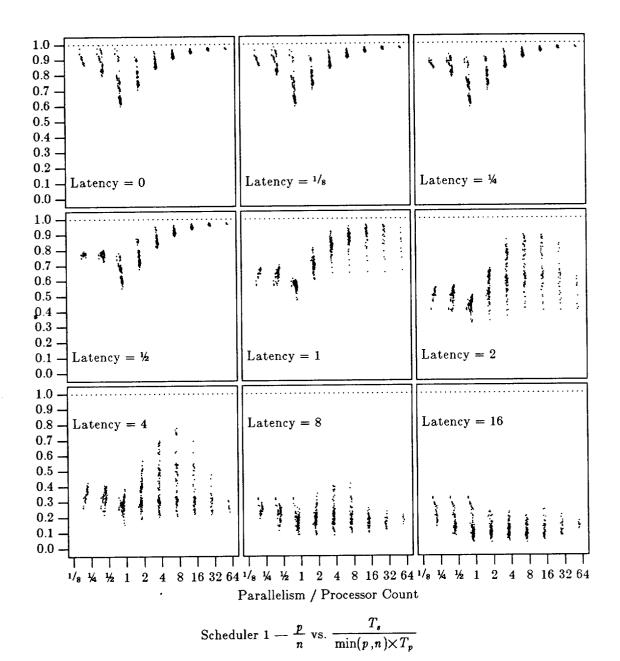

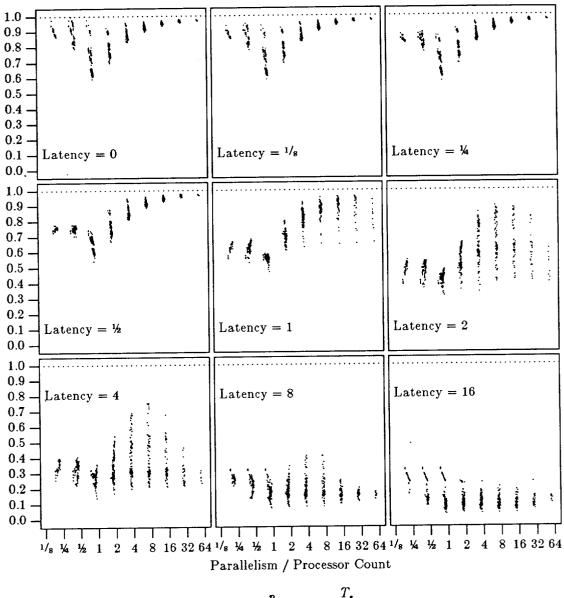

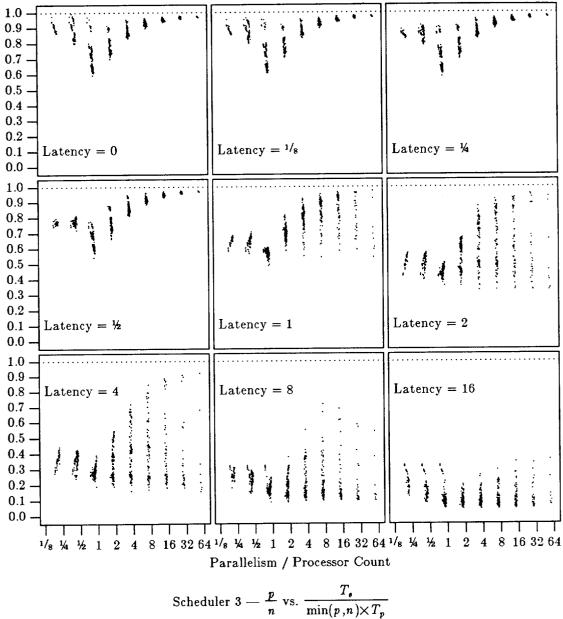

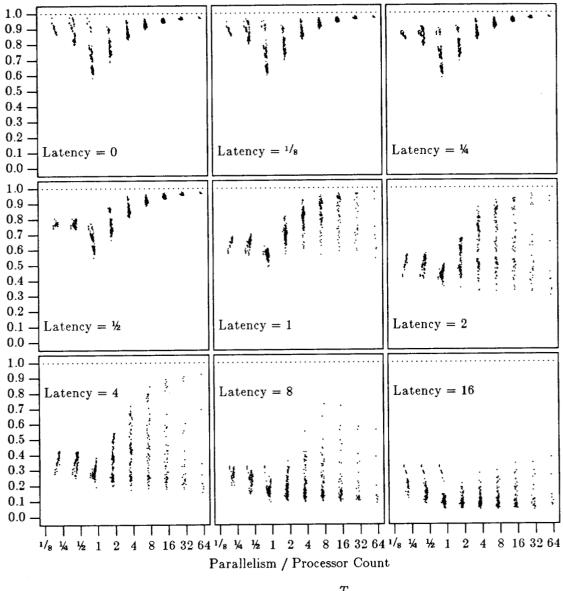

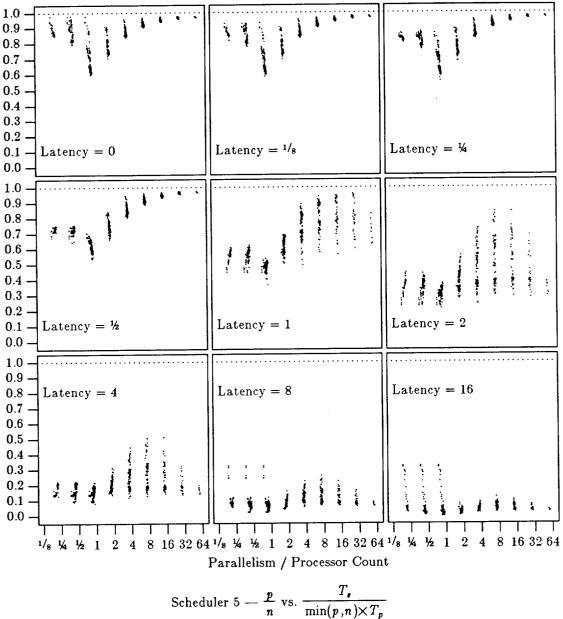

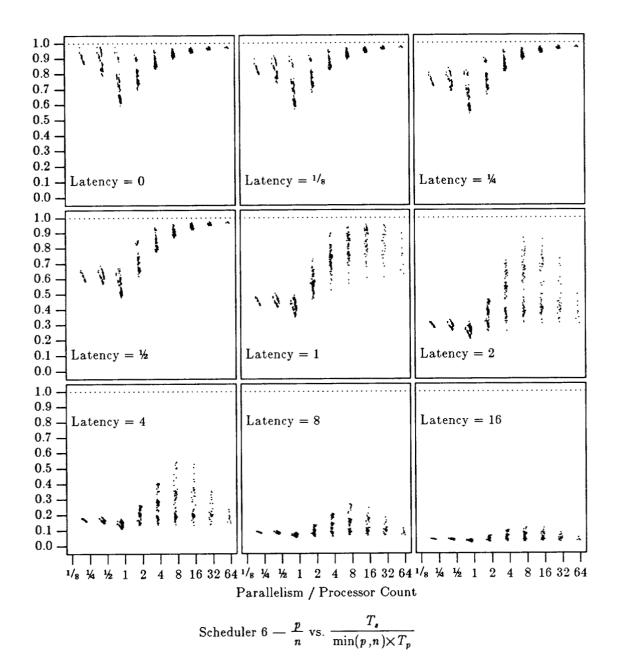

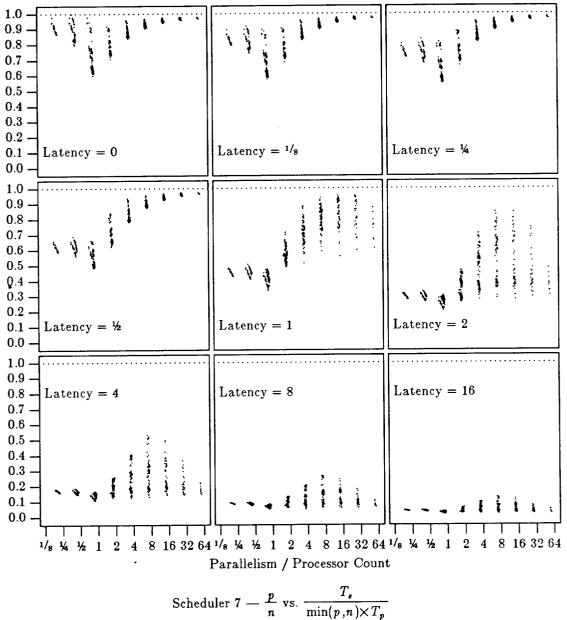

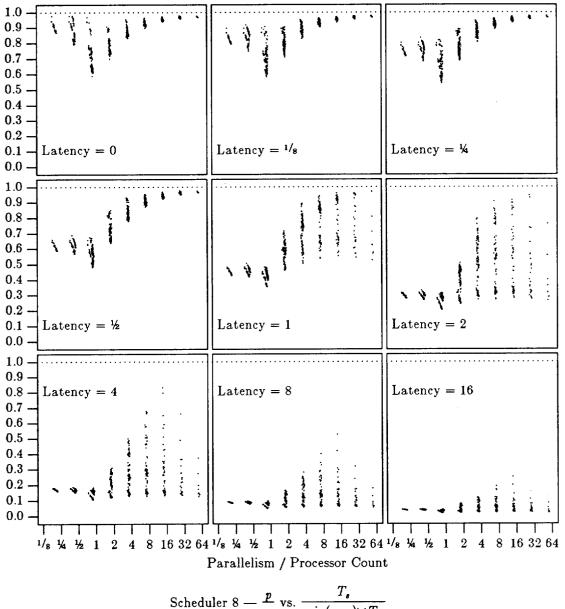

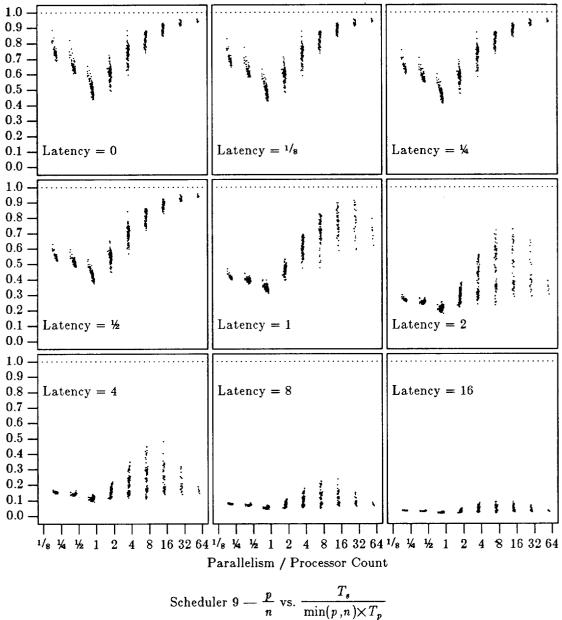

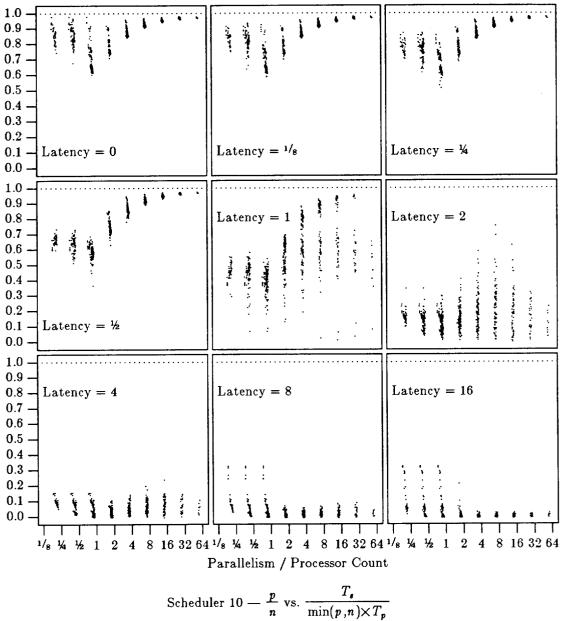

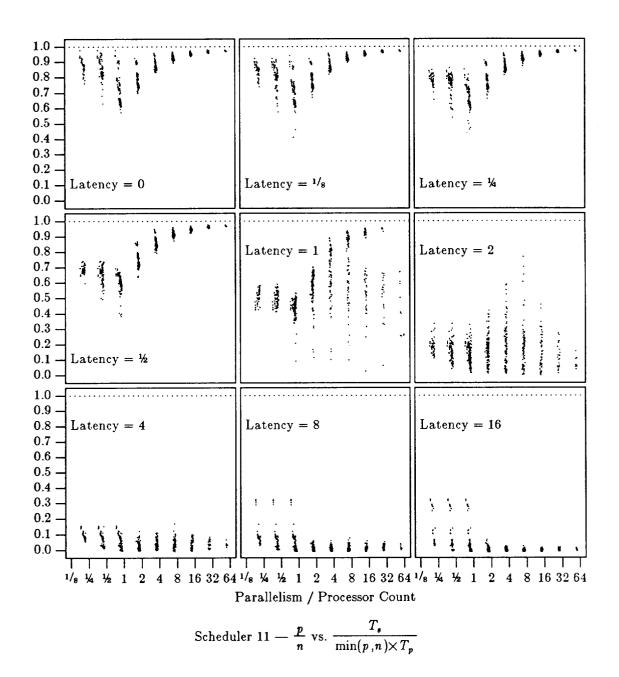

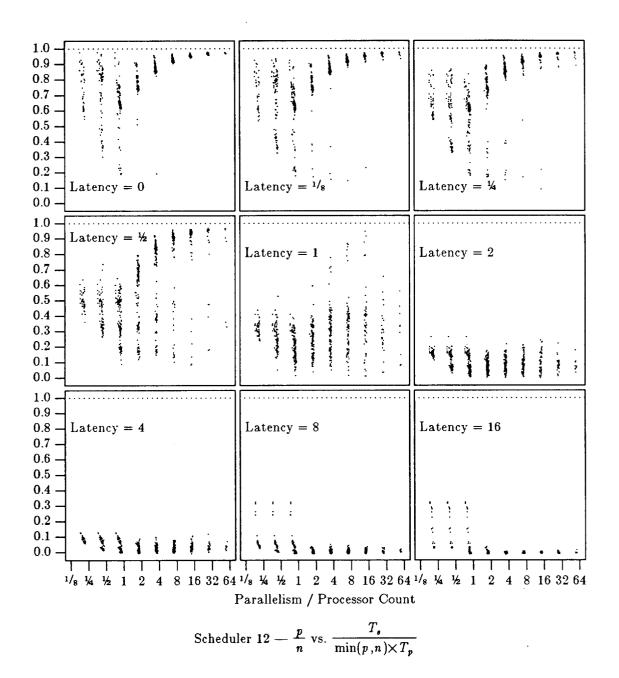

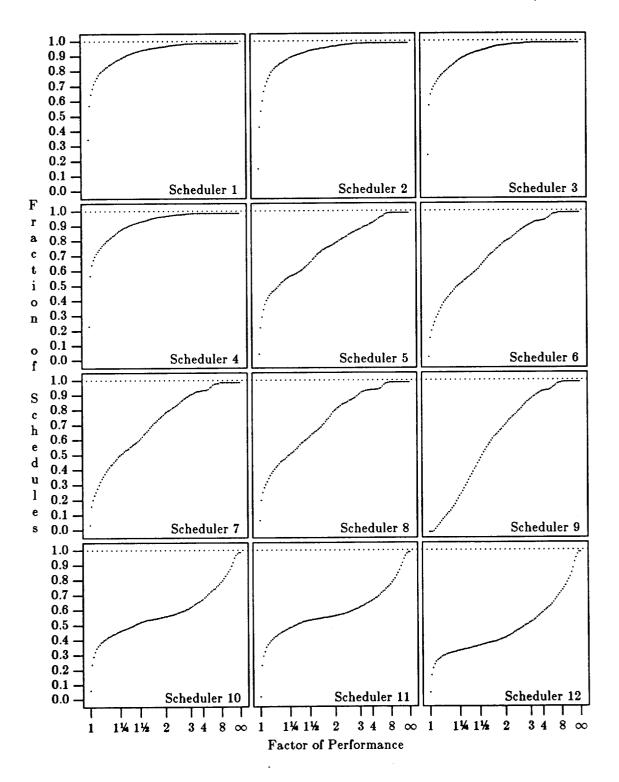

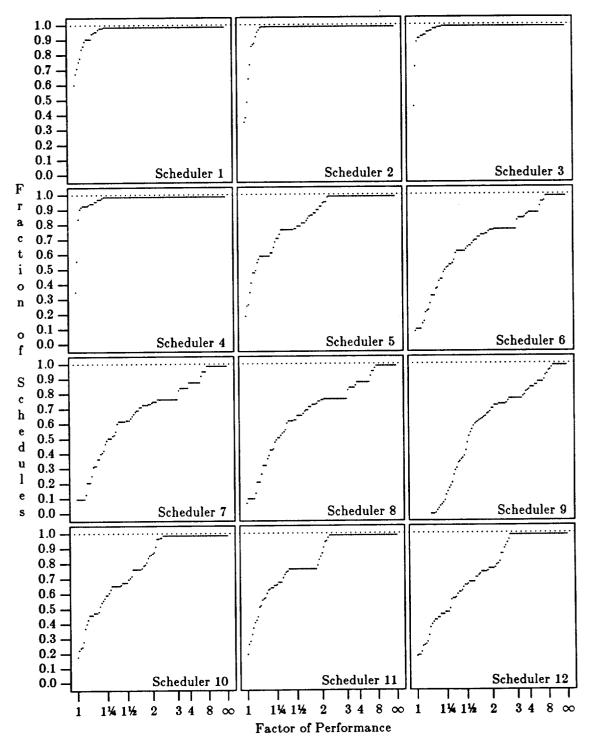

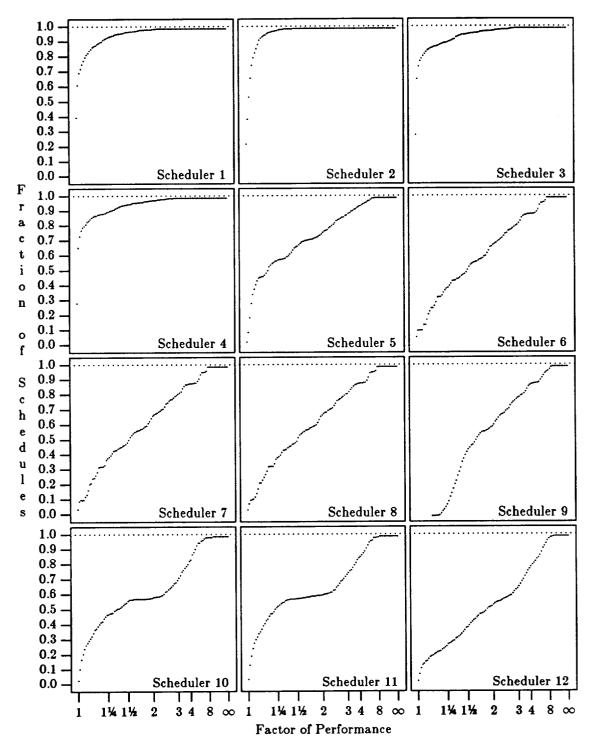

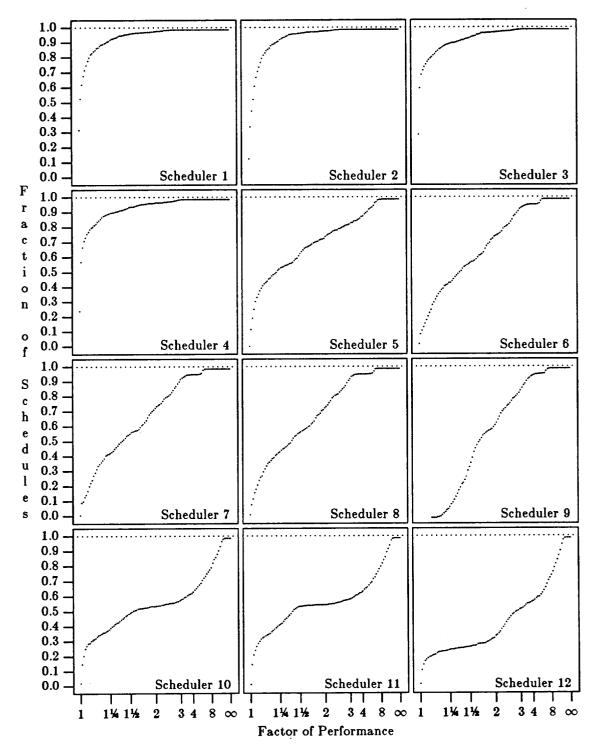

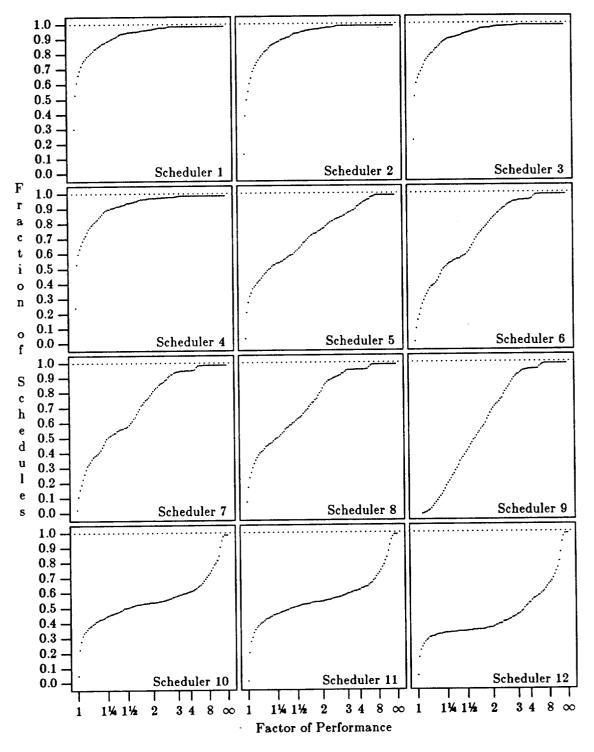

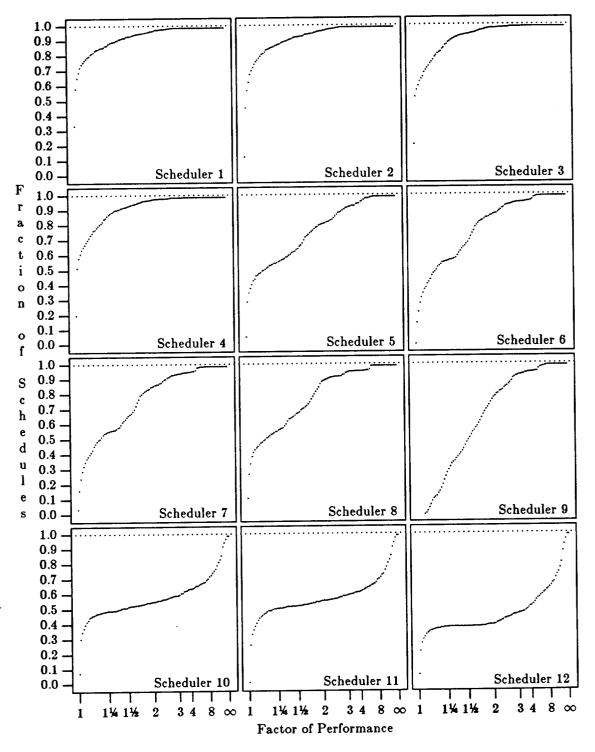

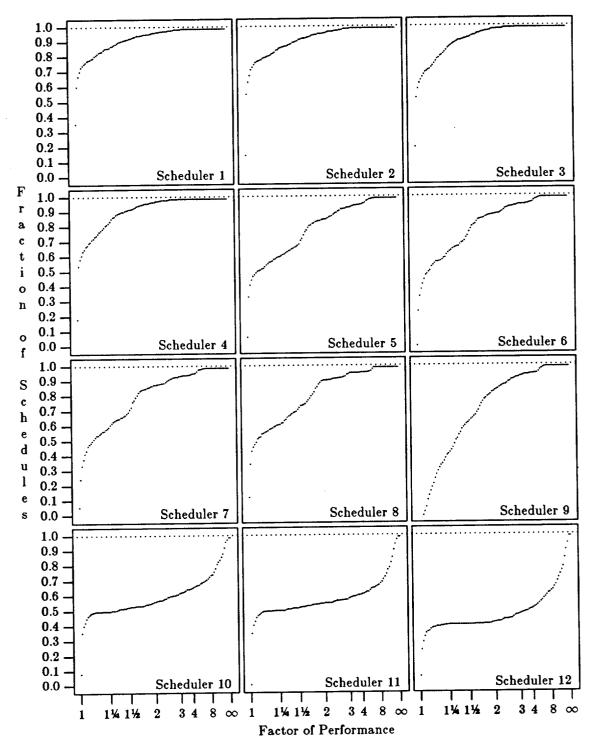

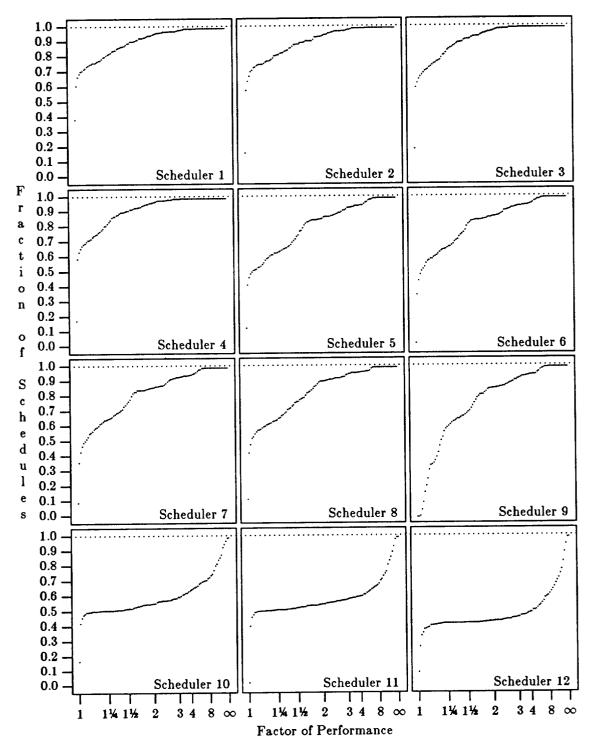

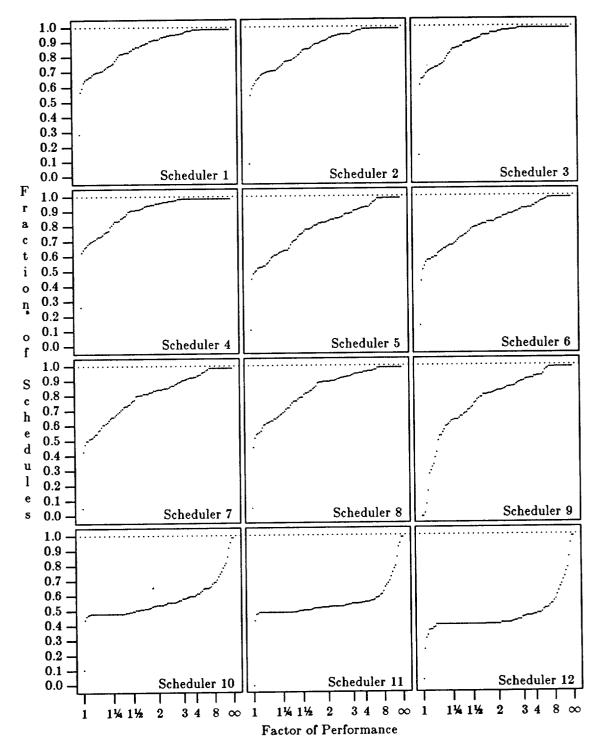

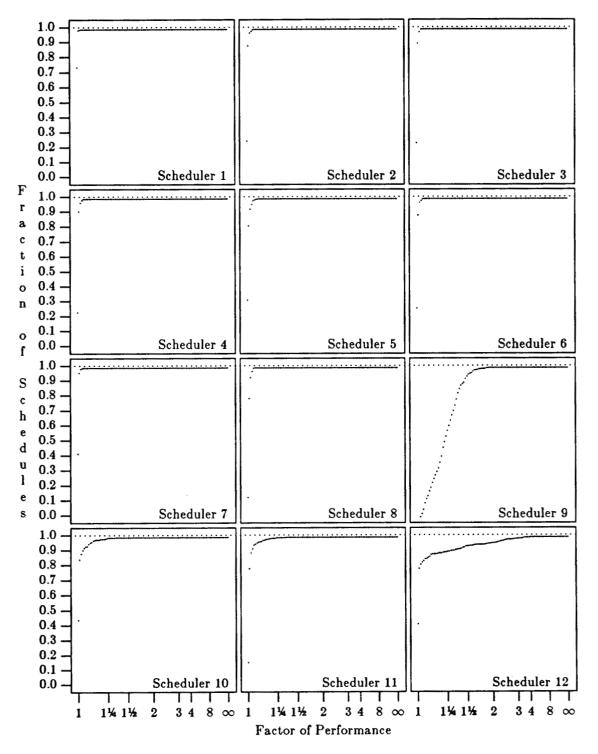

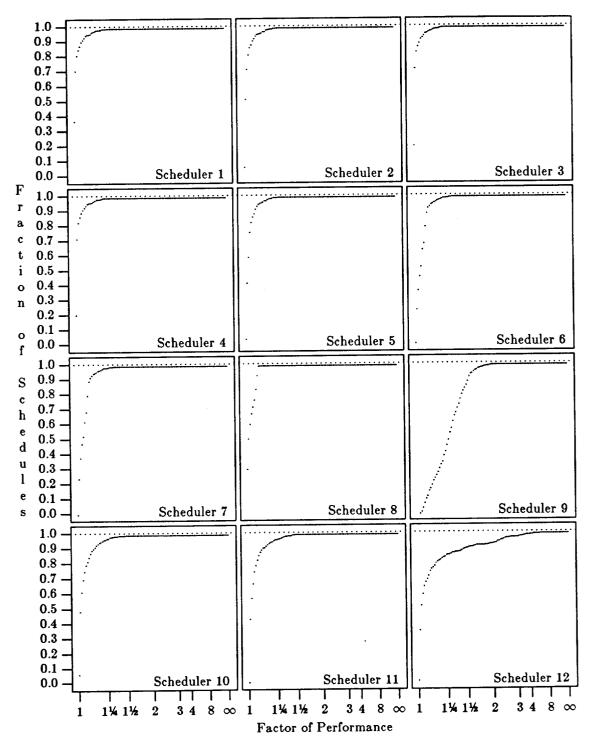

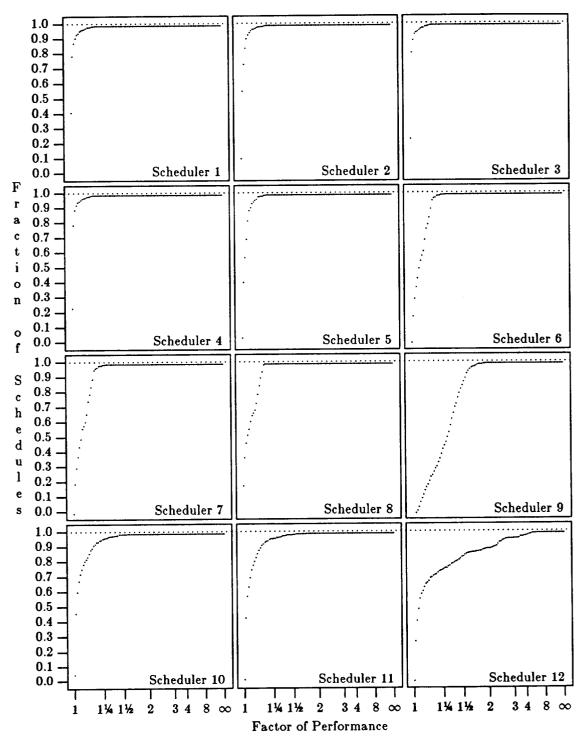

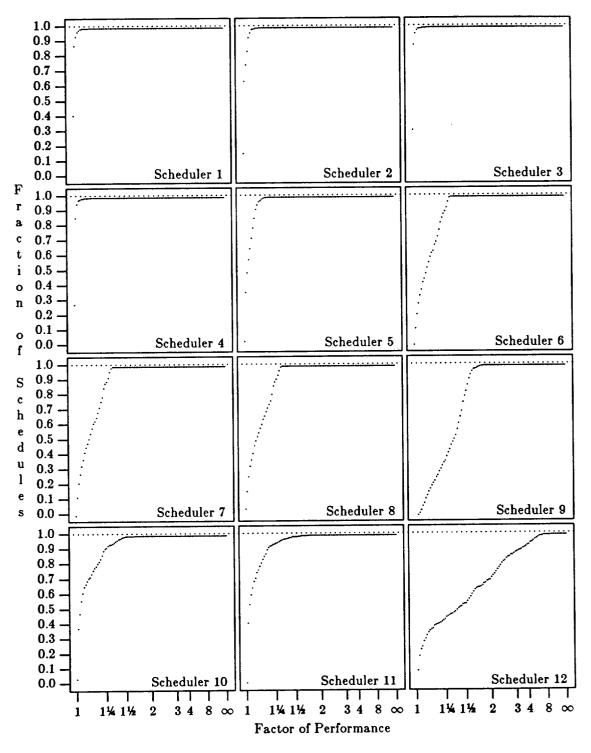

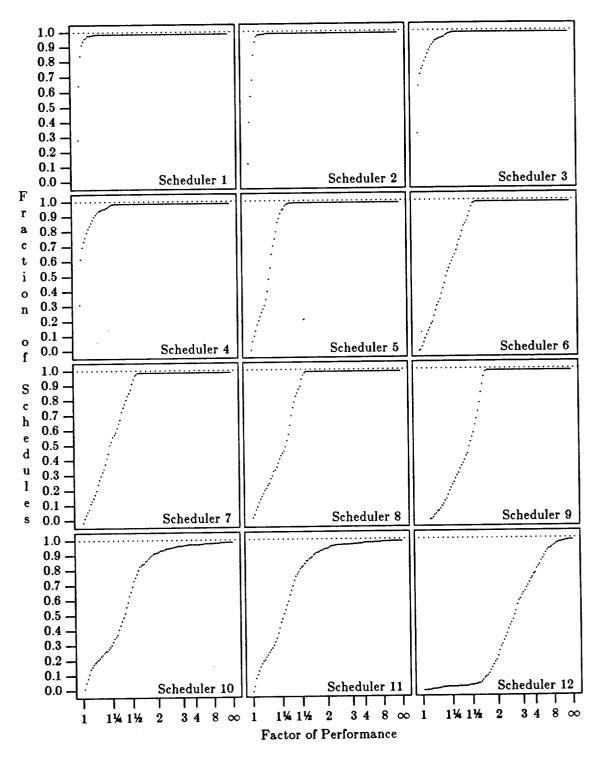

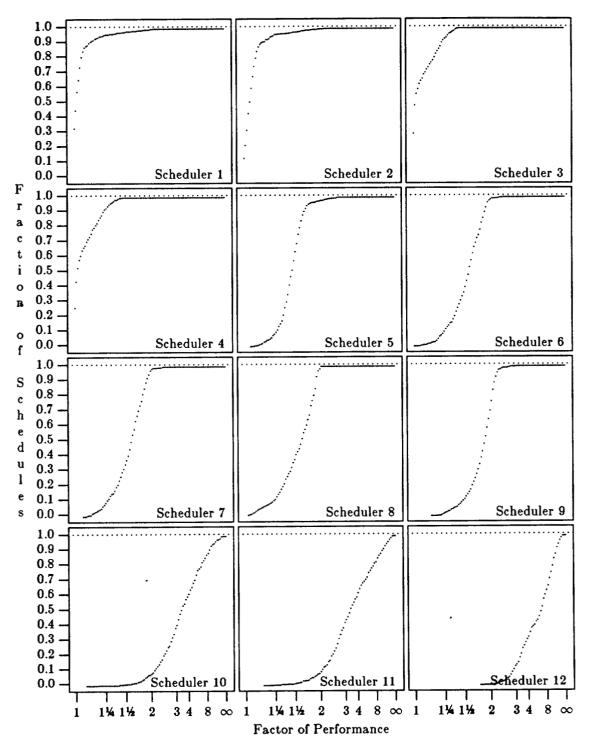

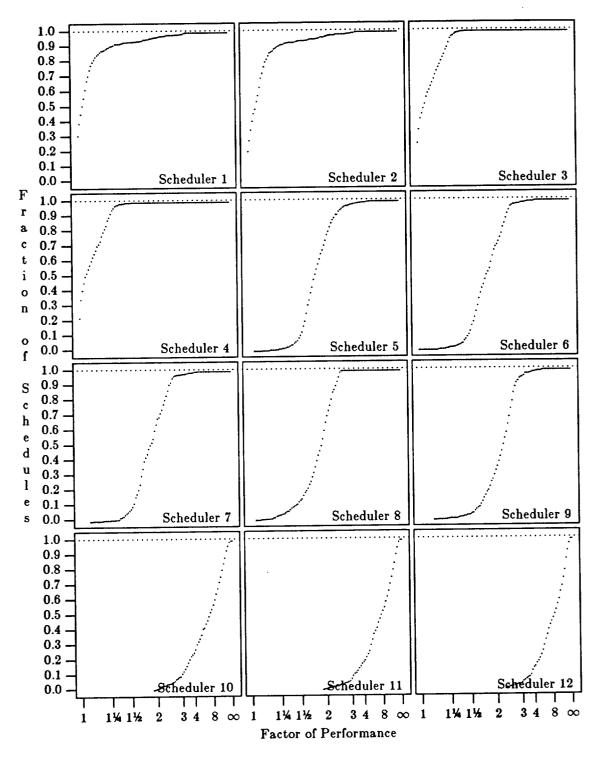

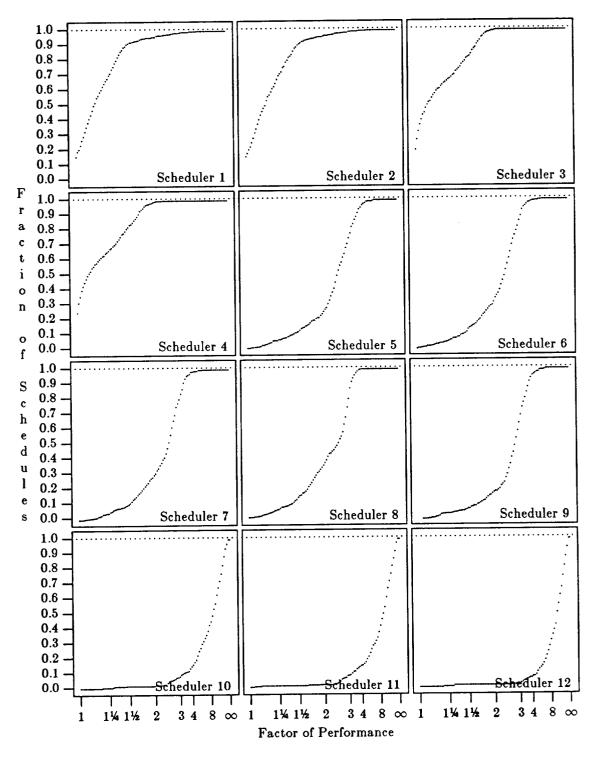

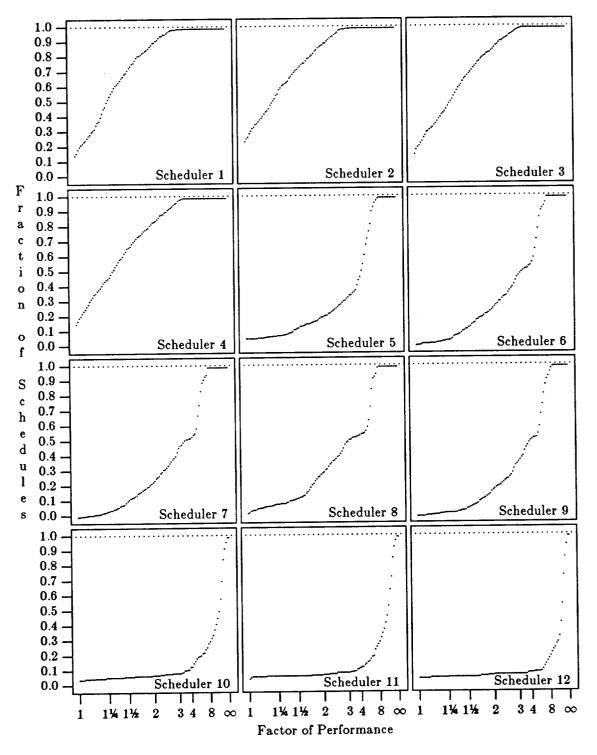

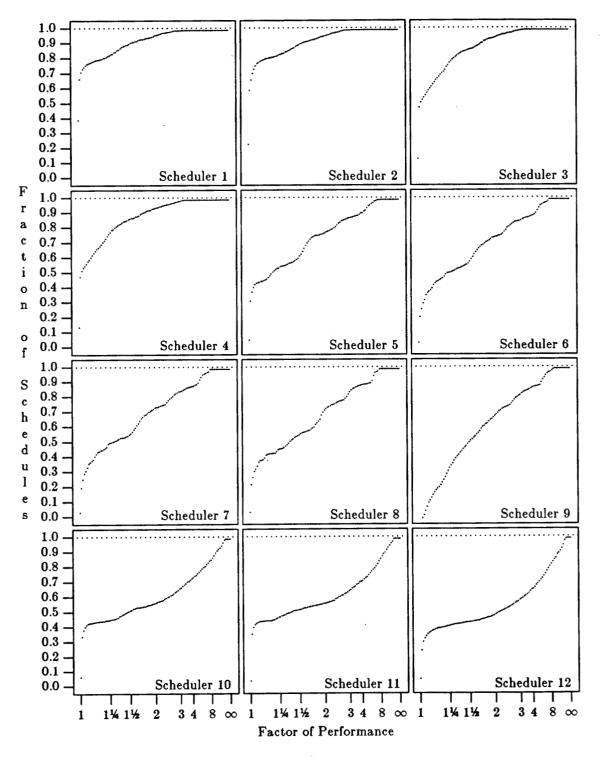

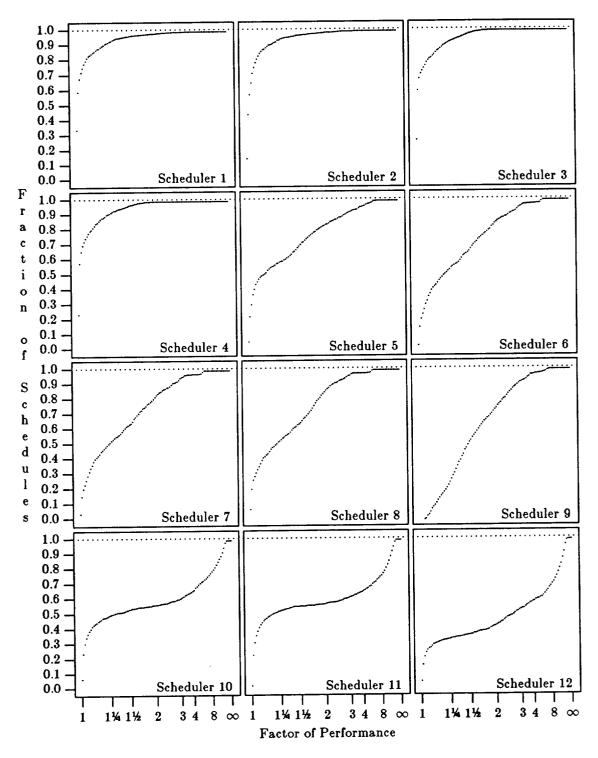

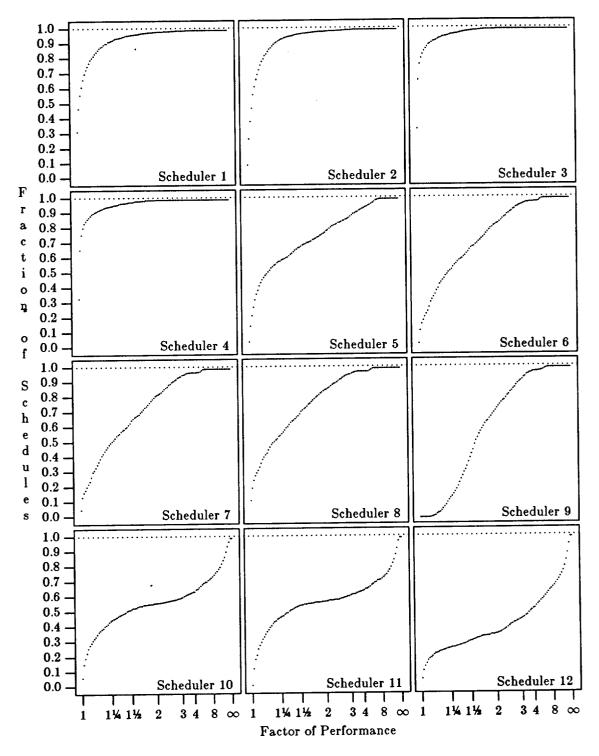

Appendix A contains graphs of the different task distributions. The remaining appendixes contain the numerical results of the different experiments. In particular, Appendix B presents the experimental results in terms of frequency histograms of schedule length, bar charts of average schedule length, and tables of all seven performance measures. Results are grouped by problem characteristic to show the effect that task distribution, average parallelism, program size, etc., have on the different schedulers. Appendix C gives the same presentation grouped by scheduler to show the effect of different scheduling decisions on scheduler quality. Appendix D contains plots of relative parallelism vs. relative efficiency. Cumulative histograms of relative scheduler performance are given in Appendix E.

## CHAPTER 2

### **Related Work**

This chapter summarizes previous work in precedence constrained scheduling (PCS). Because of the scheduler strategies considered in this dissertation, we concentrate primarily on list and list related scheduling strategies. Ullman [Ull75] proved that if task execution times are not equal, or there are more than two processors, precedence constrained scheduling for arbitrary graphs is NP-complete. This, in turn, implies that our extended problem is NP-hard, because it is a superset of PCS.

#### 2.1. PCS Without Communication Costs

A number of good heuristic solutions to PCS have been proposed in the literature. Although we are considering a more general problem, PCS with non-zero communication costs, these heuristics provide an excellent starting point for developing heuristic solutions to the extended form of PCS.

Much of the material discussing solutions to PCS is collected together into two works. The first is a survey article by M. J. Gonzalez [Gon77], the second is a book edited by E. G. Coffman [Cof76]. Gonzalez [Gon77] surveys some of the major results in scheduling theory known at that time. He classifies scheduling problems by number of processors, task duration, precedence graph structure, task interruptibility, job persistence or periodicity, presence or absence of deadlines, whether resources are limited, and whether processors are homogeneous or heterogeneous. A number of performance measures are also given, including minimum completion time, minimum mean flow time, and maximum processor utilization. Minimum completion time is an appropriate measure for scheduling large single jobs on multiprocessor systems. Minimum mean flow time is appropriate for scheduling multiple independent jobs in a time sharing environment, where fast turn around time is desirable. Appropriate heuristics and measures are also given for hard and soft real-time environments. Several scheduling algorithms are described, including those in [ACD74], and performance bounds are given.

Coffman et al [Cof76] collect into a single work much of what is known about scheduling theory. This work is more varied and in some ways more detailed than [Gon77]. It includes polynomial algorithms for exact solutions to specific subclasses of the general scheduling problem. Solutions include tree-structured task systems, processors with different speeds, and preemptive and nonpreemptive approaches. The problem complexity (its NPcompleteness) is shown, and bounds are derived on the performance of several scheduling problems. Lastly, several exact and near exact algorithms are given which use branch-andbound and dynamic programming (see [HiL74]) techniques.

The earliest reference to PCS and a critical path solution is by Hu. Hu presents the original critical path scheduling algorithm and proves it is optimal if all tasks have equal execution times and the graph is a tree or forest [Hu61]. Coffman and Graham [CoG72] later present a level-by-level scheduling algorithm (CG) which has tighter bounds than does critical path scheduling. Furthermore, scheduling of arbitrary acyclic graphs is optimal using CG if all tasks have equal execution times and there are only two processors. These two scheduling algorithms provide the basic platform from which most of the scheduling heuristics are derived.

In CG as well as Hu's algorithm, the emphasis is on ordering the selection of tasks from which the schedule is generated. A pre-scheduling analysis is done on the program graph, and the tasks are ordered into a list. As a task is removed from the list for scheduling, each processor schedule is examined and the processor with the earliest finishing schedule is selected. The task is placed at the end of that processor's schedule. A machine schedule contains only the order in which the tasks are executed, the processor on which each task is executed, and the finish time of each.

Many authors explore the advantages and limitations of this approach, among them:

Kaufman, in [Kau74], discusses a heuristic solution to the precedence constrained multiprocessor scheduling problem where the ordering relation forms a tree. Communication is considered insignificant and tasks are nonpreemptive, but tasks may have non-unit weights. Tight bounds are derived which relate his algorithm to an optimal preemptive schedule and to an optimal nonpreemptive schedule.

Adam et al [ACD74] compare the performance of five list scheduling algorithms. The schedulers are HLFET (Highest Levels First with Estimated Times), HLFNET (HLFET with equal task weights), RANDOM (task priorities are selected randomly), SCFET (Smallest Co-levels First with Estimated Times), and SCFNET. A dynamic programming preemptive scheduler is also used as a basis for comparison. There were 22 tests pulled from actual programs, mostly written in FORTRAN, and about 900 were generated stochastically. A statistical analysis of variance (AOV) concluded that HLFET performed best. A P=0.01 confidence level was used for the AOV. Tables from the text report that the largest variation between schedulers was about 31 percent. The tests considered 2, 3, and 5 processors.

Garey and Johnson present a solution to the two processor scheduling problem where there is arbitrary start times and deadlines for each of the tasks [GaJ77]. An  $O(n^3)$ algorithm gives a schedule whenever one exists. This same algorithm can also be coupled with a binary search to find the shortest such schedule, or to minimize "tardiness". A number of variations of this scheduling problem are shown to be NP-complete.

Bashir et al report the results of a statistical study in [BSV83]. In this study all tasks have unit weights, and graphs have between 20 and 48 tasks per graph. 700 graphs are generated at random, and the resulting sample is used to determine the probability that the critical path scheduling algorithm finds an optimal schedule.

Blazewicz et al [BWD84] discuss the variation on the scheduling problem where some tasks require two processors simultaneously. They present a general model for this type of scheduling, and an appropriate heuristic. Bounds on the performance of their heuristic are also developed.

Kasahara and Narita describe a fast branch-and-bound approximation scheme in [KaN84]. The initial selection for the branch-and-bound algorithm is determined by a modified critical path algorithm called CP/MISF (for Critical Path, Most Immediate Successors First). CP/MISF uses the standard critical path algorithm with the exception that ties are broken in favor of the task with the greatest number of successor tasks (i.e., tasks between it and the exit node). The approximation/optimization algorithm enumerates all possible solutions, pruning as early as possible any that are clearly inferior. The current best solution is replaced whenever a superior solution is found. Because the number of possible solutions is so large, a CPU time limit was imposed, which causes the solution to be only approximate. Tests were done for graphs with 5-200 tasks, and 2-10 processors, with no communication costs. Experimentation showed that in most cases this approach found an optimal solution within a few seconds. Kohler [Koh75] describes a slightly less refined version of the branch-and-bound algorithm used by Kasahara and Narita. His results strongly agree with those reported in the later article. Ramamoorthy et al [RCG72] develop dynamic programming algorithms that determine (1) the minimum number of processors to process a graph in the smallest possible time, (2) the minimum time required to process a graph on k processors, and (3) whether a graph can be processed in the minimum time on k processors. Two heuristics are also presented, both of which are similar to load balancing. The heuristics are compared against an optimal algorithm for small graphs and two processors. The major thrust of this paper is intended to be the dynamic programming algorithms, but the two heuristics provide ideas on task selection strategies which we use in this dissertation. Ramamoorthy's task selection strategy is different from critical path scheduling in that tasks are scheduled in the order that they become available, which can be used both in a static or dynamic scheduling environment.

Sethi [Set76] discusses some results from [CoG72] which includes an optimal  $O(n^2)$ algorithm for scheduling arbitrary directed acyclic graphs with unit weights on two identical processors. He presents a graph labeling function with O(n+e) steps. He also presents a new optimal algorithm for the two processor problem which has complexity  $O(n\alpha(n)+e)$ , where  $\alpha(n)$  is an almost constant function of n.

Graham [Gra69] and Fernandez and Bussell [FeB73] investigate the worst-case performance of a critical path scheduling algorithm. Graham derives bounds for several variations of the job-shop scheduling problem (i.e., PCS), including an upper bound on the schedule length given a fixed number of processors. Although Graham's work considers only a subset of the problem we consider, it does provide some justification for claiming that the distribution of parallelism does not have a major impact on scheduler performance, which we investigate empirically for the larger problem. More detailed information about the limits of the Coffman-Graham and critical path scheduling algorithms are given in [LaS77], [Kun81], and [Llo82]:

Lam and Sethi [LaS77] discuss the worst case performance of preemptive and nonpreemptive versions of the Coffman-Graham (CG) scheduling algorithms. They show that both algorithms are bounded by  $\omega/\omega_o \leq 2-2/m$ , where  $\omega$  is the length of the CG schedule,  $\omega_o$  is the length of an optimal schedule, and m is the number of processors. Note that this accounts for the optimality of the special case where m = 2.

Kunde derives worst-case asymptotic bounds for the critical path scheduling heuristic in [Kun81]. The bounds are derived for the special cases where tasks have unequal weights. Three types of dependency structures are considered, namely trees (2-2/(m+1)), anti-trees (exact bounds are not given, but they are generally worse than for trees), and chains (5/3).

Lloyd [Llo82] investigates the worst-case performance of the critical path scheduling algorithm and the Coffman-Graham scheduling algorithm. This analysis presumes that there are a fixed number of available processors, and that additional resources exist. An upper bound is given which depends on the number of processors and non-processor resources in the system. This upper bound is the same for both scheduling algorithms, and is asymptotically the best possible worst-case upper bound.

#### 2.1.1. PCS With Communication Costs

Several recent studies do consider communication costs in their analysis. However, none of the studies are as extensive as we have undertaken here. Three such studies are summarized here.

Kruatrachue considers the problem of communication for a precedence based scheduler in [KrL87, Kru87, KrL88a, KrL88b]. He defines the ISH and DSH schedulers; ISH is a modified version of Hu's scheduler [Hu61]. DSH is like ISH with an extra pass that duplicates tasks whenever it is beneficial to do so. Task duplication can have the beneficial effect of using idle CPU time to reduce communication. A basic assumption underlying all his results is that contention has an insignificant effect on the performance of a scheduler. All scheduling decisions are made assuming that the only delay in communication comes from channel latency, and that messages rarely interfere with each other.

Granski et al [GKS87] present a critical path algorithm suitable for scheduling dataflow graphs on a dataflow machine. Their algorithm schedules conditional branches by transforming the graph into a set of deterministic subgraphs, each element of which represents a possible path of execution. A critical path algorithm is then used to schedule each of the subgraphs independently. Loops are scheduled by first multiplying the weight of each node within the loop body by the expected number of iterations. The loop body is then scheduled as if it were acyclic. Simulated performance of their algorithm shows their algorithm compares favorably with a random scheduling algorithm.

Chester Carroll *et al* discuss a solution based on critical path analysis in [CHA88]. The solution first schedules critical paths (see Section 3.1 or [HiL74]), then adds non-critical tasks later. Task selection for non-critical tasks is done by decreasing distance from the terminal node of the graph, and uses distance from the initial node to break ties. Only "processor rich" systems were used in scheduling, which never blocked task execution because of processor unavailability. Their study considers both latency and contention in communication. Latency is restricted to being no longer than the duration of the average task. Other aspects of communication were also modeled — in particular, both completely connected and star networks with a packet switching protocol were used, and communication buffer size was included in the feasibility constraints. No performance results were reported.

## CHAPTER 3

## **Definitions And Terminology**

Briefly stated, the general problem to be considered is: what are the characteristics of parallel schedulers, programs, and architectures which affect resulting performance? Of course this problem is so broad that one can only consider a very small portion of it in a work such as this. For the sake of simplicity we will restrict the problem to static acyclic program graphs and an idealized multiprocessor architecture. In doing so we restrict the problem to what we believe are its principal components. As mentioned before, much work has been done when the cost of communication between processors is zero [Cof76], and some work has been done when communication latency is important but the communication link bandwidth is effectively infinite [Kru87]. We consider architectures that have a finite communication capacity across links, so communication latency and contention may both affect scheduler performance. In this chapter we give definitions and introduce the terminology used in the remainder of the dissertation.

#### 3.1. Task Graph Characteristics

DEFINITION: A task graph G = (A,T) is a connected, directed, acyclic graph with heterogeneous non-negative weights on all nodes and arcs.

The set T of graph nodes represents tasks to be performed; node weights represent the computational resources (i.e. CPU time) required by the program to complete its execution. Arcs in A represent communication between tasks; arc weights represent the volume of communication between tasks. It does *not* represent the communication time of the arc — that is a function of the processor schedule. The direction of the arc indicates which task is the sender and which is the receiver.

Intuitively, a task graph is a way of representing a program. Tasks within a graph are *strict* on all parameters, that is, they must receive all communication before they begin execution. Tasks are modeled as sending messages to other tasks only after the sending task has completed its execution. It is assumed for convenience that every graph begins with a single node and ends with a single node. Graphs which have more than one initial or terminal node may be easily modified to this form by adding special initial and terminal nodes.

Task graphs have no cycles nor conditional execution such as are found in dataflow graphs [Ack82, DaK82, Den80, Gur84]. The restriction on cycles is particularly severe for the representation of programs, as few useful programs are written without some form of iteration structure such as loops, recursion, or generators. Compiler technology in recent years, however, has progressed to the point where loop unrolling may take place as part of the optimizations a compiler is able to use [AlC72]. Loop unrolling partially or completely removes cycles from an otherwise cyclic graph. The unrolled portion of a loop may be represented as a task graph, or the whole loop may be represented as a single node.

DEFINITION: The parent relation of a task graph G = (A,T) is the set A of arcs of G, that is, a is a parent of b iff  $(a,b) \in A$ . Parent(a) denotes the set of tasks  $\{ p : (p,a) \in A \}$ , which are the parent tasks of a. Child(a) is the set of tasks  $\{ c : (a,c) \in A \}$ , which are all children of a.

Intuitively, a is a parent of b if b receives a message directly from a; also, b is a child of a.

DEFINITION: The ancestor relation of a task graph G = (A,T) is the transitive closure of the parent relation. In other words, a is an ancestor of b iff a is a parent of b, or there exists some c such that a is a parent of c and c is an ancestor of b. The descendant relation is the transitive closure of the child relation.

The ancestor relation is both irreflexive and antisymmetric. Irreflexive in this case means a can never be its own ancestor, and antisymmetric means that it cannot be true that both a is b's ancestor, and b is a's ancestor.

DEFINITION: An initial node of a task graph G is a task  $a \in T$  which has no parent in G, that is, a is an initial node iff  $\forall b \in T$   $(b,a) \notin A$ . A terminal node of a task graph G = (A,T) is a task a such that a is not an ancestor of any node. In other words, a is terminal iff  $\forall b \in T$   $(a,b) \notin A$ .

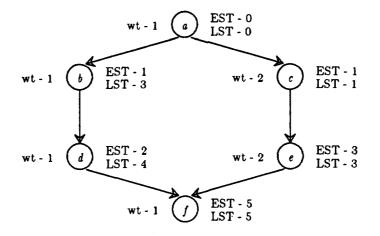

DEFINITION: The earliest starting time  $(EST)^1$  of a task *a* is  $\max_{x \in parent(a)} (EST_x + w_x)$ , where  $w_x$  is the weight of task *x*.

A task may begin execution only after all its parents have finished, so a task's EST is the estimated time of the latest parent's termination. EST ignores arc weights because the costs associated with arc weights depend on particulars of the task placement and schedule, which have not yet been determined. The EST of the initial node may be any finite value, positive, zero, or negative, but is usually chosen to be zero for convenience.

DEFINITION: The latest starting time (LST) of a task *a* is  $\left(\min_{x \in child(a)} LST_x\right) - w_a$ . The LST of the terminal node is its EST.

A task's slack is the difference between its LST and EST. Intuitively, slack measures the freedom available in scheduling the node.

<sup>&</sup>lt;sup>1</sup> These definitions for EST, LST, and slack are equivalent to the classical definitions, such as are found in [HiL74].

DEFINITION: A critical path of a graph is a connected directed path, including initial and terminal nodes, for which the slack of each task is zero.

A graph may have more than one critical path, but all critical paths will have the same length. The EST of a task represents the length of the longest path from the initial node to the task. The LST is a linear function of the length of the longest path from the terminal node to the task. Any task scheduled for execution between its EST and LST will not adversely affect the execution of the graph. A task can be scheduled before its EST when the scheduling progresses from bottom to top, in exactly the same way that a task may be scheduled after its LST when the scheduling order is from top to bottom. The two activities are symmetrical<sup>2</sup>. Any task scheduled before its EST will increase the total execution time of the graph by at least the difference between the EST and the scheduled time. Similar results occur if a task is scheduled after its LST<sup>3</sup>.

The definitions for EST, LST, slack, and critical path reflect the most optimistic execution possible which will not violate precedence constraints. They are optimistic in that they assume enough computational resources that no task is delayed due to processor unavailability, and that there is no penalty for communication. Even though these values are optimistic they serve a useful purpose as indicators for task priority.

<sup>&</sup>lt;sup>2</sup> The idea of scheduling a task before its EST may be confusing to some readers. To understand how this may occur, one must recognize that the EST is only an estimator which measures the earliest time at which a task may be scheduled without increasing the length of the schedule beyond the length of the critical path. Some scheduler designs (e.g. SCFET [ACD74]) fix the termination time of the final task first, then schedule each parent task in succession. If the final task is given a start time which is its EST, then any task which is scheduled before its EST will increase the length of the schedule. Also, when scheduling proceeds backwards like this, it may be necessary to schedule a task before its EST in order to avoid violating precedence constraints.

<sup>&</sup>lt;sup>8</sup> If more than one task is scheduled outside its EST-LST range, the execution time of the graph may or may not be augmented by the sum of the differences. This is because the schedule of one of the tasks may cause the critical path to change in such a way that the other does not affect execution. For example, suppose two parallel tasks each have LST = EST = 10. If task *a* is scheduled at time 15 and task *b* at 20, the execution will be increased by the maximum of the two, or by 10 time units. If on the other hand the tasks are sequential rather than parallel, the increase will be the sum, or 15 time units.

A number of task graph characteristics can affect the length of an optimal schedule. Among them are program size, average parallelism, task distribution, and the arity of its nodes. Program size affects schedule length by determining the total amount of work to be done. More work to be done generally means longer schedules.

DEFINITION: The average parallelism of a task graph is the ratio of the total task graph weight to the length<sup>4</sup> of its critical path.

Average parallelism measures the total amount of work that can be done in parallel over the life of the computation. It is also the ideal speedup, given an infinite number of processors with infinitely fast communication between them. Some programs are highly parallel, while others exhibit an average parallelism near unity (they are effectively sequential). An example of a nearly sequential program fragment would be the algorithm in Figure 3.1, which raises a value b to an integer power  $y = b^p$  using the binary decomposition of p. This algorithm is very fast, but it has very little parallelism.

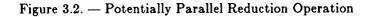

An example of a highly parallel program fragment is in Figure 3.2. Assuming + is an associative operation, this fragment may be decomposed into two equally reasonable task graphs, as shown in Figure 3.3 (a) and (b). Different task graphs are possible in this case because of the associativity. Both decompositions have the same number of operations — N additions in each case. However, because of the greater parallelism available in (b), one would expect it to have a parallel shorter schedule than (a) whenever multiple processors were available. The average parallelism of Figure 3.3 (a) is roughly 1; the average parallelism of (b) is  $N/\log_2 N$ .

<sup>&</sup>lt;sup>4</sup> The length of a critical path is the sum of the weights of the tasks on the critical path.

```

b \leftarrow base

p \leftarrow power

y \leftarrow unity

while (p > 0) {

if (p mod 2 = 1) y \leftarrow y * b

b \leftarrow b * b

p \leftarrow \lfloor p/2 \rfloor

}

```

Figure 3.1. — Program Fragment With Limited Parallelism

DO 10 I = 1, N S = S + A(I) 10 CONTINUE

Figure 3.3. — Reduction Operation Task Graphs

The distribution of tasks within a task graph (or task distribution) can potentially affect the execution in several ways. The first and most obvious way is that it determines the graph's average parallelism. The second is that it determines the amount of slack each task will have. Slack is a measure of how tightly constrained a task is in its schedule. A large slack means the task may be scheduled within a large range of times without directly impacting the overall length of the schedule.

Lastly, the shape of the distribution is capable of affecting the schedules as well. For example, if 90% of the potential parallelism occurs in the last 10% of the graph (as measured along the critical path), the execution will be essentially sequential up to the end of the program, after which the program will load up the processors until its done. If 90% of the parallelism occurs in the first 10% of the program, it might be possible to spread the parallelism across some or all of the execution of the critical path, and thus incur less additional expense. Whether this is realizable depends in no small part on the available slack.

The fan-in, or arity, of nodes in a task graph may affect parallel schedule length because each incoming arc to a task places a constraint on the execution of that task. Tasks must receive communication from all parents before they may begin execution. If the parent resides on the same processor as the child, the communication is free. If the parent does not, a certain penalty in delay and resource usage must be paid. As the arity increases, the likelihood that a parent will be scheduled on another processor, and thus that communication will be across links increases, forcing a tradeoff between communication delay and loss of parallelism. The communication delay can be reduced at the expense of reducing the exploited parallelism. This becomes very important when it forces delays in the execution of tasks along a critical path in the graph, since delays along the critical path cannot be hidden or masked — except by longer delays in parallel parts of the graph.

#### 3.2. Architecture Characteristics

Although graph characteristics are important, they are not the only significant factors in scheduling. Various architectural considerations may also influence the length of parallel schedules. This study considers three of the most important: processor count, link latency, and link bandwidth.

There is a large number of multiprocessor architectures, each with characteristics that are unique, and each with characteristics that are common to other systems<sup>5</sup>. A majority of the systems can be classified as distributed memory, shared memory, or shared address space. For the purposes of this dissertation, it is assumed only that each processor may communicate with other processors via message passing over a network of communication links. This is quite natural to a distributed memory machine. A shared memory machine might also be used as a message passing machine, by using locks or semaphores to signal the arrival of messages. A shared memory system can be viewed as a distributed machine with a completely connected network that has near-zero communication latency.

DEFINITION: A multiprocessor architecture is a graph M = (P,L), where P is the set of processor elements, and L is the set of communication links.

Communication links are some combination of uni- and bidirectional arcs, with labels on all arcs and nodes. The directionality of the arcs represents the possible flow of communication across the system. An arc label represents the bandwidth of the communication link which connects processors on both ends of the arc. (There is nothing inherent to our model which precludes communication startup costs from being used, but we

<sup>&</sup>lt;sup>5</sup> A large number of texts have appeared on this topic in recent years, and three are mentioned here. For a thorough treatment of multiprocessor systems at the architectural level, see [HwB84]. Babb [Bab87] discusses programming different commercially available parallel processing systems, and Chambers *et al* [CDJ84] considers design ideas behind some of the more exotic experimental systems.

do not consider them in this study.) Node labels represent the different capabilities a processor may have, along with the speed with which it is able to perform the work.

DEFINITION: Link latency is the time delay per unit message incurred in transmitting a message over a single empty communication link. Message latency is the time delay of a given message.

Link latency is also called communication latency, or just latency. The units of latency are generally seconds per bit or seconds per byte, but here we are interested in the time relative to the execution of an average task so it is the average tasks executed per transmission of an average message. Message latency is a function of the link latency and the size of the message to be sent.

Message delay comes from two main sources: delay due to physical properties of the communication circuits (i.e. link latency), and queuing delay due to multiple messages competing for communication links. Queuing delay, or *contention*, depends on the total resources available, the resources used by each message, and the pattern of usage. Network resources are determined by the network size and topology. Message transmission patterns can be co-operative or interfering. If message patterns are (effectively) random, interference depends on the average distance a message is sent and the number of messages in transit. Contention is dependent in part on latency because longer latency means messages take longer to cross a link, and thus the link usage is higher. This in turn causes other messages waiting to use the link to be further delayed.

Not all communications cause an increase in schedule length. Since communication between two tasks on the same processor is "free", delay can sometimes be avoided. Communication between processors that occurs along the critical path will always affect the schedule length (unless something in parallel affects it more). However, if there is sufficient slack between communicating tasks off the critical path, communication may have no effect at all. But to say that the effect of communication is indirect is *not* to say that it is insignificant. Its significance depends in large measure on the scheduler's ability to take advantage of opportunities to reduce its effects. This dissertation will examine in later chapters the effect message delay has on different scheduler strategies.

#### 3.3. Scheduling Performance Metrics

DEFINITION: A task assignment  $\alpha: T \rightarrow P$  is a mapping of tasks to a set P of processors.

If task duplication is allowed [Kru87],  $\alpha$  is a relation, not a function, because a task may be assigned to more than one processor. The same is true if certain types of preemptive scheduling is used. If task duplication is not allowed and scheduling is nonpreemptive,  $\alpha$  also induces a partition, and each task is assigned to exactly one processor.

DEFINITION: A schedule  $\sigma: T \rightarrow Z$  is a function from a set T of tasks to Z, the set of integers<sup>6</sup>. A multiprocessor schedule is a task assignment of T to a set P of processors with a schedule for each processor. All tasks must be executed at least once, and no more than one task may execute at a time on a processor.

Intuitively, T is divided among the available processors, with some tasks possibly occurring on more than one processor. Then  $\sigma$  is a function which returns the start time of a task on a processor. Because the schedules are nonpreemptive, the finish time of a task is the sum of its start time and its weight. A schedule is valid if it obeys all of the constraints, such as precedence, which are imposed upon the task graph. Although we only

<sup>&</sup>lt;sup>6</sup> In some formulations of the problem,  $\sigma$  is a function to  $Z^+$  or  $Z^0$ , and negative integers are not included. We include negative integers in our definition in order to allow a scheduler to fix the termination time of the schedule and work backwards to the starting time. The usual order is to fix the start time at zero or one and schedule forward to the end.

consider precedence in our model, other constraints, such as memory usage limits, are certainly possible.

For reasons mentioned earlier, it is desirable to schedule tasks between their EST and LST. In critical path scheduling, tasks are assigned priorities to establish the order in which tasks will be scheduled. The highest priority goes to the task which will be scheduled furthest outside of the EST-LST range, in order to minimize its impact on the schedule. Scheduling lower priority tasks first can never increase the opportunities to schedule higher priority tasks — it can only fill time slots that higher priority tasks might have used.

On the other hand, always scheduling the highest priority task first will not guarantee an optimal schedule, or even a good one. Suppose there are two unscheduled tasks a and b, and task a has the highest priority of the two. Task a might have several slots which would be equally suitable, whereas because of communication constraints task b might have only one slot which does not adversely affect the schedule length. If task a is given the slot which also happens to be the best slot for b (because it is also the best slot for a by a small margin) the schedule suffers because the completion time for b suffers. If a were less aggressively scheduled, b could take its best slot, and a would be scheduled in a slot that is "almost" as good. This strategy would ultimately give the best overall schedule, but to implement it reliably requires a search of nearly all the possible task combinations.

DEFINITION: The *length* of a task graph's schedule is the difference between the start time of the earliest task, and the finish time of the latest task.

Task weights affect schedule length in an easily understood manner — tasks that are added to the beginning or end of a schedule increase the schedule length by the value of the task weight. Arc weights (i.e. message weights) do not have as direct an influence on the schedule length. If the sending and receiving tasks are both on the same processor, no message is scheduled, and the schedule length is unaffected. If the tasks are on separate processors, the message must be scheduled on each communication link in the path which is used to transmit the message from the sending task's processor to the receiving task's processor. The amount of time reserved on each link (i.e the message latency) is proportional to the message weight and the link transmission rate. Thus the execution of the receiving task can be delayed by the latency of the message, and possibly more if other messages are competing for the links. Communication delays the execution of individual tasks, which in turn increases the schedule length.

Schedule length measures the total execution time of a given schedule. It is interesting to note that as a scheduler constructs a schedule, it attempts to model "reality" with some degree of accuracy. There may be some differences, perhaps insignificant, perhaps highly significant, between "reality" and a scheduler's perception of reality. Because of those differences, a scheduler's perception of a schedule and the actual schedule may be quite different. This is also true of the scheduler's perception of the schedule length and the actual schedule length.

DEFINITION: The parallel efficiency of a task graph schedule is the value  $\frac{T_s}{n \times T_p}$ , where  $T_s$  is the length of a sequential execution of the graph (or the sum of the weights of the individual tasks), n is the number of processors, and  $T_p$  is the length of the parallel schedule.

The parallel efficiency describes how effectively the machine is being utilized. Efficiencies near one show that near maximum speedup is being attained, while efficiencies near zero indicate that few of the available resources are being used efficiently. If tasks are not duplicated to increase parallel execution speed, low efficiencies also reflect a high processor idle time. If tasks are duplicated, all processors may be kept busy even when parallel efficiency is low.

8

The processor count and average parallelism of the task graph together place an upper bound on the speedup any parallel schedule can display on that system. The bounds are calculated in the following way:

$Speedup \leq \min(Average Parallelism, Processor Count).$

Processor count and parallelism also place a limit on the best possible parallel efficiency attainable for a graph. The best parallel efficiency is bounded above by

$Parallel \ Efficiency \leq \min(\frac{Average \ Parallelism}{Processor \ Count}, 1).$

## CHAPTER 4

#### Scheduler Components

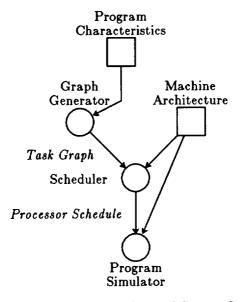

Stubborn scheduling designs generally consist of three main phases: task selection, processor selection, and schedule generation. Both the length of schedule computed and the running time necessary to create the schedule will depend on the algorithms chosen for these phases. It is interesting that the *interaction between components* can also have a major effect on scheduler performance. For example, we discovered that combining a schedule generator that models communication latency and contention, with a processor selector that uses only latency can be very detrimental. Schedulers which include this pair can generate schedules that are more than 40 times as long as a corresponding sequential schedule. Dividing schedulers into phases gives us a simple taxonomy which will be used to compare schedulers in later chapters.

#### 4.1. Task Selection

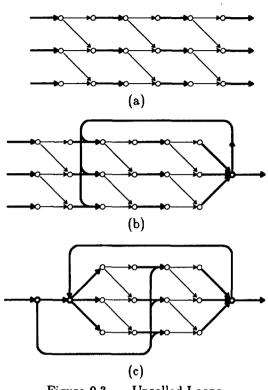

The task selection phases can be subdivided into task priority assignment and task selection. Priority assignment is an analysis of the (perhaps partially scheduled) task graph to determine the order in which (remaining) tasks will be scheduled. Tasks are then selected for scheduling according to the priorities assigned. Task priority may be a function of the task's distance from the top of the task graph, from the bottom of the graph, or both [Gon77]. Distance is measured as the sum of the running times of each task along the longest path from the graph start (finish) to the task. No additional distance is usually included because of communication. While unscheduled tasks remain Assign task priorities Select a task to be scheduled Select a processor for the task Schedule the task on the processor End

Figure 4.1. -- Scheduler With Multiple Task Priority Calculation

The priority assignment may occur as infrequently as once or it may occur more often. A single priority assignment has the advantage of requiring less CPU time to generate a schedule, whereas multiple priority assignments allow the task priorities to adjust to the changing conditions that will occur during execution. For example, the assignment of a particular task to a particular processor could change the critical path of the task graph; reassigning task priorities would allow priorities to reflect such changes. Figure 4.1 shows the scheduling algorithm that recomputes the task priorities each time a task is selected. If the task priorities are computed only once, the priority computation can be moved out of the scheduling loop, as in Figure 4.2. This algorithm is used in all other schedulers.

> Assign task priorities While unscheduled tasks remain Select a task to be scheduled Select a processor for the task Schedule the task on the processor End

Figure 4.2. — Scheduler With Single Task Priority Calculation

#### 4.2. Processor Selection

Once a task has been selected for scheduling, a determination must be made as to which processor the task must be assigned to yield the most favorable result. Each processor must be examined to determine which processor assignment will yield the overall shortest schedule. This requires that the "important" aspects of the architecture be modeled. Some features worth considering are communication link latency and capacity, and processor load. Incorrect modeling of an architecture can lead to grossly inefficient schedules, while complete modeling can be prohibitively expensive.

This work considers several processor selection functions, namely random processor selection, selection based on processor load only, selection based on processor load and communication latency, and selection based on load, latency, and communication capacity (or contention). For random selection a processor is selected at random each time a task is to be scheduled. Each processor is equally likely to be selected, and no consideration is given to the architecture or to the schedule generated. When selection is based on load, each processor schedule is examined. The processor with the shortest schedule, i.e., the earliest completion time or lightest processor load, is selected to receive the task. When selection is based on load and latency, each schedule is examined as before but the time required to communicate results to other tasks is also included. It is assumed that each communication link is completely devoid of other traffic, i.e., interference between messages is not considered. This is a reasonable approximation if the average link utilization is generally quite light.

The last processor selection strategy considers processor load, link latency, and contention. Communication contention is modeled by individually scheduling messages on communication links. A separate schedule is maintained for each link in the system. Thus if a previous message is scheduled to use a link at a given time and a second message would use the same link at the same time, the second message is delayed or, when possible, scheduled earlier than the first. In this way message contention is completely accounted for, and simultaneous transmission of multiple messages over a communication link is not allowed.

### 4.3. Schedule Generation

Schedule generation deals with the actual construction and recording of the various schedules. It is at this time that a task is actually assigned to the processor which has been selected for it. This can be done in several ways. For a given task assigned to a processor, the generator may place the new task at the top (or bottom) of the processor's schedule, or it may search the schedule for a suitable slot which would not increase the schedule length. Task insertion in parallel scheduling has been the basis of some study [KrL87,Kru87], and although it increases the time required to generate a schedule, it can shorten the schedule length by a modest amount.

Another degree of freedom in schedule generation is the level of architecture modeling undertaken. Just as processor selection may make certain assumptions about the environment in which a program will be executed, the schedule generator must also make assumptions about the environment. And although it is the same environment, each need not necessarily make the same assumptions. For example, it might be the case that only processor load is considered in selecting a processor, but the schedule generator might build schedules which explicitly account for all messages a task will send, and thus model both communication latency and contention. It is worth noting that the processor selector may only use those features modeled by the generator, though it may choose to use fewer. This is because the schedule generator is the mechanism that records the state of the execution through each step of the scheduled computation.

## 4.4. Descriptions of Schedulers

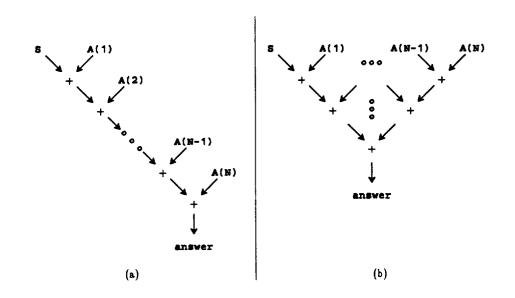

Task selection, processor selection, and schedule generation define a taxonomy. Of the 160 schedulers this taxonomy defines 12 were selected for experimentation, for reasons explained below. The specific characteristics of the schedulers used are summarized in Table 4.1, and their relationship to other schedulers may be found in Figure 4.3. A complete description of each scheduler is included in the following sections. The designations in the table indicate how the scheduler was constructed. The two fields under "Priority Assignment" indicate the behavior of that part of the scheduler. The entry "Once" indicates that the scheduler assigns the task priorities once before the first task is scheduled, and they do not change after that point. "Many" indicates that the task

Figure 4.3. — Organization of Scheduler Design Space

| Scheduler | Priority<br>Assignment |        | Task<br>Selection | Processor<br>Selection | Schedule<br>Generation |      | Complexity      |

|-----------|------------------------|--------|-------------------|------------------------|------------------------|------|-----------------|

| #1        | Once                   | Bottom | Тор               | Contention             | Insertion              | Full | $n^2 p \ell$    |

| #2        | Many                   | Тор    | Тор               | Contention             | Insertion              | Full | $nm+n^2p\ell$   |

| #3        | Once                   | Тор    | Bottom            | Contention             | Insertion              | Full | $n^2 p \ell$    |

| #4        | Many                   | Тор    | Bottom            | Contention             | Insertion              | Full | $nm+n^2p\ell$   |

| #5        | Once                   | Bottom | Тор               | Latency                | Insertion              | Lat. | $n^2p$          |

| #6        | Many                   | Тор    | Тор               | Load                   | Insertion              | Full | $nm+np+n^2\ell$ |

| #7        | Once                   | Bottom | Тор               | Load                   | Insertion              | Full | $np+n^2\ell$    |

| #8        | Once                   | Тор    | Bottom            | Load                   | Insertion              | Full | $np+n^2\ell$    |

| #9        | Once                   | Тор    | Тор               | Random                 | Insertion              | Full | m               |

| #10       | Once                   | Bottom | Тор               | Latency                | Insertion              | Full | $np+n^2\ell$    |

| #11       | Many                   | Тор    | Тор               | Latency                | Insertion              | Full | $nm+np+n^2\ell$ |

| #12       | Once                   | Bottom | Тор               | Latency                | No Insert.             | Full | $np+n\ell$      |

### Table 4.1. - Scheduler Design Parameters

8

priorities are re-calculated each time a task is scheduled. "Top" ("Bottom") indicates that the priority is measured as the distance from the top (bottom) of the task graph. "Top" ("Bottom") under "Task Selection" indicates that task selection occurs from the top (bottom) of the task graph.

Under "Processor Selection" there are four choices, namely, "Random", "Load", "Latency", and "Contention". These indicate the level of architecture modeling that occurs in the determination of each task's processor assignment. "Random" indicates that the processor is selected at random. "Load" indicates that only the processor load, or schedule length, is considered in selecting a processor. "Latency" means that both processor load and communication latency are modeled. An entry of "Contention" indicates that the task is successively scheduled on each processor, complete with task insertion and message scheduling, and the processor which gives the best task completion time is selected.

The "Schedule Generation" columns indicate whether task insertion was used in the final schedule, and at what level the scheduler modeled the architecture. "Full" indicates that both tasks and messages were scheduled on the various resources, i.e., that communication contention was modeled. "Latency" indicates that tasks were scheduled with sufficient delay that communication could take place across the appropriate processors, but otherwise communication was not considered.

Figure 4.3 includes the entry "Order", to indicate that the order of tasks is maintained on the architecture, but no additional information is retained. A scheduler need not record task start and finish times only if they are not used in either task or processor selection. Any scheduler which selects a processor based on processor load, latency, or contention must record task start and finish times in addition to the order in which tasks are executed. Scheduler #9 selects processors at random, so no start or finish times are needed. In our experiments a separate task graph execution simulator is used to determine the actual schedule length, so all schedules are, in effect, "measured by the same yardstick". This is needed because, as discussed in Section 3.2, each scheduler's perception of task start and finish times may not be consistent with "reality".

This particular selection of schedulers was chosen to compare not only the costs and benefits of different scheduler phase designs, but also the relative importance of each scheduler phase. Several of the most promising phase designs were selected for each scheduler phase. A processor selection phase which selected processors at random was also used, primarily to provide a scheduler which could be used as a standard of reference for other schedulers.

The first four schedulers, #1, #2, #3, and #4, were designed to test the impact of task selection strategies on schedule length and CPU time. Each of these four schedulers are identical in every way, except for task selection strategy. Scheduler #1 uses the same task selection strategy used in Hu's scheduler [Hu61], and in critical path scheduling [Koh75]. Scheduler #2 uses a task selection strategy which is identical to that which is used in dynamic load balancing (cf. [ELZ86,LiK87]), namely earliest available task first, or first come, first served. Dynamic load balancing selects tasks in order of availability, that is, task priority is measured as the distance from the starting point, and the tasks closest to it are selected. In other words, both priority assignment and task selection occur from the top of the task graph. Because load balancing occurs at run time, the priority assignment is effectively recomputed each time a task is assigned.

One important difference between dynamic load balancing and the corresponding static approach is that the dynamic approach suffers from incomplete knowledge of the system load when decisions are made, due to the necessity of distributing load messages relatively infrequently. For this reason the static approach is an idealized version of the dynamic approach. It provides a lower bound on the schedule length, both because of the availability of complete information at the time the schedule is created, and because the overhead of generating the schedule does not interfere with the execution of the task graph.

In addition to the above approaches, Hu's task selection method was also inverted, that is, priority was measured as the distance from the top of the graph and tasks were selected from the bottom. Scheduler #3 measures the task priorities once, scheduler #4 measures the priorities each time a task is selected for scheduling. Scheduler #4 was chosen to test the importance of multiple passes in the task selection phase.

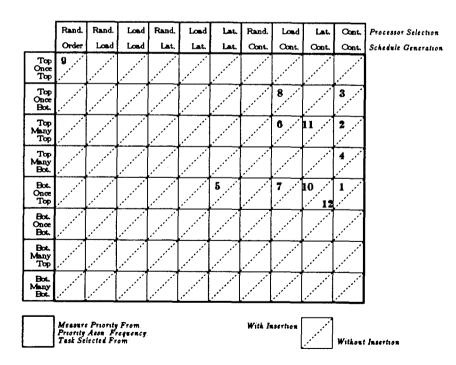

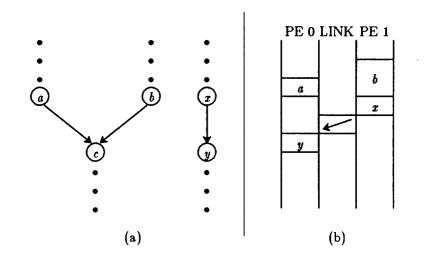

To understand more fully how the task selection mechanism works, consider the task graph in Figure 4.4. Scheduler #1 uses a task selection phase which measures task priority from the bottom of the task graph, so it uses the LST of each task to determine the task selection order. It selects tasks from the top, so a task with the *smallest* LST is selected first. Thus scheduler #1 would select tasks in the order a, c, b, e, d, f. Ties are not

Figure 4.4. — Example Task Graph

explicitly resolved, so the order of tasks b and e might be reversed.

Scheduler #2 measures task priority from the top of the task graph, so it uses the EST value. It selects tasks from the top, so it would select them in order of smallest EST to largest. The first task to be selected is task a. Once scheduled, it would fix a's EST at the actual time it was scheduled, and recompute the EST for all unscheduled tasks. In this way the task selection mechanism receives feedback from the actual schedule, at least as it is perceived by the scheduler. The order in which all remaining tasks are scheduled, therefore, depends on details of the architecture and other phases of the scheduler. After the EST's are recomputed, the next task is selected for scheduling.

Scheduler #3 measures task priority from the top, and selects tasks from the bottom, so it too uses the EST to determine task ordering, but it reverses the order used by scheduler #2. It first selects the final task and schedules it. It then selects another task and schedules it, subject to the constraint that the execution of the second task must complete *before* the final task, including any time needed for communication. Scheduling proceeds in that manner until all tasks are scheduled. The order in which tasks from Figure 4.4 would be scheduled is f, d, e, b, c, a. Scheduler #4 works in the same way as #3, but like scheduler #2 it fixes the EST of a task once it is scheduled, and recomputes all ESTs.

Schedulers #6, #7, and #8 were designed to discern the effect of less expensive processor selection strategies. A major portion of the scheduling expense comes from the processor selection phase of the scheduler, so a less expensive one — load balancing — was substituted. To select a processor, each processor schedule is examined, and the processor with the earliest completion time is selected. Since it was not known whether task selection would have an impact on the effectiveness of a processor selection strategy, three different task selection strategies were used. Scheduler #6 in particular was selected because its design is closest to that of dynamic diffusion scheduling.

Schedulers #10 and #11 were also designed as an attempt to find effective, but inexpensive, approaches to scheduling. The idea was to use load balancing, but include a cost for communication. The main constraint was that the communication cost had to be inexpensive to compute. Message latency was used, since the amount of computation required is proportional to the task arity, and the arity is usually a very small number.

To illustrate the different approaches to processor selection, consider the partial task graph in Figure 4.5 (a). (Only node precedence has been shown — node and arc weights have not been marked, for convenience.) If we are scheduling the graph for a two processor system, a partial result might be the schedule shown in Figure 4.5 (b). Assume that task c is the next task to be scheduled.

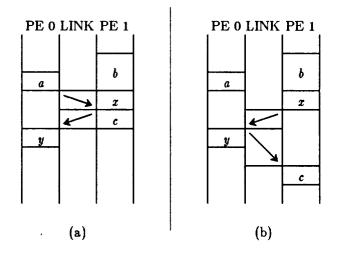

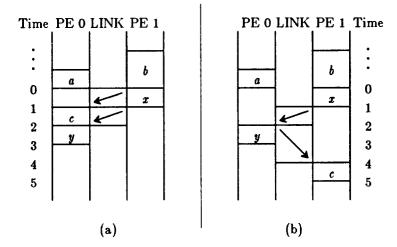

If the processor selection phase uses only load to select a processor for a task, then c will be scheduled on PE 1, because its schedule finishes first. If the communication requirements between tasks a and c are small, the result will be a tight schedule, as shown in Figure 4.6 (a). However, if the message is large, the results could be very poor, as shown

Figure 4.5. - Partially Scheduled Task Graph Fragment

Figure 4.6. — Processor Selection Using Processor Load

in Figure 4.6 (b). It might be better to schedule c on PE 0, depending on the size of the message connecting b and c. The same type of problem can occur if load and latency, but not contention, are used in processor selection, although it would not occur in this example.

Figure 4.7. — Processor Selection Using Contention

.

Now consider the situation which occurs if the message from a to c is large, and the message from b to c is small. For concreteness, assume that the messages require empty link transmission times (i.e. latencies) of 2 and 1, respectively, and that the execution time of task c is also 1. The processor selector would first try c on PE 0, the result of which is shown in Figure 4.7 (a). It would then try c on PE 1, shown in Figure 4.7 (b). The first schedule clearly is the better schedule, so PE 0 would be selected.

This example also illustrates the concept of *task insertion*. There are unused spaces in PE 0's schedule which can be used by tasks such as c. When such spaces exist, they can often be filled by scheduling suitable tasks in them, as they were in Figure 4.7 (a). Schedules can be made more efficient with task insertion, because it uses what would otherwise be processor idle time.

The remaining schedulers, #5, #9, and #12, were each selected for different reasons. Schedulers #5 and #9 were chosen to provide a basis of comparison for the other schedulers. Scheduler #5 is Kruatrachue's ISH scheduler, which has been proposed as a solution to this problem [Kru87], and scheduler #9 schedules tasks at random. Scheduler #12 was selected because poor performance was observed in scheduler #10, and it was thought that task insertion might be causing the problem. Scheduler #12 was designed to test that hypothesis. It differs from #10 in that #10 uses task insertion and #12 does not.

## 4.5. Scheduler #1

Scheduler #1 (Figure 4.8) is one of several variations on Hu's scheduler [Hu61]. Assigning task priority, as mentioned before, can be done using a standard PERT analysis routine and the tasks put on a heap (also called a priority queue, heaps are discussed in [Sed83]). PERT analysis has complexity O(m+n), where m is the number of precedence arcs in the task graph and n is the number of tasks in the task graph, so task priority assignment is  $O(m+n\log n)$ , Checking for unscheduled tasks has complexity O(1). Task selection, because of the heap structure, takes  $O(\log n)$  time.

Processor selection and task scheduling are a bit more complicated. To select the best processor for a task t, t must be scheduled on each of the p available processors, and the best selection recorded. This involves finding the shortest available communication path from each parent of t to t itself. A standard  $O(\ell)$  shortest-path graph search is used, such

> Assign task priorities as distance from the graph bottom While unscheduled tasks remain Select the task that is closest to the top Select the processor for which the task will finish at the earliest time (including communication) Schedule the task on the selected processor (recording both processor and link schedules) End

> > Figure 4.8. — Scheduler #1 Algorithm

as is found in  $[Sed83] - \ell$  is the number of links connecting the *p* processors. For this scheduler, each message must be scheduled on each link over which the message is transmitted to avoid overloading the link. Overloading the link would cause a delay in the actual message transmission which would not be anticipated by the scheduler. To further shorten communication time, the link schedule is searched for the earliest time slot which will accommodate the new message. This allows the message to be sent across the link at the earliest possible time after the processor has initiated the transmission. Therefore, assuming the number of parents is bounded above by some small constant (i.e. task arity is independent of the total number of tasks in the graph), the complexity of finding the fastest communication path is  $O(n\ell)$ .

To insert t into the destination processor schedule, the schedule is searched for the earliest slot which occurs after the message arrives. Because this search is O(n), it is overshadowed by the complexity of the communication algorithm, and can be ignored. Now because there are p processors on which to try each task, processor selection is an  $O(p\ell n)$  operation. Task scheduling involves at most the same operation repeated once (rather than p times) and does not affect the overall complexity.

Collecting terms together and noting that the loop executes n times, the time complexity for scheduler #1 is  $O(n^2 p \ell)$ .

#### 4.6. Scheduler #2

This algorithm (Figure 4.9) is very similar to that of scheduler #1, with the notable exceptions that task priority is measured from the top, and it is measured each time a task is selected for scheduling. This behavior is very much like that of a dynamic load balancing system, in that tasks are selected as soon as they become available on a first come, first served basis. It is also similar in that it locally minimizes the system load.

While unscheduled tasks remain Assign task priorities as distance from the graph top Select the task that is closest to the top Select the processor for which the task will finish at the earliest time (including communication) Schedule the task on the selected processor (recording both processor and link schedules) End

Figure 4.9. — Scheduler #2 Algorithm

Differences are that there is no runtime overhead associated with scheduling, and the scheduler has complete knowledge of the state of the entire system. Dynamic load balancing systems *do* have a runtime overhead associated with scheduling each task. Also, every processor's knowledge about the system is limited by the frequency with which it receives load messages. Because load messages are received relatively infrequently, a processor's knowledge is incorrect by the amount the system state has changed since the last load message was received.

Another, perhaps more subtle difference is that because the entire system state is known, the static scheduler can effectively minimize loading for communication links as well as the processors. It also avoids delays which can result because of the asynchronous nature of a dynamic load balancing system. For example, if two processors each have work to export and they both choose the same processor to receive the work, the receiving processor could end up with work to export — it might have been better if one of the original processors had given the work to a different processor.

The time complexity of this algorithm is very similar to that of scheduler #1. Differences are that the PERT analysis is done inside the loop, and the heap is no longer needed. This means the complexity for scheduler #2 is  $O(nm+n^2p\ell)$ . Assign task priorities as distance from the graph top While unscheduled tasks remain Select the task that is closest to the bottom Select the processor for which the task will finish at the latest time (including communication) Schedule the task on the selected processor (recording both processor and link schedules) End

Figure 4.10. — Scheduler #3 Algorithm

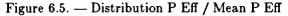

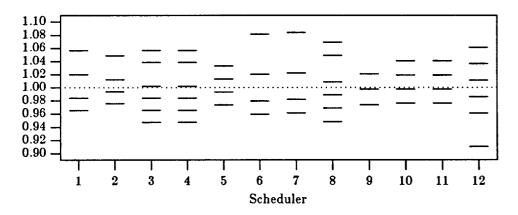

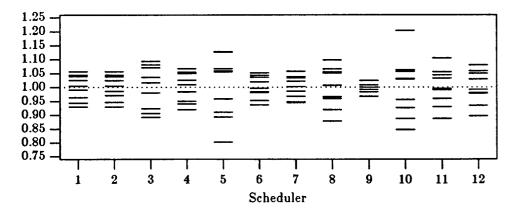

#### 4.7. Scheduler #3