## Comparison of CMOS XOR and XNOR Gate Design

Makara Tang

B.S. Mathematics, Portland State University (1997) Minor B.S. Electrical Engineering, Portland State University (1997)

> A thesis presented to the faculty of the OGI School of Science and Engineering at Oregon Health and Science University in partial fulfillment of the requirement for the degree Master of Science in

Electrical and Computer Engineering

August 2002

i

The thesis "**Comparison of CMOS XOR and XNOR Gate Design**" by Makara Tang has been examined and approved by the following Examination Committee:

> Advisor: Dr. Shih-Lien Lu Senior Staff Researcher Intel Corporation

Thesis Committee: Dr. Dan Hammerstrom OGI, Professor

Thesis Committee: Dr. Milt Scholl OGI, Associate Professor

### Acknowledgements

The author thanks his close friend Ossah Chan at Mentor Graphics as market engineer for supporting the tool, and his co-workers, Michael Pang Cheng Hsu (Senior Staff Researcher, Intel) for suggestions on the HSPICES NETLIS waveform. The author also thanks Professor Shekha y Borkar (Intel), Professor Stewart Taylor (Maxim), Professor Milt Scholl (OGI), Professor Rom Krishnamurthy (Intel), Professor Kartik Raol (Intel), Professor Raj Solanki (OGI), Professor Malgorzata Chrzanowska-Jeske (PSU), and Professor Shih-Lien Lu (Intel) for their classes that I took and led me to an understanding of the field of modern VLSI technology. Thanks also to Intel Corporation Department of Circuit Research Lab that offered me a job. I had practical experience with hands on analytical tools by operating the equipment and probing wafers at the Circuit Research Lab. Finally, the author would like to thank the persons that helped editing his thesis Professor Milt Scholl (OGI), Julianne Williams (OGI), Professor Jody Lee House (OGI Reading/Writing research group), Yi Liang (OGI Reading/Writing research group), and

# **Table of Contents**

| Pa                                                                  | ige |

|---------------------------------------------------------------------|-----|

| Acknowledgements                                                    | iii |

| List of Tables                                                      | v   |

| List of Figures                                                     | vi  |

| Abstract                                                            |     |

|                                                                     |     |

| 1.0 Synopsis                                                        | 1   |

| 1.1 Physical Layout                                                 |     |

| 1.2 Fan-Out                                                         |     |

| 1.3 Input Vector Generation                                         |     |

| 1.4 MOSFET Scaling                                                  |     |

| 1.5 Adder Experiment                                                |     |

| 1.6 Comparison of Results                                           |     |

|                                                                     |     |

| 2.0 Background                                                      | 5   |

| 2.1 Fan-Out of XOR/XNOR Gates                                       | 6   |

| 2.2 Transmission Gates                                              | 6   |

| 2.3 Inverter-base Gates                                             | 8   |

| 2.4 Proposed Structures                                             | .10 |

| 2.5 Realistic Gates                                                 | .12 |

| 2.6 Combination Circuit Design XOR/XNOR                             | .14 |

| 2.7 Basic Physical Layout Design of XOR/XNOR Gates                  | .18 |

|                                                                     | 20  |

| 3.0 Results of Simulation.                                          |     |

| 3.1 MOSFET Scaling                                                  | .22 |

| 4.0 Results of XOR Gates with HSPICE                                | .25 |

| 4.1 Results of XOR Gates with Mentor Graphic                        |     |

| 4.2 Results of XNOR Gates with Mentor Graphics                      |     |

| 4.3 Experimental                                                    |     |

|                                                                     |     |

| 5.0 Conclusion                                                      | .51 |

|                                                                     |     |

| Reference                                                           | 52  |

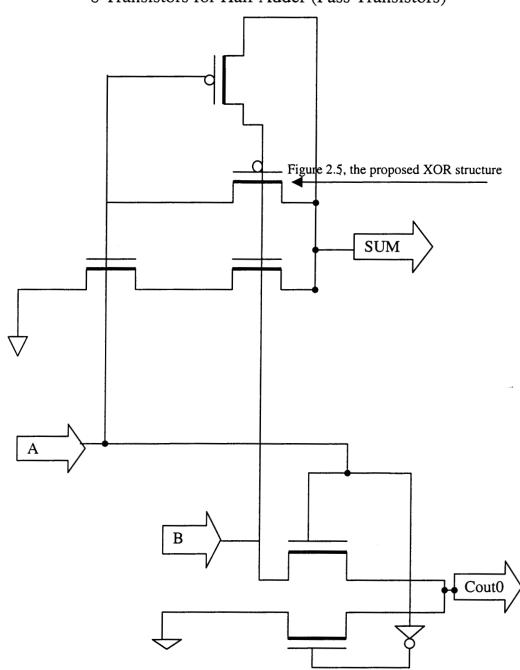

| APPENDIX A: Carry Selected Full Adder.                              |     |

| APPENDIX B: TSMC CMOS Fabrication Technology                        |     |

| APPENDIX C: HSPICE NETLIS Files.                                    |     |

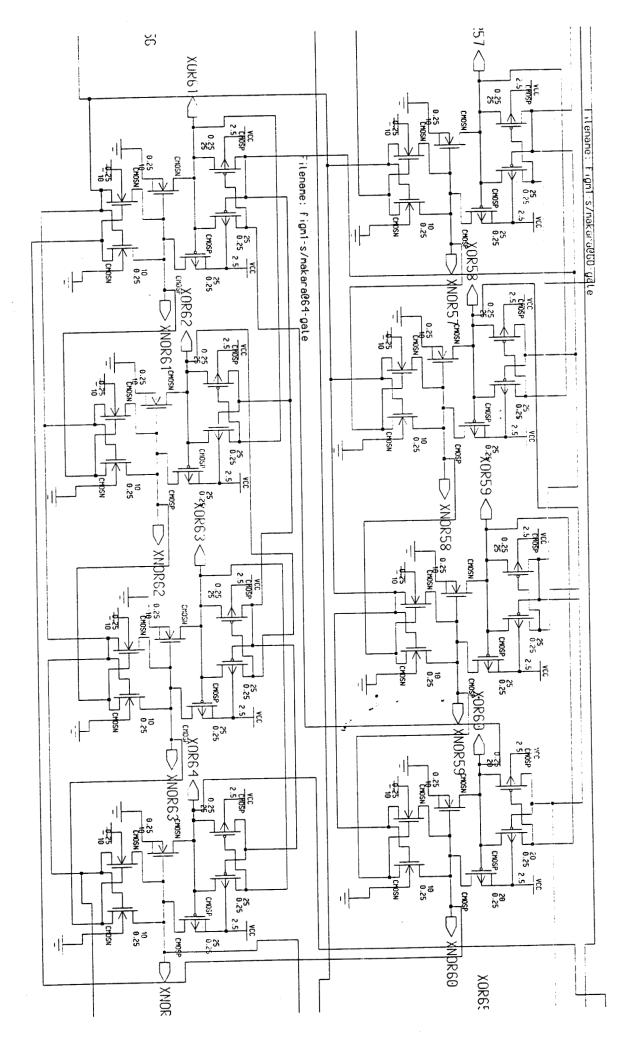

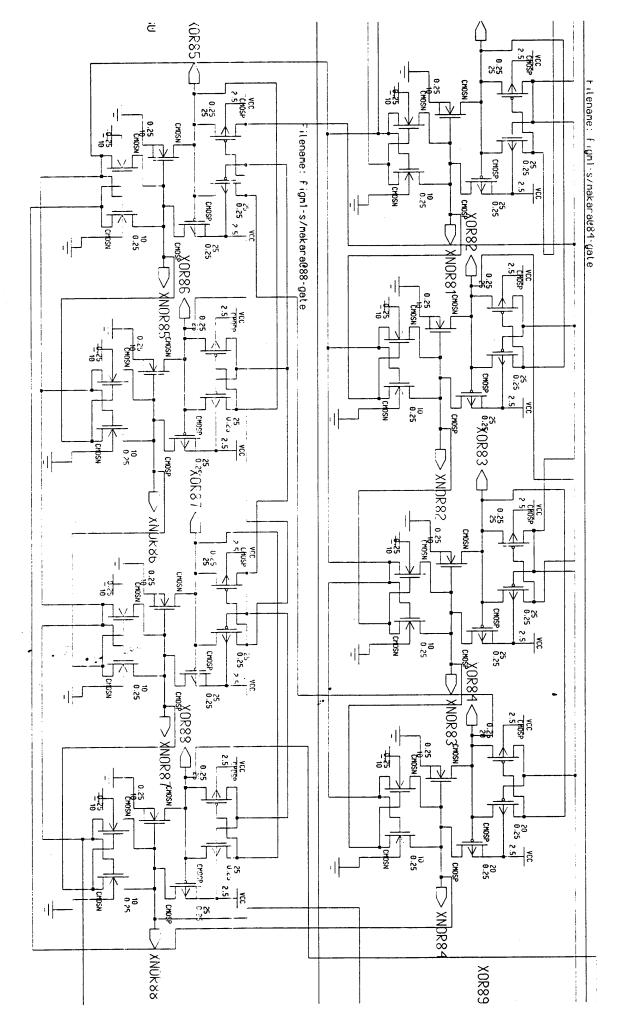

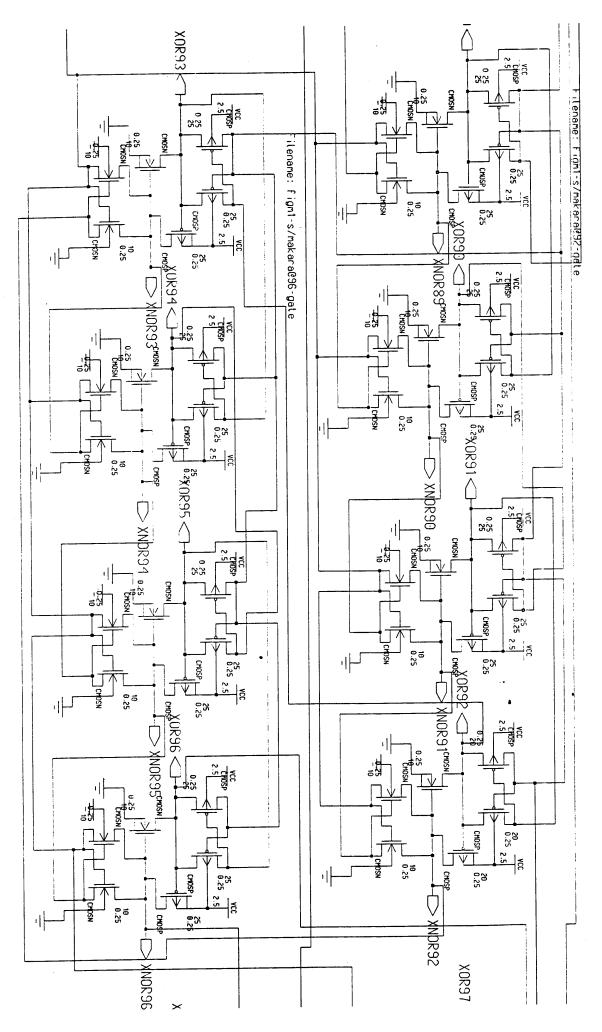

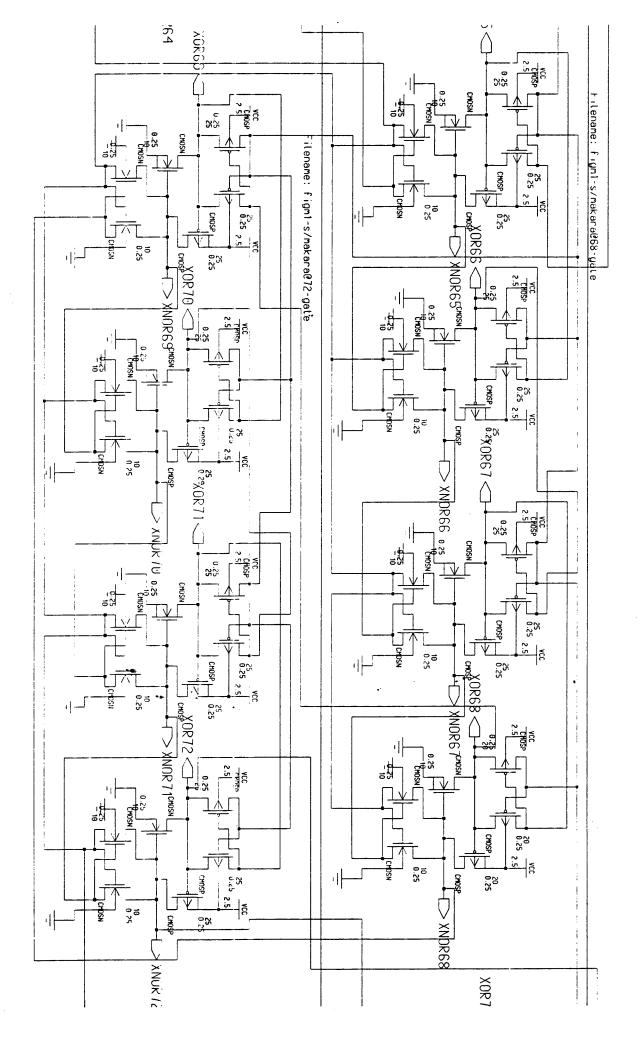

| APPENDIX D: The Layout of XOR/XNOR Works on Mentor Graphics, Design |     |

| Architecture (DA) from Figures 2.M1 to 2.M5, and Schematic of 128   | -   |

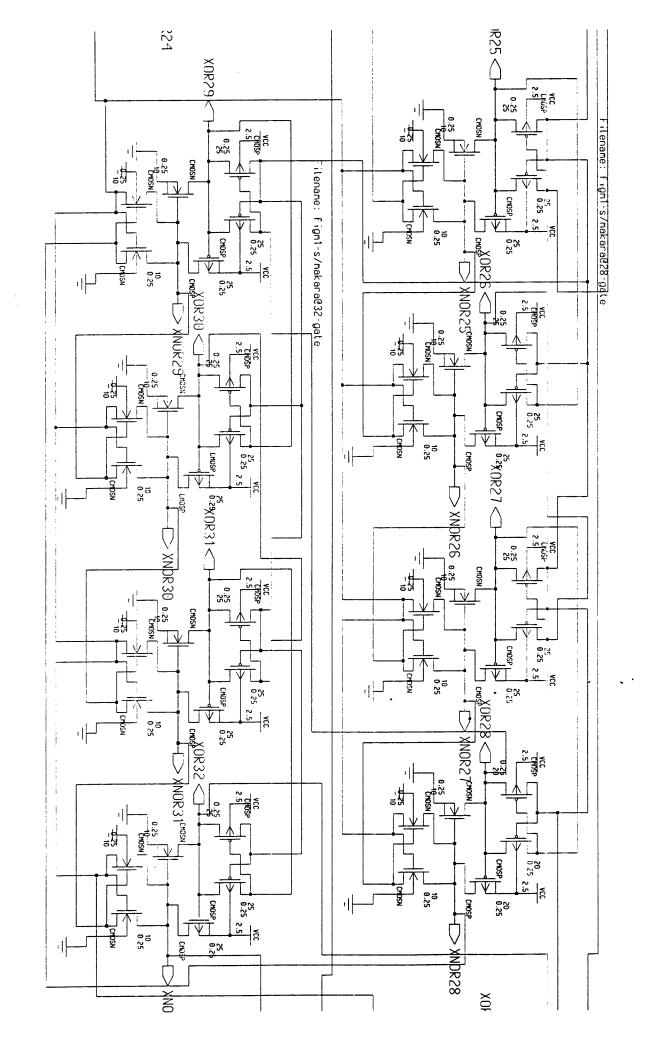

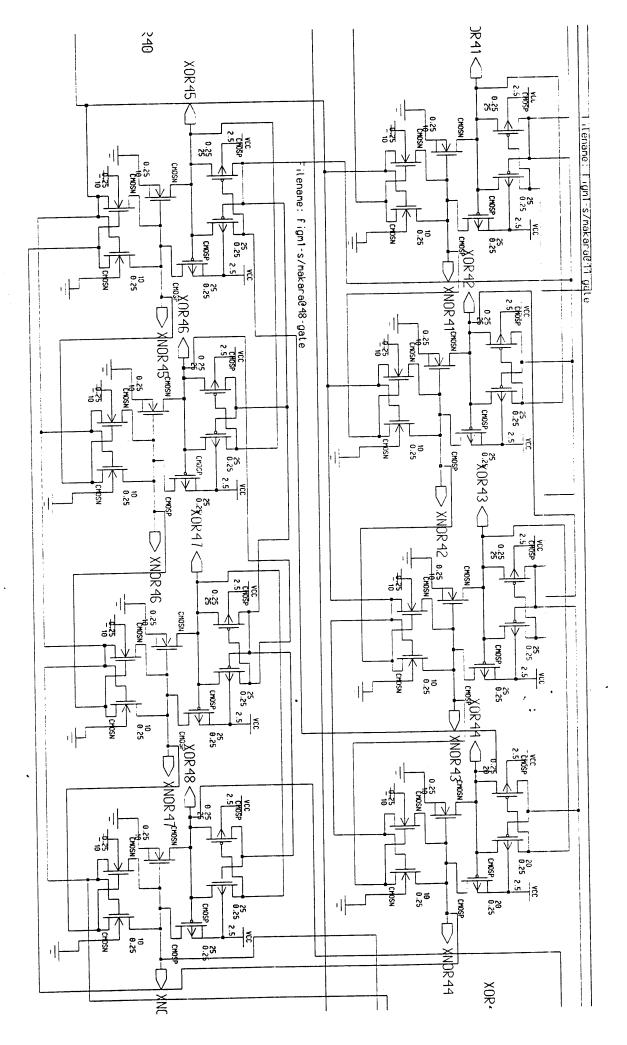

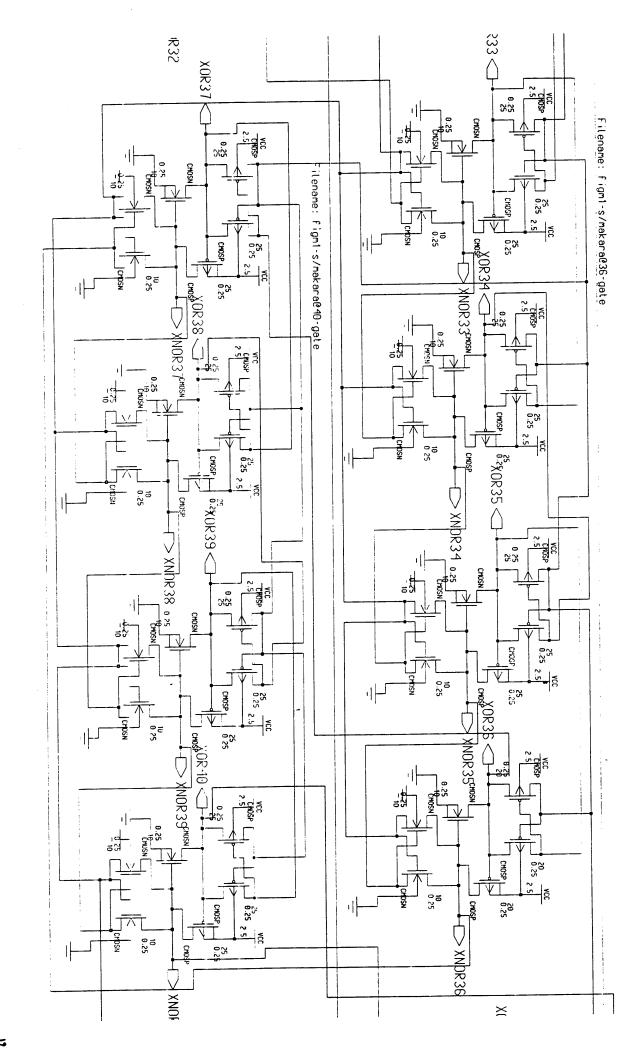

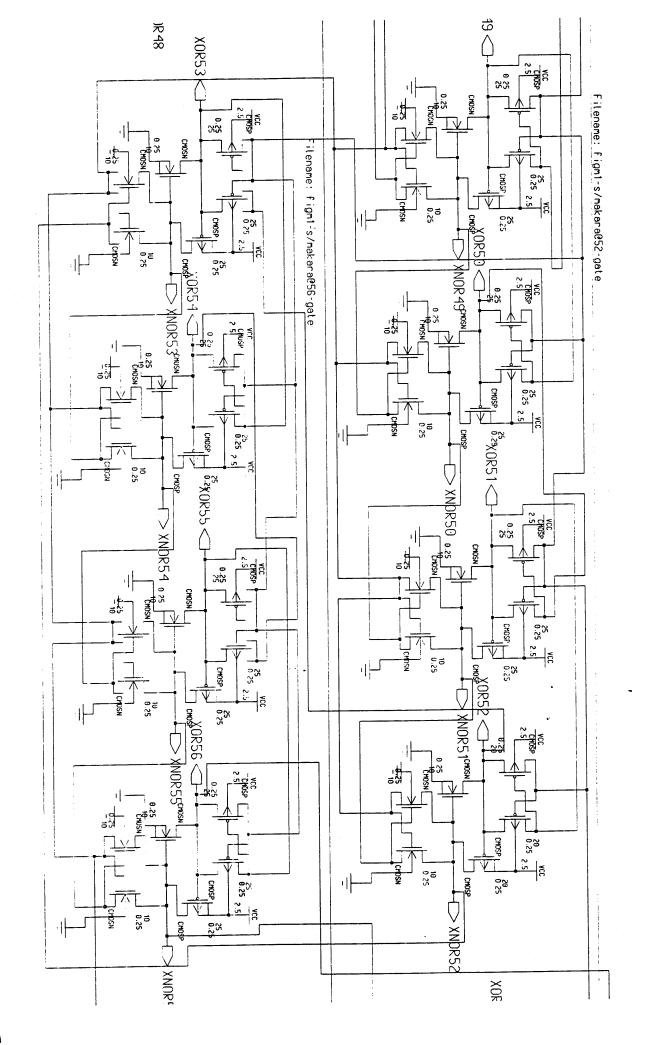

| XOR/XNOR-gates                                                      | .72 |

## List of Tables

|                                                                             | Page |

|-----------------------------------------------------------------------------|------|

| Table 1 TSMC 0.35um Fabrication Technology                                  |      |

| Table 1.1 The Function of XOR and XNOR                                      |      |

| Table 2.1 Advantage/disadvantage comparison                                 |      |

| Table 3.1 Generalized MOSFET Scaling Theory                                 |      |

| Table 3.2 Output simulation file of the parameter model for CMOSN and CMO   |      |

| TSMC 0.25µm fabrication technology                                          |      |

| Table 4.1 2.5volt Delay Time Analysis of Each XOR Structure                 |      |

| Table 4.1 2.0volt Delay Time Analysis of Each XOR Structure                 |      |

| Table 4.1 1.5volt Delay Time Analysis of Each XOR Structure                 |      |

| Table 4.1 1.0volt Delay Time Analysis of Each XOR Structure                 |      |

| Table 4.2 2.5volt Rising/Falling Time Analysis of Each XOR Structure        |      |

| Table 4.2 2.0volt Rising/Falling Time Analysis of Each XOR Structure        |      |

| Table 4.2 1.5volt Rising/Falling Time Analysis of Each XOR Structure        |      |

| Table 4.2 1.0volt Rising/Falling Time Analysis of Each XOR Structure        |      |

| Table 4.3 Comparison of Each XOR Function.                                  |      |

| Table 4.4 Average Power Dissipation from 0 through 100ns                    |      |

| Table 4.5 2.5volt with scale Vth Delay Time Analysis of Each XOR Structure  |      |

| Table 4.5 2.5volts Delay Time Analysis of Each XOR Structure                |      |

| Table 4.5 2.0volt Delay Time Analysis of Each XOR Structure                 |      |

| Table 4.5 1.5volt Delay Time Analysis of Each XOR Structure                 |      |

| Table 4.5 1.0volt Delay Time Analysis of Each XOR Structure                 |      |

| Table 4.6 2.5volt with scale Vth Rising/Falling Time Analysis of Each XOR   |      |

| Table 4.6 2.5volt Rising/Falling Time Analysis of Each XOR Structure        |      |

| Table 4.6 2.0volt Rising/Falling Time Analysis of Each XOR Structure        |      |

| Table 4.6 1.5volt Rising/Falling Time Analysis of Each XOR Structure        |      |

| Table 4.6 1.0volt Rising/Falling Time Analysis of Each XOR Structure        |      |

| Table 4.7 Comparison of Each XOR Function.                                  |      |

| Table 4.8 Average Power Dissipation XOR from 0 through 100ns                |      |

| Table 4.9 2.5volt with scale Vth Delay Time Analysis of Each XNOR           |      |

| Table 4.9 2.5volt Delay Time Analysis of Each XNOR Structure                |      |

| Table 4.9 2.0volt Delay Time Analysis of Each XNOR Structure                |      |

| Table 4.9 1.5volt Delay Time Analysis of Each XNOR Structure                |      |

| Table 4.9 1.0volt Delay Time Analysis of Each XNOR Structure                |      |

| Table 4.10 2.5volt with scale Vth Rising/Falling Time Analysis of Each XNOR |      |

| Table 4.10 2.5volt Rising/Falling Time Analysis of Each XNOR Structure      |      |

| Table 4.10 2.0volt Rising/Falling Time Analysis of Each XNOR Structure      |      |

| Table 4.10 1.5volt Rising/Falling Time Analysis of Each XNOR Structure      |      |

| Table 4.10 1.0volt Rising/Falling Time Analysis of Each XNOR Structure      |      |

| Table 4.11 Comparison of Each XNOR Function.                                |      |

| Table 4.12 Average Power Dissipation XNOR from 0 through 100ns              | 49   |

# List of Figures

| Pa                                                                            | age |

|-------------------------------------------------------------------------------|-----|

| Figure 1.1 Logic Gate of 8-bit Adder                                          | 4   |

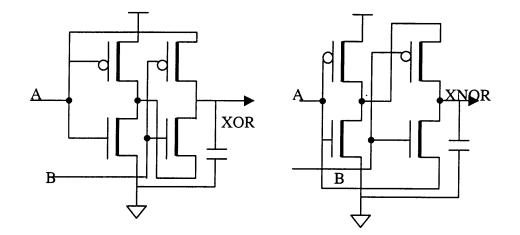

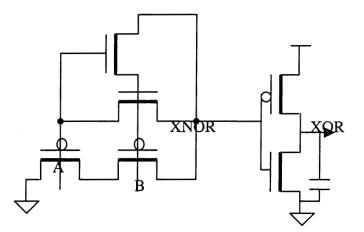

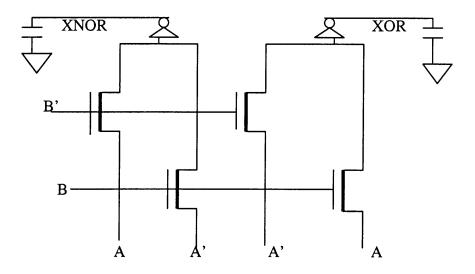

| Figure 2.1 The XOR and XNOR Functions Implemented by Transmission Gates       | 7   |

| Figure 2.2 The XOR and XNOR Functions Implemented by                          |     |

| Transmission Gates with Driving Output                                        | 7   |

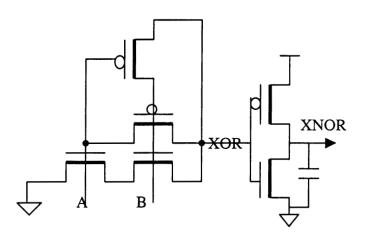

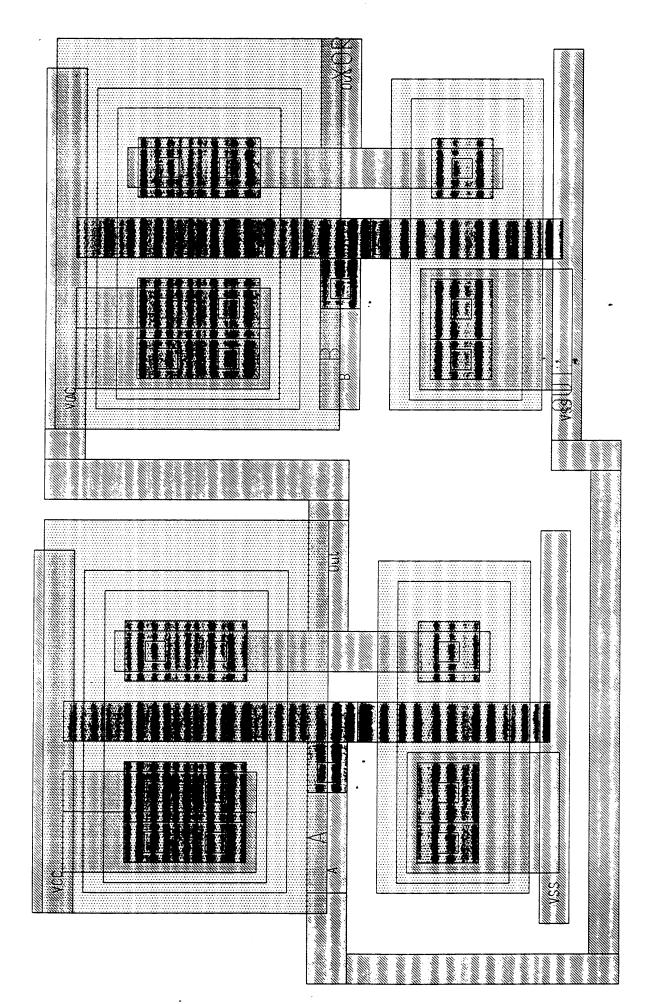

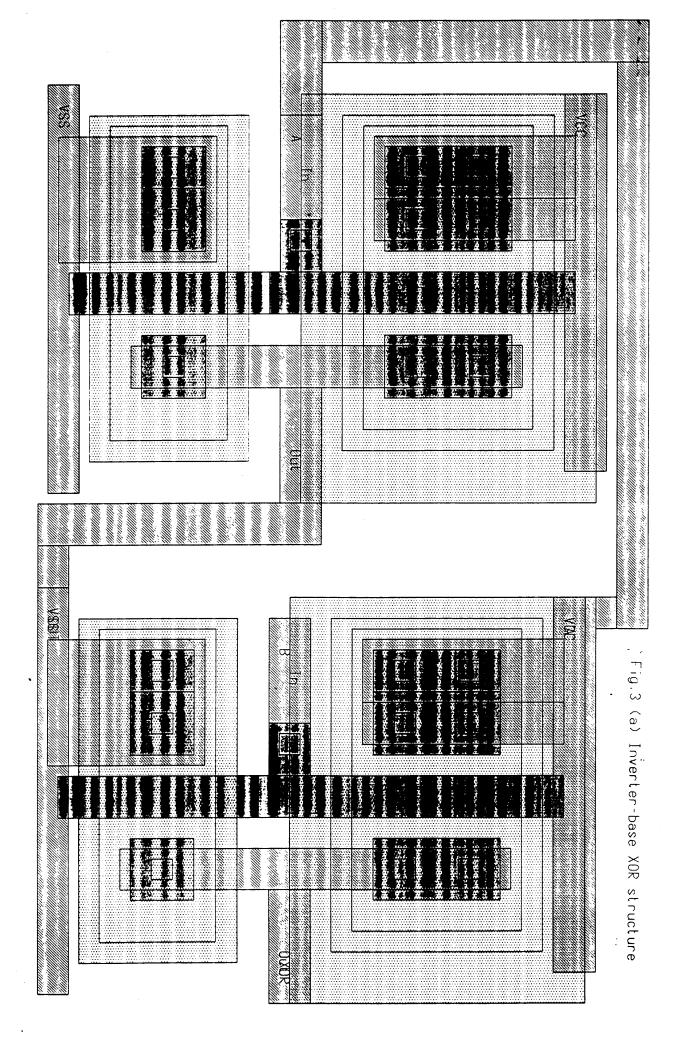

| Figure 2.3a and 2.3b (a) Inverter-base XOR structure                          |     |

| (b) Inverter-base XNOR structure                                              |     |

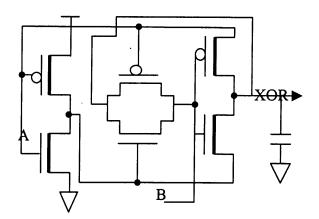

| Figure 2.4a Improved Version of XOR Structure                                 | 9   |

| Figure 2.4b Another Improved Version of Exclusive-OR Structure                | 9   |

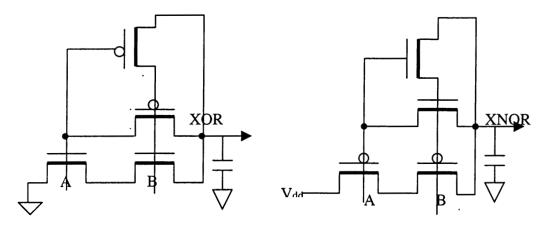

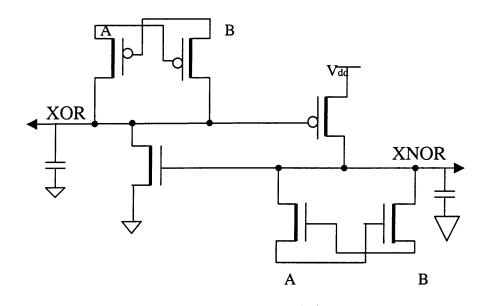

| Figure 2.5 Proposed XOR and XNOR                                              | 11  |

| Figure 2.6 The Proposed XOR Structures with Driving Output                    |     |

| Figure 2.7 The Proposed XNOR Structures with Driving Output                   | 11  |

| Figure 2.12a Realistic-simulated circuit for Figure 2.2                       | 13  |

| Figure 2.12b Realistic-simulated circuit for Figure 2.4a                      |     |

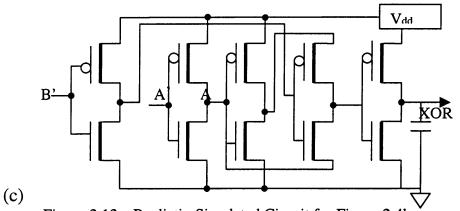

| Figure 2.12c Realistic-simulated circuit for Figure 2.4b                      |     |

| Figure 2.12d Realistic-simulated circuit for Figure 2.6                       |     |

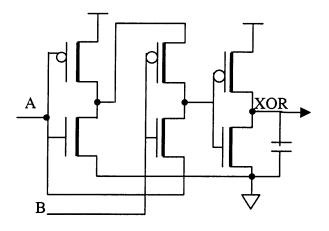

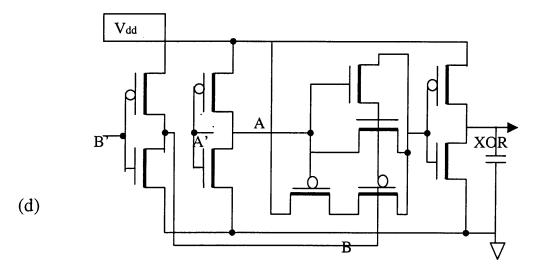

| Figure 2.7/Figure 2.M1 Full Restored Combination Circuit Design XOR/XNOR      | .15 |

| Figure 2.M2 Complimentary Pass Gate Logic                                     |     |

| Figure 2.M3 Cross Coupled Logic (input to Vad instead of Vdd-Vth)             | .16 |

| Figure 2.M4 Swing Restored Pass Gate Logic                                    |     |

| Figure 2.M5 Full Restored Combination Circuit Design XOR/XNOR Driving Output. | .17 |

| Figure 2.13 Layout Design of Figure 2.2 XNOR                                  | .19 |

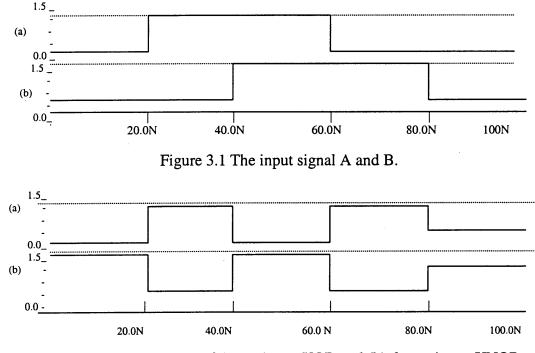

| Figure 3.1 The input signal A and signal B                                    |     |

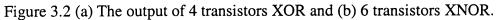

| Figure 3.2(a) The output of 4 transistors XOR and (b) 6 transistors XNOR      |     |

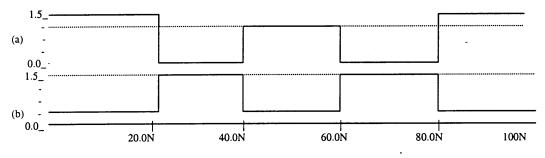

| Figure 3.3(a) The output of 4 transistors XNOR and (b) 6 transistors XOR      |     |

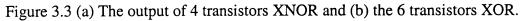

| Figure 3.4(a) The output of 4 transistors XOR and (b) the 6 transistor XNOR   |     |

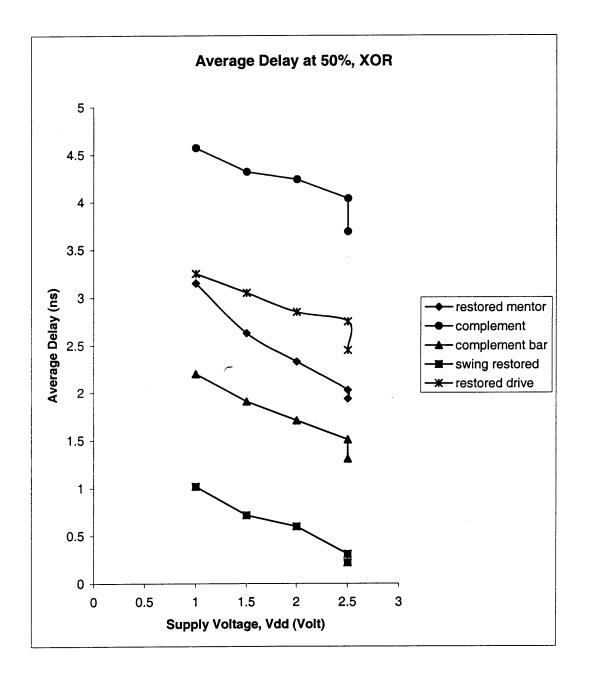

| Figure 4.1 Average Delay                                                      |     |

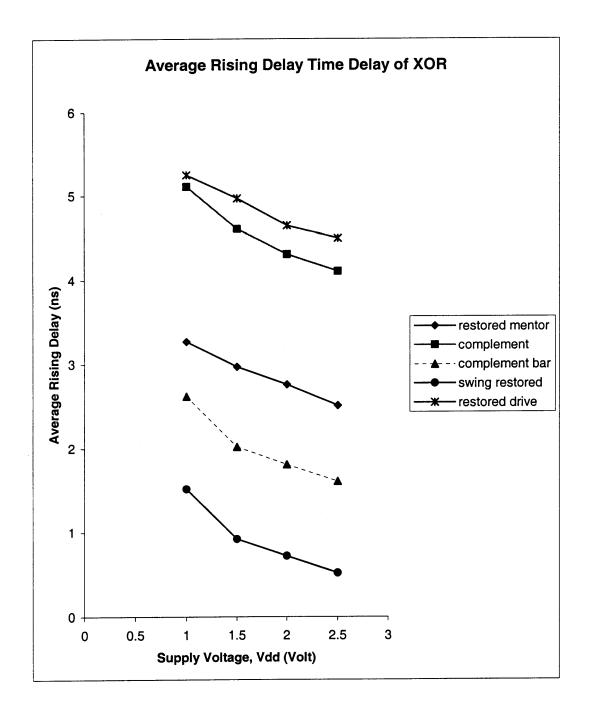

| Figure 4.2 Average Rising Delay                                               |     |

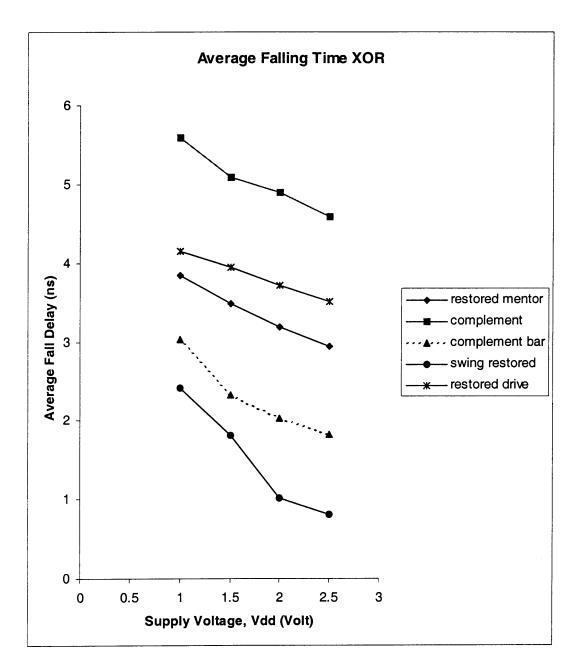

| Figure 4.3 Average Falling Delay                                              |     |

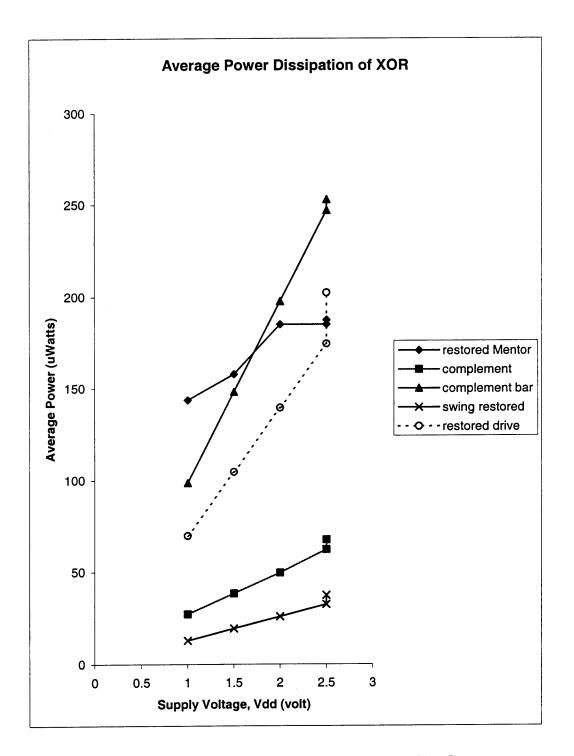

| Figure 4.4 Average Power Dissipation                                          |     |

| Figure 4.5 Average Delay XOR Gates                                            |     |

| Figure 4.6 Average Falling Delay XOR Gates                                    |     |

| Figure 4.7 Average Rising Delay XOR Gates                                     |     |

| Figure 4.8 Average Power Dissipation XOR Gates                                |     |

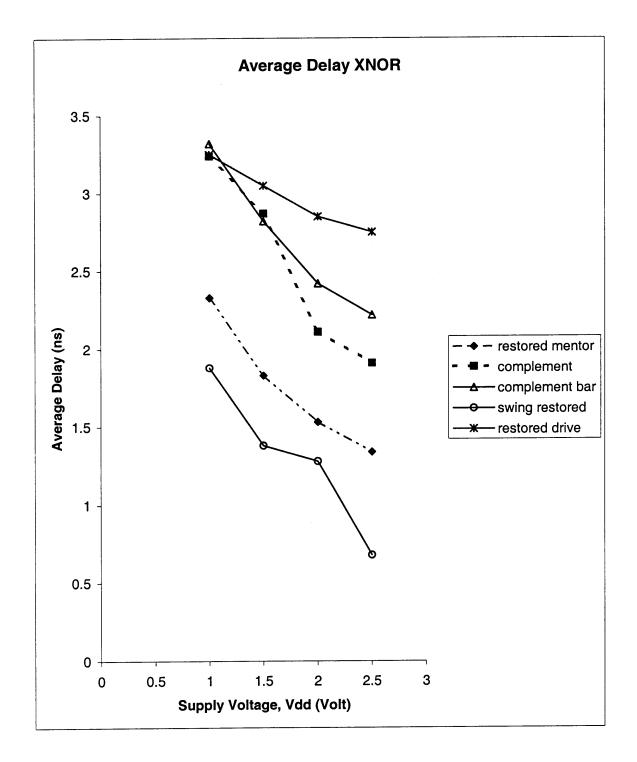

| Figure 4.9 Average Delay XNOR Gates                                           |     |

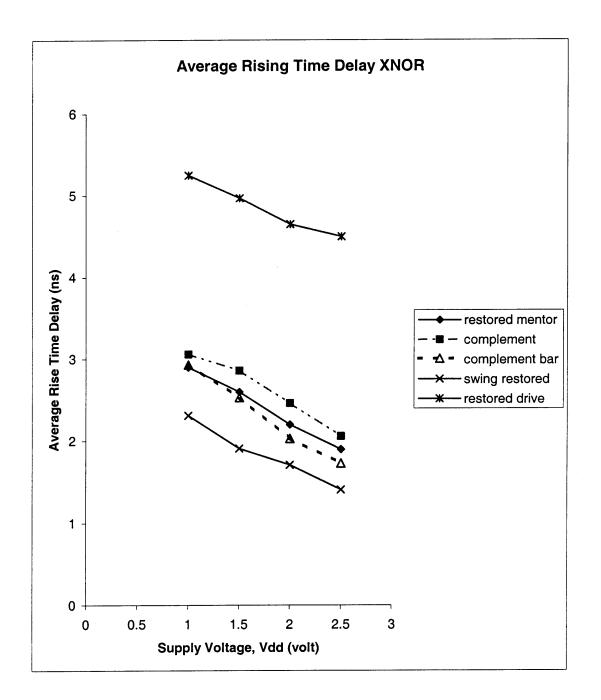

| Figure 4.10 Average Rising Delay XNOR                                         |     |

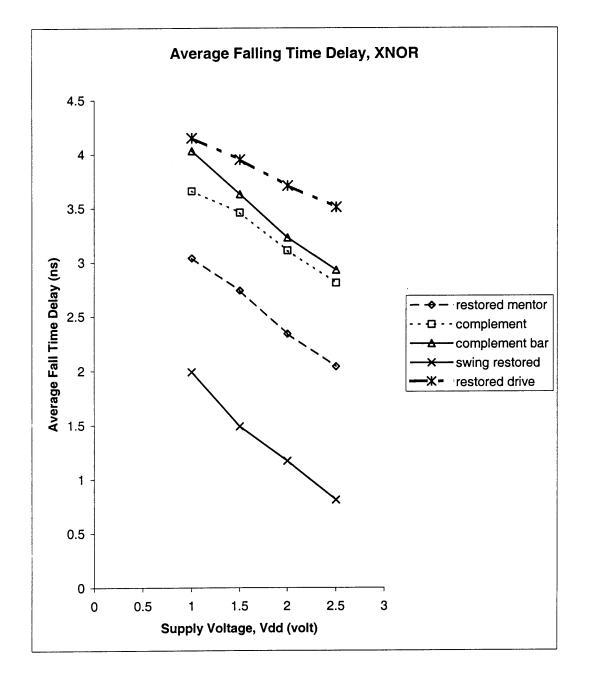

| Figure 4.11 Average Falling Delay Gates                                       | 48  |

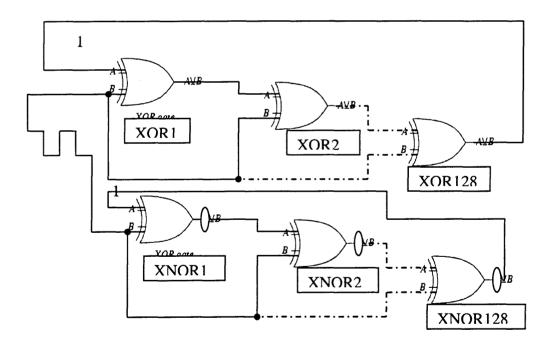

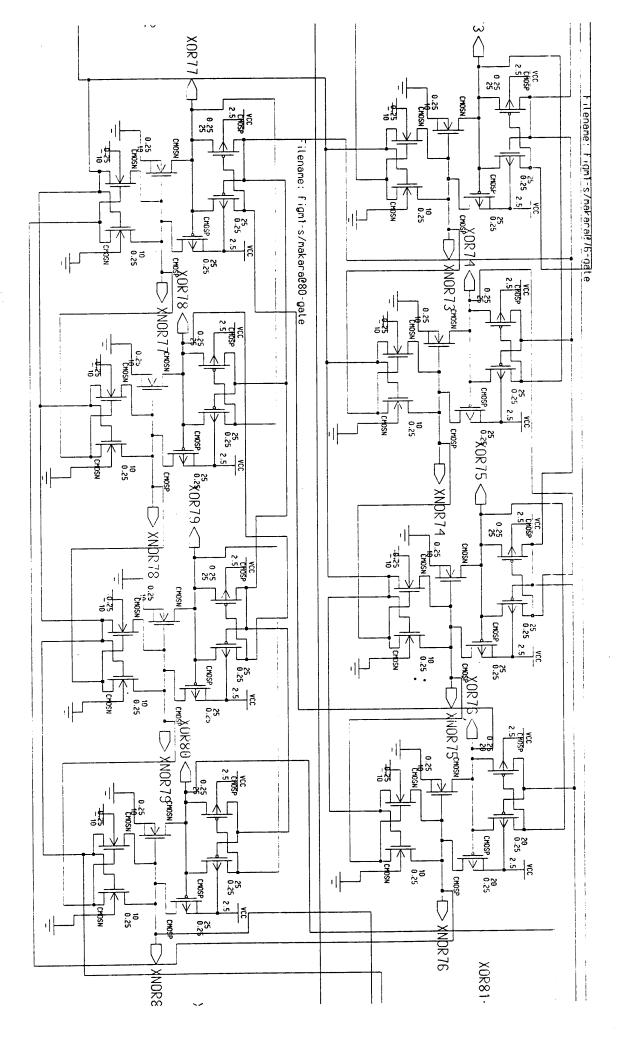

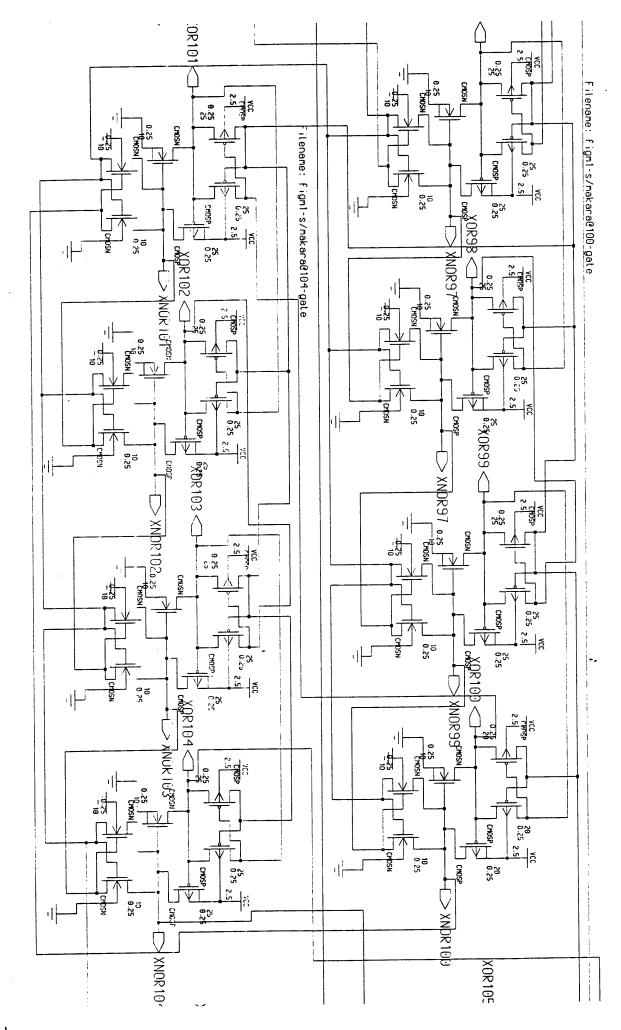

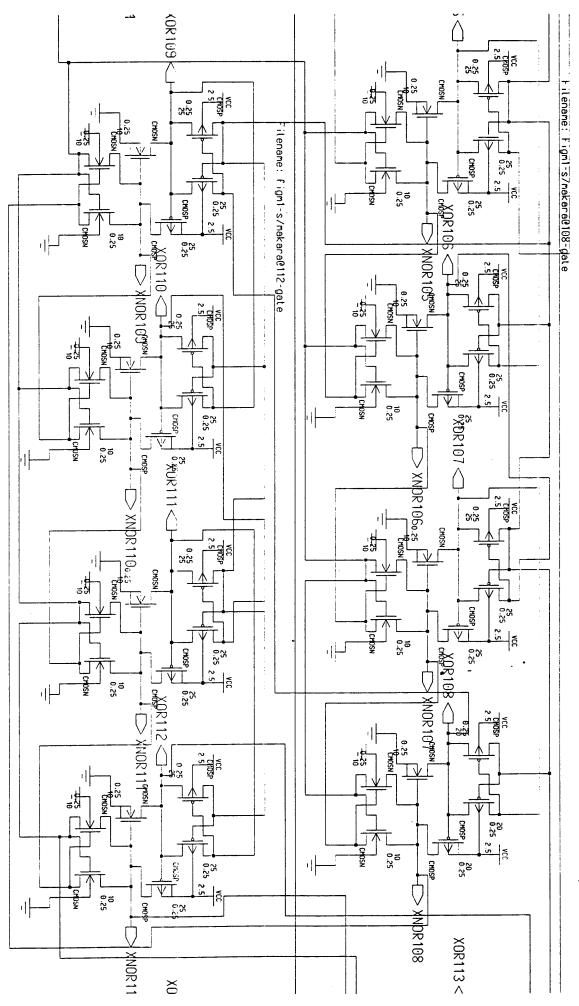

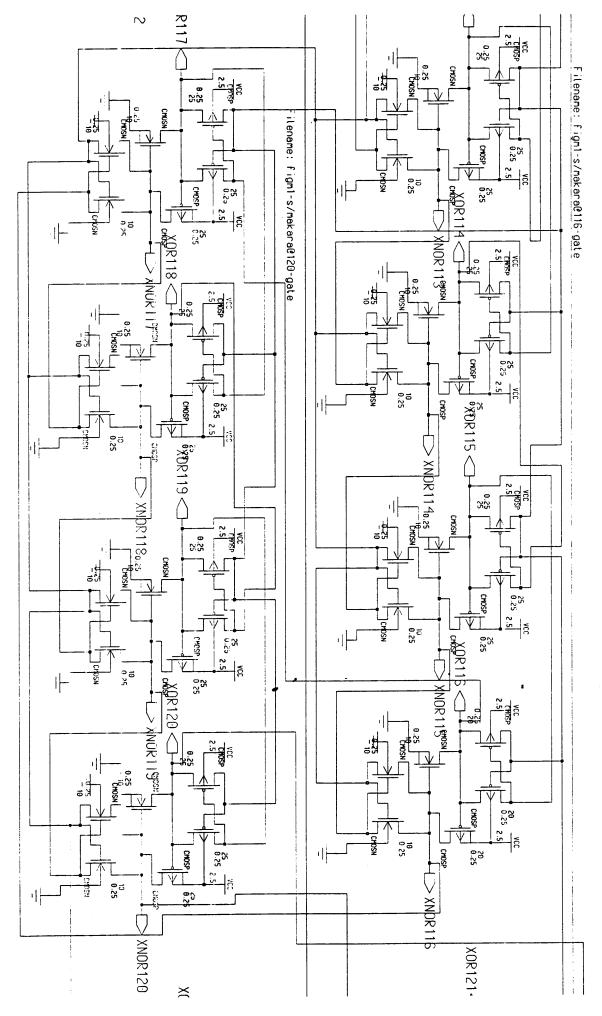

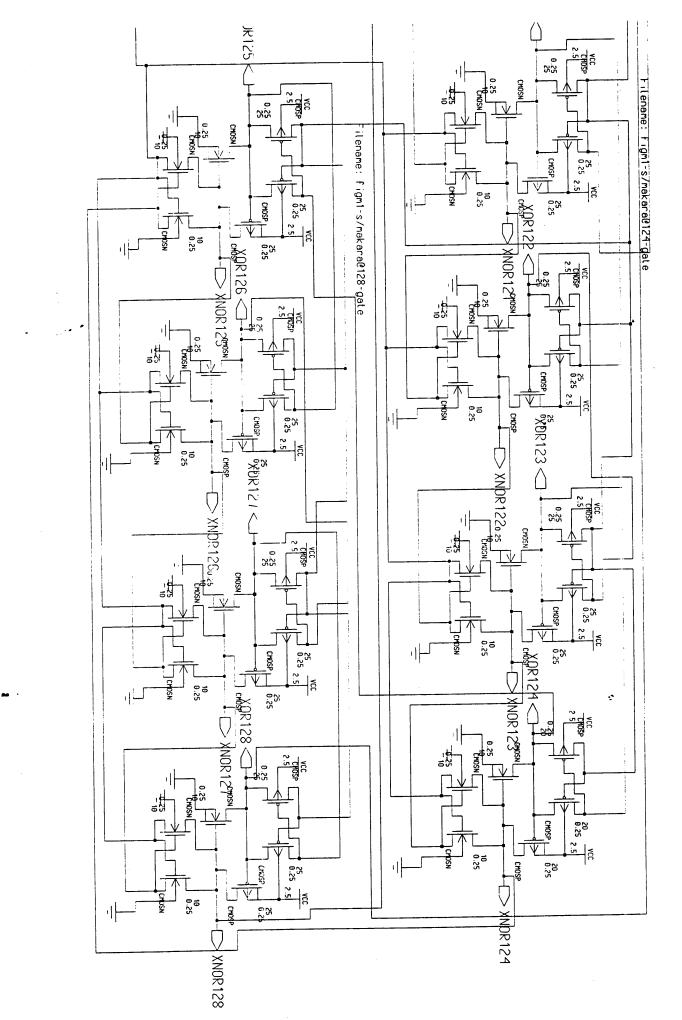

| Figure 4.12 Series Connection of 128 XOR-Gates                                | 50  |

## Abstract

## **Comparison of CMOS XOR and XNOR Gate Design**

Makara Tang

M.S, OGI School of Science and Engineering at OHSU August 2002

Thesis Advisor: Dr. Shih-Lien Lu

Two new methods are proposed to implement the exclusive-OR and exclusive-NOR functions at the transistor level. The first method uses non-complementary signal input and the least number of transistors. The second method improves the performance but two additional transistors are utilized. The proposed method uses the same number of transistors but adds with more drive capability. These circuits were first implemented using a Physical Layout Design tool produced by Mentor Graphics. These layouts were extracted and simulated using circuit simulator HSPICE and ACCUSIM. Delay and power consumption of these circuits were characterized and compared with previously known designs.

#### 1.0 Synopsis

Complementary Metal Oxide Semiconductor (CMOS) technology is advancing for microprocessors. Supply voltage (V<sub>dd</sub>) and transistor size continue to scale smaller sizes with lower power dissipation and faster microprocessors. The exclusive-OR (XOR) and exclusive-NOR (XNOR) functions are popular gates in microprocessors. The XOR/XNOR gates are fundamental unit circuits used in comparators, parity checkers, error detectors and correctors, multipliers, adders (ALU, AGU), etc. Many circuit implementations of XOR/XNOR gates have been proposed previously. One circuit that is implement the XOR/XNOR gates was published by Jyh-Ming Wang, Sung-chuan Fang, and Wu-shiung Feng [12]. In their work, Jyh-Ming Wang compared several circuit implementations using supply voltage (V<sub>dd</sub> = 5volt) with TSMC 0.8µm fabrication technology.

This thesis proposes several circuit-level implementations of XOR/XNOR gates. These circuits were simulated using a circuit simulator (HSPICE) with various supply voltages. The various supply voltages are important because as technology continues to scale to smaller feature size, supply voltage (V<sub>dd</sub>) also needs to scale down for reliability and power reduction [9].

The optimizations in this thesis have been performed through simulations with HSPICE using various supply voltages from  $V_{dd} = 1$  volt to  $V_{dd} = 2.5$  volt on TSMC 0.35µm fabrication technology. First part in thesis simulations with HSPICE using TSMC 0.35µm fabrication technology is devoted to re-evaluation of these circuit implementations using more advanced technology. Second part of the thesis proposes two new combination XOR/XNOR circuit implementations and simulated with Mentor Graphic using TSMC 0.25µm fabrication technology. The Design Architecture (DA) tool was used for designing the circuits and the ACCUSIM tool was used for simulation. The optimization in this thesis has also been performed through simulations with Mentor Graphics Software using various supply voltages from  $V_{dd} = 1$  volt to  $V_{dd} = 2.5$  volt on TSMC 0.25µm fabrication technology.

1

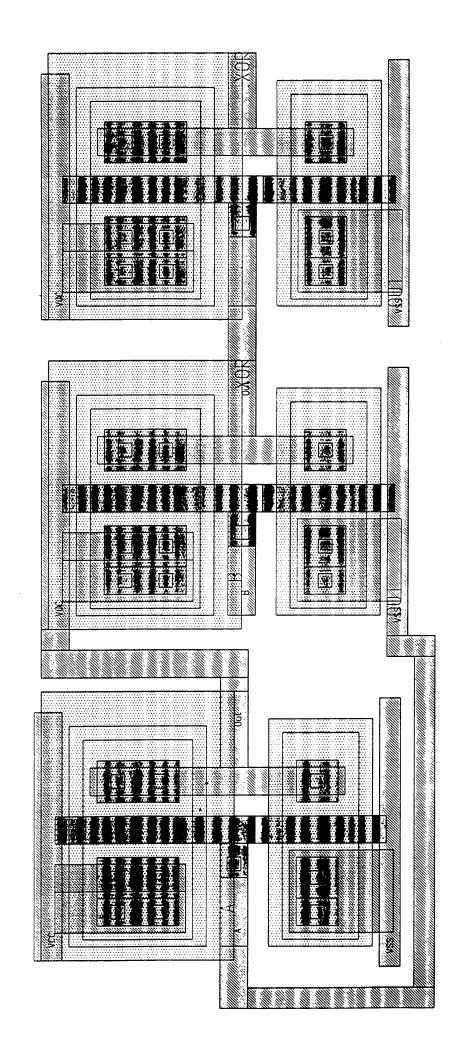

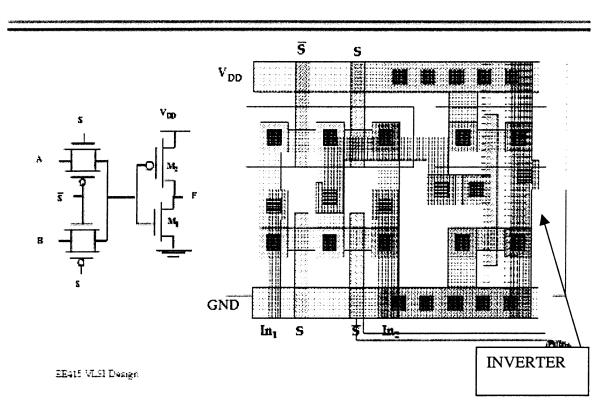

#### 1.1 Physical Layout

The Mentor Graphics Physical Layout tool was used to design the XOR/XNOR circuits. The Lambda value was used, specifying Lambda equal to 0.125 $\mu$ m ( $\lambda$ =0.125). In addition, the supply voltage used was V<sub>dd</sub> = 2.5volt with TSMC 0.25 $\mu$ m fabrication technology for this Physical Layout Design [5]. The stick rule was used for the component layout and applied the design rule applied for the component layout space requirements. The dimension-width scaling of the gate-area ratio in Complementary Metal Oxide Semiconductor P-channel (CMOSP) and Complementary Metal Oxide Semiconductor N-channel (CMOSN) is 3:1. The physical W/L sizes of CMOSP and CMOSN are 2.1 $\mu$ m/0.35 $\mu$ m and 1.05 $\mu$ m/0.35 $\mu$ m respectively, in order to meet the optimal design of low power with high performance.

#### 1.2 Fan-Out

The term "fan-out" as used with digital circuits describes the maximum number of load gates (circuits) of similar design as the driver gate that can be connected to the output of XOR/XNOR thus helping to drive the output signal for the driver gate [12].

#### **1.3** Input Vector Generation

Non-complementary [12] inputs, signal A and signal B vectors, were generated so as to test the design in four cases: AB=00, AB=01, AB=10, and AB=11. Also the complementary inputs, signal A and signal A', signal B and signal B' vector, were generated to test the design in four cases: AB=00, AB=01, AB=10, and AB=11. The XOR logic gate operates based on a truth table where if input signal A and signal B are the **same** value then the output signal is "LOW." If input signal A and signal B are **different** values then the output signal is "HIGH." The exclusive-OR and exclusive-NOR functions are shown in Table 1.1. Assuming the input signals are A and B, then the exclusive-OR of A and B, denoted  $A \oplus B$  is logically equivalent to A'B+AB'; and the exclusive-NOR of A and B, denoted as A  $\otimes$ B, is logically equivalent to AB+A'B'.

| A | В | XOR | XNOR |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 1   | 0    |

| 1 | 0 | 1   | 0    |

| 1 | 1 | 0   | 1    |

| Table 1.1                 |  |  |

|---------------------------|--|--|

| Functions of XOR and XNOR |  |  |

Exclusive-OR A XOR  $B = A \oplus B$ = A'B+AB'

| Exclusive-NOR | A XNOR $B = A \otimes B$ |

|---------------|--------------------------|

|               | = AB + A'B'              |

#### 1.4 MOSFET Scaling

MOSFET Scaling determines how threshold voltage should be decreased by the scaling factor, K, in proportion to the power supply voltage. In this work, MOSFET Scaling is applied to CMOSN and CMOSP from the TSMC 0.25 $\mu$ m fabrication technology. According to the fundamentals of modern VLSI devices by Yuan Taur and Tak H. Ning [9], when the TSMC fabrication technology scales down the threshold voltage (Vth), it is also necessary to scale down the physical dimension.

#### **1.5** Adder Experiment

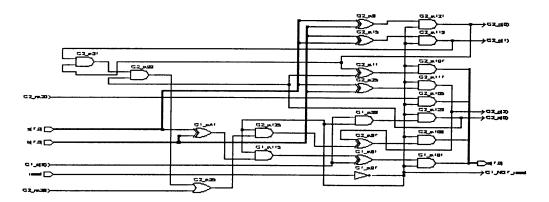

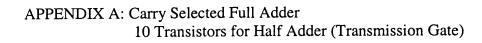

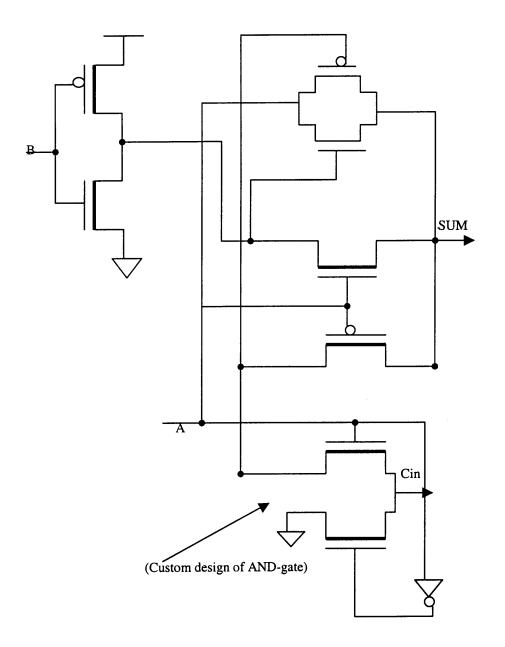

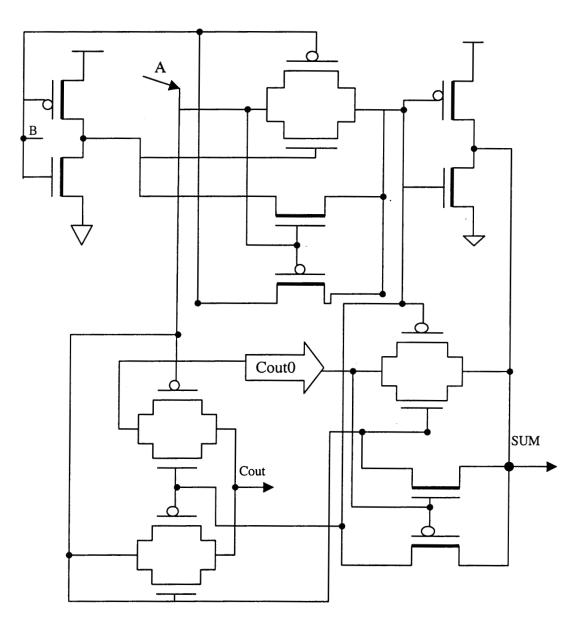

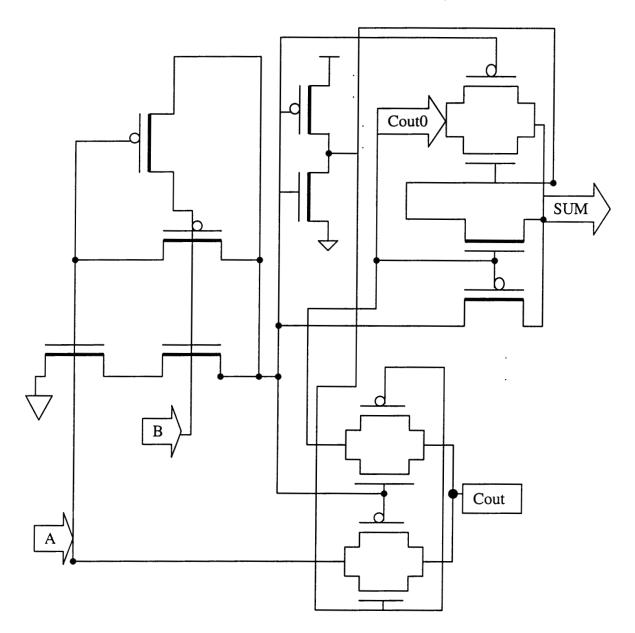

The XOR gates that were chosen for the design of the adders listed in appendix A were the XOR transmission gate (Figure 2.1) and the proposed XOR structure (Figure 2.5). The advantage of the proposed XOR structure is the Pass-Transistor and the ability to transmit the signal HIGH (or "1") and signal LOW (or "0") directly from the input. The disadvantage of the proposed XOR structure is that the Pass-Transistor does not scale well. The advantage of the XOR transmission gate is that it is a powerful device that scales well, and has a full swing signal level. The disadvantage of the XOR transmission gate is its complementary inputs. As in Figure 1.1, the 8-bit adder given a general idea of how many XOR gates need to use. Microprocessors use the XOR gate everywhere so they are very important.

Figure 1.1, Logic Gate of 8-bit Adder

#### 1.6 Comparison of Results

Results were compared between our proposed XOR gates and other conventional XOR gates, comparing average power dissipation and average delay measuring from 50 percent of the waveform between the inputs and the outputs. We also compared average rising time delay measuring from 10 to 90 percent of the waveform between the inputs and the outputs and average falling time delay measuring from 90 to 10 percent of the waveform between the inputs and the outputs [12]. Compared data analysis was also done for the average power dissipation, average delay, and average rising/falling delay time. For average delay and average rising/falling delay time must fit in the negative linear slope. Also, the average power dissipation must fit in the positive linear slope [11].

#### 2.0 Background

The exclusive-OR (XOR) and exclusive-NOR (XNOR) functions are fundamental for various circuits used in comparators, parity checkers, full adders, multipliers, etc. There are two kinds of MOS; the N-channel Metal Oxide Semiconductor (NMOS) and the P-channel Metal Oxide Semiconductor (PMOS). It is well known that NMOS transistor can transmit the signal "LOW" (or "0") completely, but it has poor performance when transmitting the signal "HIGH" (or "1"). If one takes a NMOS transistor to implement a switch device, a control signal is added to the gate terminal and sets one end of the signal "HIGH", where the other end will drop to the threshold voltage of NMOS, V<sub>nth</sub>. The PMOS transistor can pass a signal "HIGH" fully but handles a signal "LOW" poorly. As a switch device, if a signal "LOW" appears on the source end of the PMOS transistor, the destination end will not sink to signal "LOW", as it will keep a higher than threshold voltage of PMOS, [V<sub>pth</sub>].

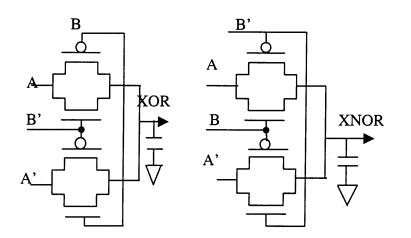

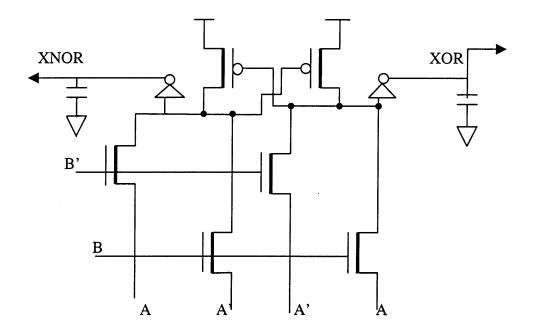

Based on the transmission gate theory, the realized XOR/XNOR circuit uses transmission gates (Figure 2.1). This structure needs only four transistors, but the complementary inputs can lose driving capacity. In general if the output signal of a circuit comes from V<sub>dd</sub> or V<sub>ss</sub> directly, this circuit has drive capability. However, it is well known that a transmission gate has no drive capability. Using this technique, the circuit can have configurations of XOR and XNOR as in Figure 2.1, but adds an inverter behind each case. Therefore, the improved versions of the transmission gates shown in Figure 2.1 are illustrated in Figure 2.2 as transmission gates with driving output.

#### 2.1 Fan-Out of XOR/XNOR Gates

The fan-out of a logic gate is the total number of gate inputs that are driven by a gate output. This is usually expressed in terms of some default gate size. For instance, one might express the loading of a minimum-sized inverter as unity, and capacitor load are between 1pF and 5pF. The circuit implementations shown in Figures 2.2, 2.4b, 2.6, 2.12a, 2.12c, and 2.12d with two input XOR/XNOR gates and four input XOR/XNOR gates all have a fan-out of one. Also, in the combination-circuits implementations shown in Figures 2.M2, 2.M3, and 2.M5, the two input XOR/XNOR gates and the four input XOR/XNOR gates all have a fan-out of one.

When the amount of fan-out is small, the poor signal level can still drive other circuits correctly. If the amount of fan-out is no longer small or the poor signal has to pass through several improper transistors, i.e., transmit signal "HIGH" by NMOS or pass signal "LOW" by PMOS, then the poor signal level may degenerate and no longer be guaranteed to work right. In order to overcome the individual defects, combining the NMOS and the PMOS yields a transmission gate that can pass both signal "HIGH" and signal "LOW" with excellent performance.

#### 2.2 Transmission Gates

Although a CMOS transmission gate has better quality, there is full swing signal in a CMOS transmission gate, i.e., it needs complementary signal values to control the gates of PMOS and NMOS. Usually, an inverter is needed to generate a complementary input. Conventionally, a logical circuit can be realized with a canonical CMOS transistor. According to transmission gate theory [7] if a high impedance state is available, fewer transistors can be used. The performances with the proposed design are better than the past designs [5] and are proven after a careful analysis of appropriate simulations.

Figure 2.1 The XOR and XNOR Functions Implemented by Transmission Gates.

Figure 2.2 The XOR and XNOR Functions Implemented by Transmission Gates with Driving Output.

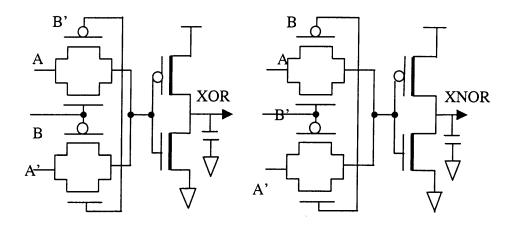

#### 2.3 Inverter-Base Gates

Based on the inverter configuration, two inverters can be arranged appropriately for the XOR function as well as the XNOR structure. The circuits are shown in Figure 2.3. For the structure shown in Figure 2.3(a), when input signal A is "HIGH", input signal A' must be "LOW". The signal A and signal A'

are connected to the V<sub>dd</sub> end of PMOS and the V<sub>ss</sub> end of NMOS in the second inverter. The second inverter functions like a standard inverter, and outputs the signal B' is the output signal of XOR/XNOR gates. Therefore, the output signal of the XOR/XNOR gates will be a perfect AB' signal. On the other hand, when the input signal A is "LOW", input signal A' must be "HIGH". The output of the inverter will be a poor signal B because it transmits a signal "HIGH" by NMOS and a signal "LOW" by PMOS. That is, if only four transistors are used to implement an XOR function based on the inverter configuration, its output will be complete on signal AB' but poor on an A'B signal. An additional transmission gate can correct the problem. In Figure 2.4(a) [7], when input signal A is "HIGH" the output of the structure is signal B', as described above, the additional transmission does nothing. It will be a good AB' signal level. When input signal A is "LOW", the transmission gate will pass signal B to the output end directly and fully. Hence the output will be a good A'B signal level. This function will be complete on all of the input cases. In Figure 2.4(b), an additional tailing inverter can also improve the poor signal coming from the output end of the four transistors XNOR structure, and output the good signal level. For these two cases, they do not need the complementary signal inputs and the driving property is better than Figure 2.1 as well. However, these structures have some disadvantages such as not having full driving capability on the output end, or more delay time.

Figure 2.3(a) Inverter-Base XOR Structure (b) Inverter-Base XNOR Structure.

Figure 2.4(a) Improved Version of XOR Structure.

Figure 2.4(b) Another Improved Version of XOR Structure.

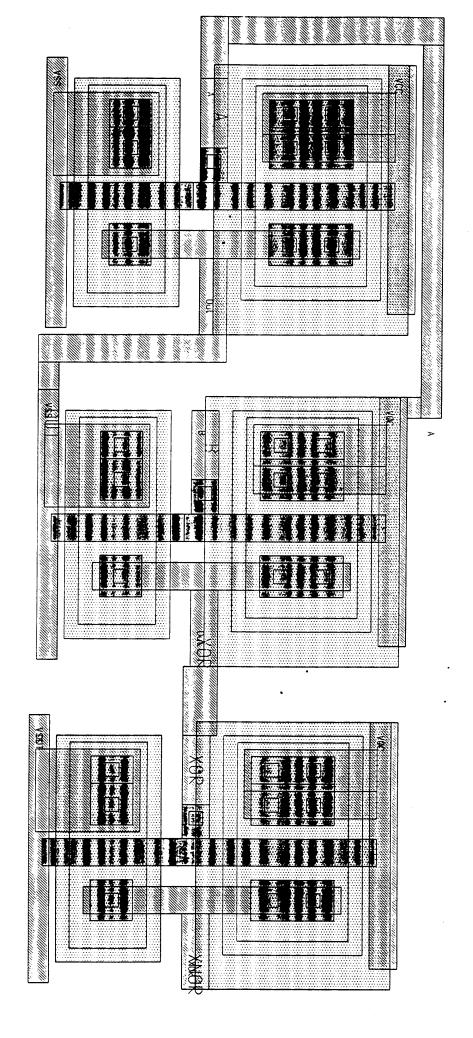

#### 2.4 **Proposed Structures**

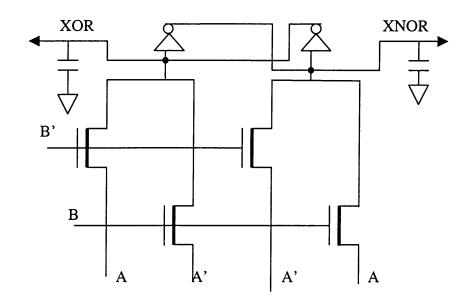

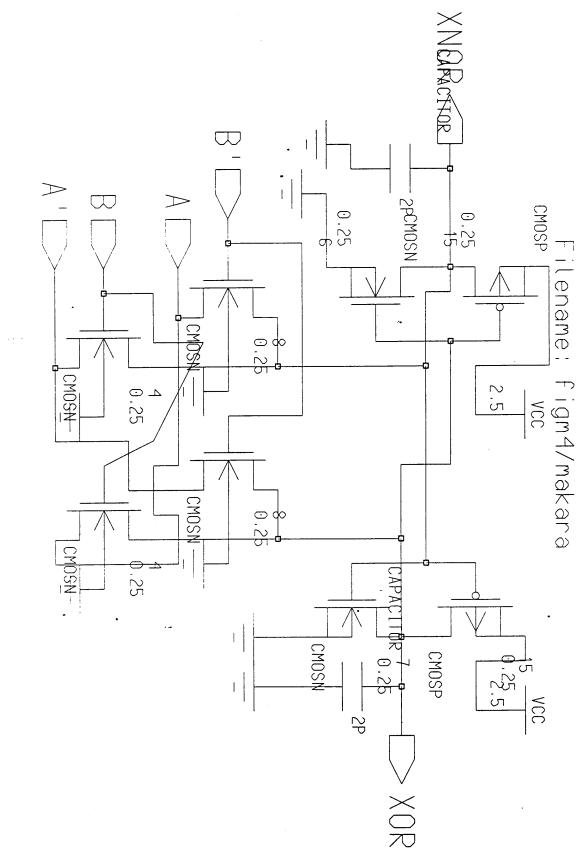

For the four transistor designs, the proposed structures require noncomplementary inputs and their output is nearly perfect [12]. The configurations for the proposed XOR and XNOR structures are shown in Figure 2.5. For analysis of the XOR structure the output signals are applied to the inputs to test the XOR gates with the values as AB=01, AB=10, and AB=11 were completed with good output signals. For an incomplete output signal, when applied the input signal to test the XOR gates with the values as AB=00, each PMOS will be on and will pass a poor "LOW" signal level to the output end. That is, if the input signal to test the XOR gates with the values as AB=00, the output will have a threshold voltage  $|V_{pth}|$ , a little higher than "LOW." For the XNOR function, the output signal in the case of AB=00, AB=01, and AB=10 will be complete. When AB=11, each NMOS will be on and pass the poor "HIGH" signal level to the output end.

The proposed structure discussed above uses four transistors and does not have driving output. By cascading a standard inverter (fan-out) to the XNOR circuit, a new type of XOR, as shown in Figure 2.6 will have a driving output, and the signal level at the output end will be perfect in all cases. The same technique may use structure as shown in Figure 2.7.

Figure 2.5 Proposed XOR and XNOR Structures.

Figure 2.6 The Proposed XOR Structure with Driving Output.

Figure 2.7 The Proposed XNOR Structure with Driving Output.

#### 2.5 Realistic Gates

All of the six transistor structure and the previous ones using transmission gates with driving output (Figure 2.2), improved version of XOR structure (Figure 2.4(a)), another improved version of XOR structure (Figure 2.4(b)), and the proposed XNOR structures with driving output (Figure 2.6) were simulated under nearly realistic conditions to determine drive capability. For the XOR structure, the circuit was redesigned as a realistic-simulated circuit as shown in Figure 2.2 (Figure 2.12(a)), Figure 2.4(a) (Figure 2.12(b)), Figure 2.4(b) (Figure 2.12(c)), and Figure 2.6 (Figure 2.12(d)).

The output waveform of an inverter will be a more realistic signal in the physical design. For convenience, we generate input signal A' and input signal B' from actual simulated realistic inverters. The signals displayed at the input ends of the XOR function will be signal A and signal B, and the output value at the output end of the XOR function will be  $(A \oplus B)$ . In order to determine the driving capability, an additional capacitor is connected to the output end of each case. Then the driving capability can be determined by the capacitor rising time and falling time. If a circuit has strong driving output, the rising time and falling time will be shorter than the one with poor driving output. If one uses the proposed methods of four transistors to drive canonical CMOS circuits, it can still work correctly. When the output levels of both four transistor cases are poor, an added tailing inverter can improve the defect, and the driving capability is present for the proposed six transistor version, and one can utilize it as a generalized XOR or XNOR function.

Figure 2.12a Realistic-Simulated Circuit for Figure 2.2.

Figure 2.12b Realistic-Simulated Circuit for Figure 2.4a.

Figure 2.12c, Realistic-Simulated Circuit for Figure 2.4b.

Figure 2.12d Realistic-Simulated Circuit for Figure 2.6.

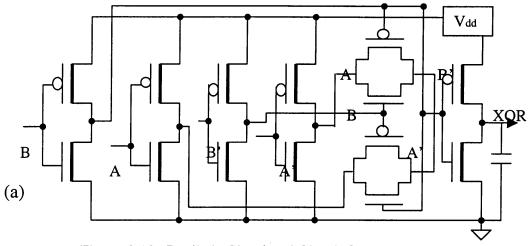

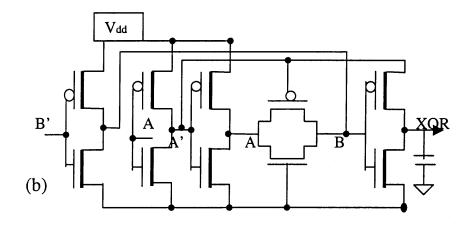

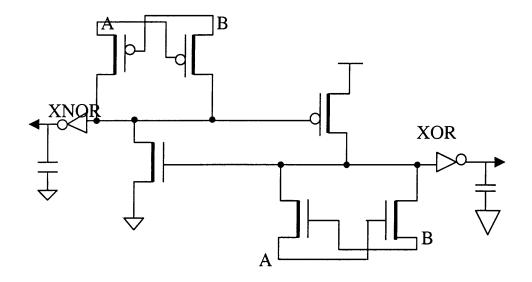

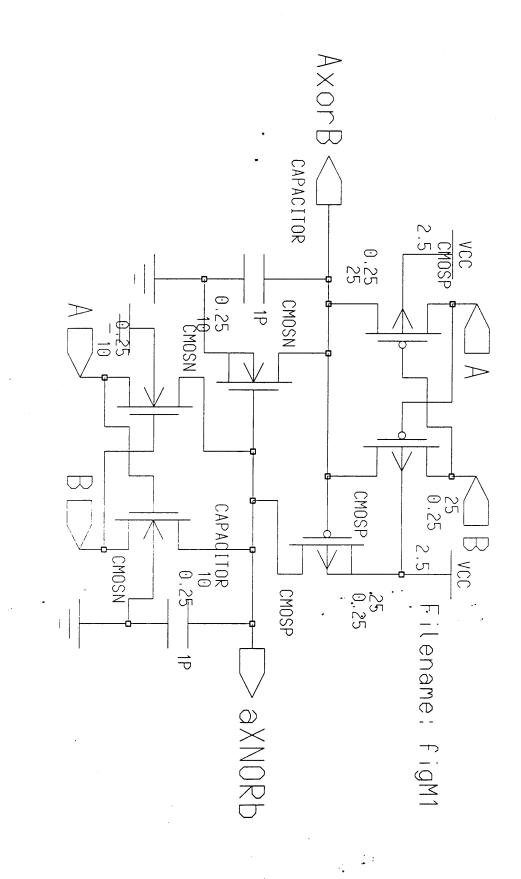

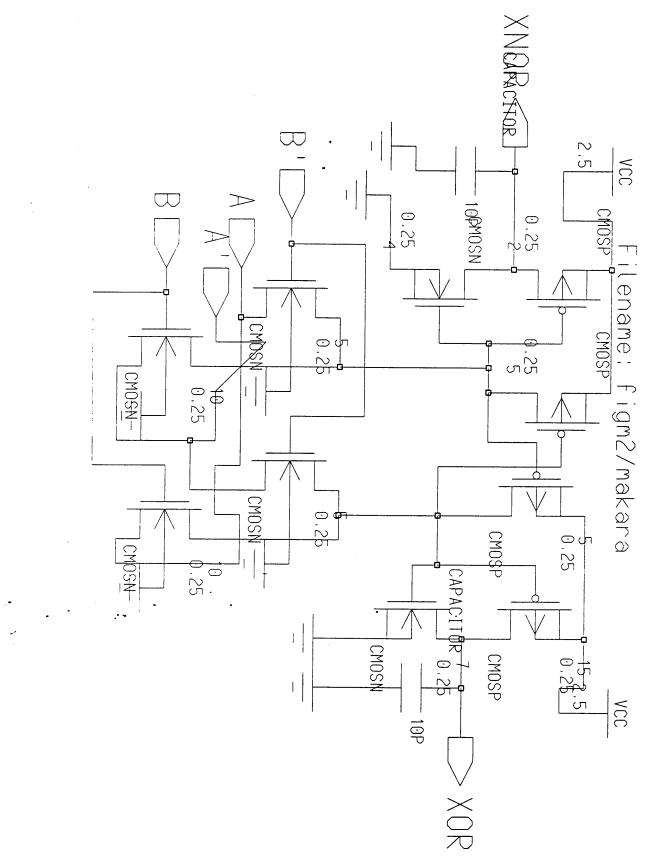

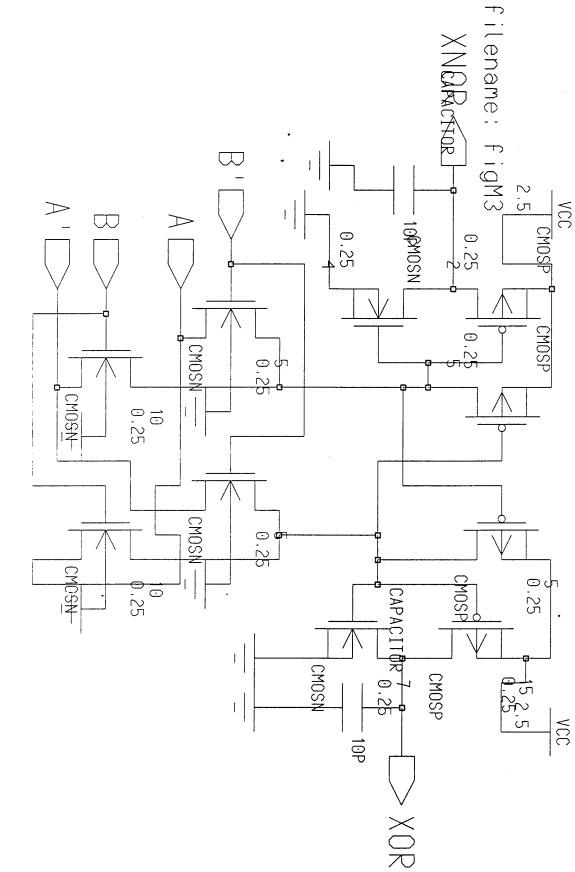

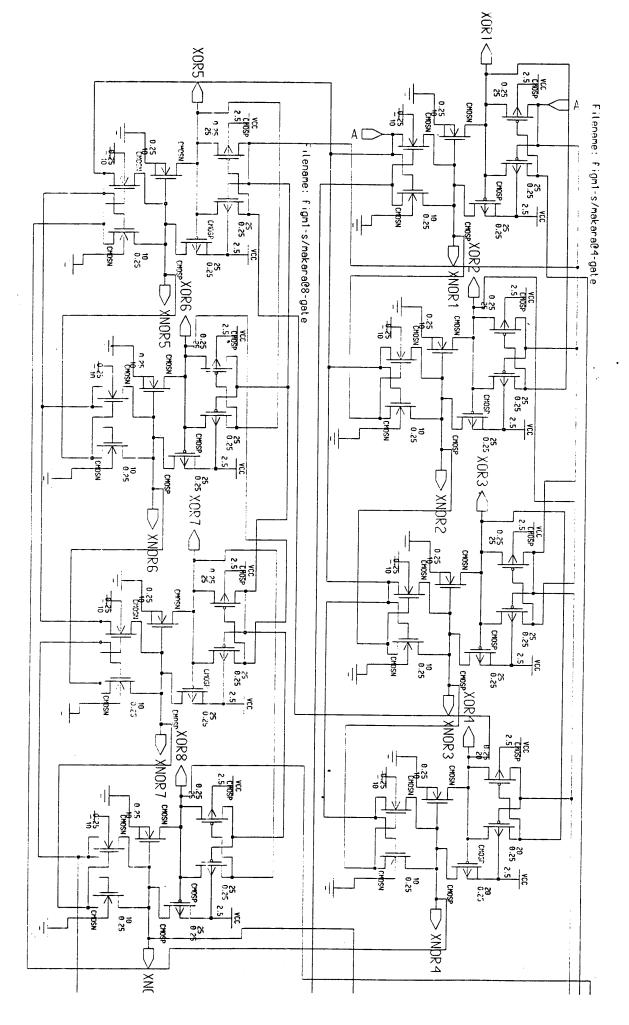

#### 2.6 Combination Circuit Design XOR/XNOR

Combination XOR/XNOR circuit designs are shown in Figures 2.M1, 2.M2, 2.M3, 2.M4, and 2.M5. The XOR/XNOR gates are given the structure names off full restored combination circuit design XOR/XNOR (Figure 2.M1), complementary pass gate logic (Figure 2.M2), complementary pass gate logic cross bar (Figure 2.M3), swing restored gate logic (Figure 2.M4), and full restored Combination circuit design XOR/XNOR with driving output (Figure 2.M5). A comparison of the advantages and disadvantages for the circuits in Figures 2.M1, 2.M2, 2.M3, 2.M4, and 2.M5 are shown on Table 2.1.

|             | Table 2.1 Circuit Comparison             |                   |

|-------------|------------------------------------------|-------------------|

|             | Advantage                                | Disadvantage      |

| Figure 2.M1 | static gate for low power circuit design | slow circuit      |

| Figure 2.M2 | high speed and fewer stages of delay     | body effect       |

| Figure 2.M3 | improved cross bar current               | high power        |

| Figure 2.M4 | low standby current/less delay           | less output drive |

| Figure 2.M5 | more driving output                      | hard scaling      |

Figure 2.8/Figure 2.M1 Full Restored Combination Circuit Design XOR/XNOR (HSPICE and Mentor).

Figure 2.M2 Complementary Pass Gate Logic.

Figure 2.M3 Complementary Pass Gate Logic Cross Bar.

Figure 2.M4 Swing Restored Pass Gate Logic.

Figure 2.M5 Full Restored Combination Circuit Design XOR/XNOR Driving Output.

#### 2.7 Basic Physical Layout Design of XOR/XNOR Gates

We will examine the physical layout of CMOS gates in a general sense to study the impact of the physical structure on the behavior of the circuit. These XOR/XNOR gates begin with an outline of **inverter** layout forms. To simplify layouts, "unit" sized transistors will generally be shown. In actual layouts, the correct dimension transistors would be arrived at via detailed circuit design. ptransistors will often be shown to be double in "unit" size. A symbolic layout style is used to show most layouts. Wires and transistors are arranged on a grid and actual layouts would space the grid proportionately to design results.

By examining the circuit diagram for the two inverters (Figure 2.3(a)), we should be able to lecture a physical layout by substituting layout symbols for the schematic symbols [5]. Any non-planar situation is dealt with by simply crossing two lines, i.e., the connection between the drain of the n-transistor and the drain of the p-transistor. However, in a physical layout, we have to concern ourselves with the interaction of physical different interconnection layers. We know from our consideration of the fabrication process that the source and drain of the n-transistor are n-diffusion regions and the p-transistor uses p-diffusion regions for these connections. Additionally in a bulk CMOS process we cannot make a direct connection from n-diffusion to p-diffusion. Thus we have to implement the simple inter-drain connection in the structural domain with at least one wire and two contacts in the physical domain. Assuming that the process does not have local interconnect or buried contacts, this connection has to be in metal.

Alternatively, if a metal line is to be passed from left to right at the top or bottom of the cell, the power and ground connections to the transistors may be made in the appropriate diffusion layer (Figure 2.3(a)-layout). This in effect makes the inverter transparent to horizontal metal connections that may have to be routed through the cell. From considerations that affect performance, the previous deviations from the original layout have little effect. In the case of a vertical poly-silicon drain connection, an extra connection resistance is incurred. This would be approximately (2R-contact) + (R-poly) where R-contact is the resistance of a metal poly-silicon contact and R-poly is the resistance of the polysilicon runner. Additionally, a slight extra capacitance may be incurred. Usually the result of both of these effects would be inconsequential. For the power and ground diffusion connections, the penalty is a series-connection resistance and increased capacitance. The layout designs developed are listed in Appendix D: Inverter-base XOR structure (Figure 2.3(a)), Inverter-base XNOR structure (Figure 2.3(b)), Inverter-base XNOR structure with driving output (Figure 2.3(a)), and Inverter-base XOR structure driving output (Figure 2.4(b)).

# Pass-Transistor Based Multiplexer

Figure 2.13, Layout Design of Figure 2.2

#### 3.0 Results of Simulation

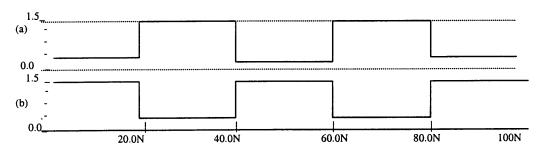

The process technology used is "CMOS TSMC"  $0.35\mu$ m fabrication technology with parameters in CMOSN and CMOSP transistors listed in Appendix B in Table 1. The input signals depicted as the input signals A and B (Figure 3.1) cover four types of combinations; i.e., AB=00, AB=01, AB=10, and AB=11. The output simulation waveforms of the design results are shown in Figure 3.2 and Figure 3.3 where the worst case occurs on the both input signals AB=00. The output signal level in the XOR structure cannot sink to "LOW." In such a condition the poor signal level can still drive the next inverter stage correctly, as in the waveform in Figure 3.2 where the worst case happens on the both input signals AB = 11. The output signal level cannot pull-up to "HIGH", but is still able to make the next inverter stage work correctly.

The results can improve if the threshold value  $|V_{th}|$  decreases. The lower  $|V_{th}|$  is, the smaller the gap between the defect case and the normal case. In the Figure 3.2 and Figure 3.3,  $V_{nth} = 0.49$  volt and  $V_{pth} = -0.66$  volt as shown in Appendix B on Table 1. Figure 3.4 shows the simulation result of the proposed XOR structure with the same parameters as in Appendix B on Table 1 except decreasing the value of  $V_{nth} = 0.25$  volt and  $V_{pth} = -0.36$  volt. From the waveform shown in Figure 3.2 and Figure 3.4, it can be concluded that the smaller  $|V_{th}|$  used, the better the performance achieved, such as increasing the signal level and decreasing the delay time.

Figure 3.4 (a) The output of 4 transistors XOR and (b) the 6 transistors XNOR.

21

#### 3.1 MOSFET Scaling

In MOSFET Scaling the threshold voltage should be decreased by the scaling factor "k" in proportion to the power supply voltage [9]. When the TSMC 0.35 $\mu$ m fabrication technology scales down the threshold voltage (Vth), it also needs to scale down physical dimensions as well. Table 3.2 lists the output simulation file of the transistor parameter model for CMOSN and CMOSP relating to the threshold voltage, sub threshold voltage, and mobility. Table 3.1 lists the generalized MOSFET Scaling theory. The circuit delay scales down by a factor between "k" and "f•k", depending on degree of velocity saturation. The most serious issue with generalized scaling is the increase of the power density by a factor of "f<sup>2</sup>" to "f<sup>3</sup>". The power density increase puts a great burden on VLSI packaging technology to dissipate the extra heat generated on the chip. The power delay product is also a factor of "f<sup>2</sup>" higher than for constant field scaling.

| Ta | ble | 3. | 1 |

|----|-----|----|---|

|    |     |    |   |

## Generalized MOSFET Scaling Theory

| MOSFET D                               | evice and Circuit Param          | neters                         | Multiplication                         |

|----------------------------------------|----------------------------------|--------------------------------|----------------------------------------|

|                                        |                                  | Factor                         |                                        |

| ······································ |                                  |                                | (k>1)                                  |

| Scaling assumptions:                   | Device dimensions                |                                |                                        |

|                                        | (T <sub>ox</sub> , L, W          | , x <sub>j</sub> )             | 1/k                                    |

| Doping concentration                   | $(N_a, N_d)$                     |                                | f•k                                    |

| N **                                   | Vol                              | tage(V)                        | f/k                                    |

| Derived scaling:                       | Electric fiel                    | d (E <sub>-field</sub> )       | f                                      |

| Behavior of device:                    | Depletion layer wi               | idth (W <sub>d</sub> )         | 1/k                                    |

| Parameters:                            | Capacitance (C                   | $C = \epsilon A/t$             | 1/k                                    |

| In                                     | version layer charge den         | isity (Q <sub>i</sub> )        | f                                      |

|                                        |                                  | Long                           | Velocity                               |

|                                        |                                  | channel                        | Saturation                             |

|                                        | Carrier velocity                 | f                              | 1                                      |

|                                        | Current, drift (I)               | f²/k                           | f/k                                    |

| Derived scaling:                       | Circuit delay time               |                                |                                        |

|                                        | $(t_{au} \sim CV/I)$             | 1/f•k                          | 1/k                                    |

| Behavior of circuit:                   | Power dissipation                |                                |                                        |

|                                        | per circuit (p~VI)               | $f^{3}/k^{2}$                  | $f^2/k^2$                              |

| Parameters:                            | Power delay product              |                                |                                        |

|                                        | per circuit (P•t <sub>au</sub> ) | f <sup>2</sup> /k <sup>3</sup> |                                        |

| С                                      | Circuit density ( f•L/A )        | k <sup>2</sup>                 | ······································ |

| I                                      | Power density (P/A)              | f <sup>3</sup>                 | $f^2$                                  |

.

#### Table 3.2

# Output simulation file of the transistor parameter model for CMOSN and CMOSP, TSMC 0.25um fabrication technology

\*\*\* Threshold voltage related model parameters of CMOSP \*\*\*

| VTH0 = -6.01E-01 V  | DELVTO = 0 V                       | K1=5.85E-01 V^1/2 |

|---------------------|------------------------------------|-------------------|

| K2 = 1.48E-02       | NCH = $4.16E + 17 \text{ At/cm}^3$ | K3=0              |

| K3B = 7.78E+0 1/V   | DVTO = 2.35E+0                     | DVT1=7.16E-01     |

| DVT2= -1.13E-01 1/V | DVTOW = 0                          | DVT1W=0 1/m       |

| DVT2W=01/V          | DSUB = 1.37E + 0                   | ETA0 = 1          |

| ETAB= -2.22E-01 1/V |                                    |                   |

\*\*\*\*\*\*

\*\*\*Sub threshold voltage related model parameters of CMOSP\*\*\*

| NFACTOR = 1.15    | $CDSC = 2.4E-04 F/m^{2}$ | CDSCB =0               |

|-------------------|--------------------------|------------------------|

| CDSCD = 0         | VOFF = -1.19E-01 V       | CIT = 0                |

| PDIBLC1 = 1       | PDIBLC2= 1.00E-02        | PDIBLCB = 5.64E-21/V   |

| DROUT = 9.31E-1   | VSAT = 1.36E+05 m/s      | PSCBE1= 3.21E8V/m      |

| PSCBE2= 8.7E-8m/V | PRWB=-2E-1 V^-1/2        | $PRWG = 1.15E-1 \ 1/V$ |

| RDSW = 2.86E+2    | AGS = 3.01E-01 1/V       |                        |

\*\*\*\*\*\*

\*\*\* Threshold voltage related model parameters of CMOSN \*\*\*

| VTH0 = 4.1E-01 V    | DELVTO = 0 V         | $ $ K1 = 5E-1V^1/2 |

|---------------------|----------------------|--------------------|

| K2 = 1.46E-02       | NCH=2.35E+17 At/cm^3 | K3 = 1.00E-03      |

| K3B = 7.78 1/V      | DVTO = 0             | DVT1=1.68E-03      |

| DVT2= 5.00E-01 1/V  | DVTOW = 0            | DVT1W = 0.1/m      |

| DVT2W=0 1/V         | DSUB = 1.47E+02      | ETA0 = 1.09E-03    |

| ETAB = 5.50E-05 1/V |                      |                    |

\*\*\*Sub threshold voltage related model parameters of CMOSN\*\*\*

| NFACTOR = $1.09$ | $CDSC = 2.4E-04 F/m^{2}$ | CDSCB =0 |  |

|------------------|--------------------------|----------|--|

| CDSCD = 0        | VOFF = -1.05E-01 V       | CIT = 0  |  |

\*\*\*\*\*

\*\*\*Mobility related Model parameters CMOSN\*\*\*

| UA =1.04E02 | UB=1.27E10 | UC=2.39E18(m/V)^2 | 11 m/V^2 |

|-------------|------------|-------------------|----------|

| U0 =3.92E   |            |                   |          |

#### 4.0 **Results of XOR Gates with HSPICE**

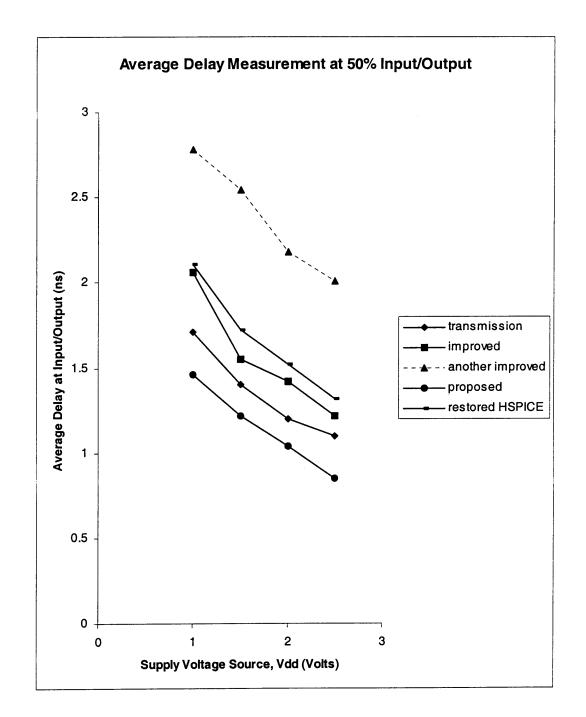

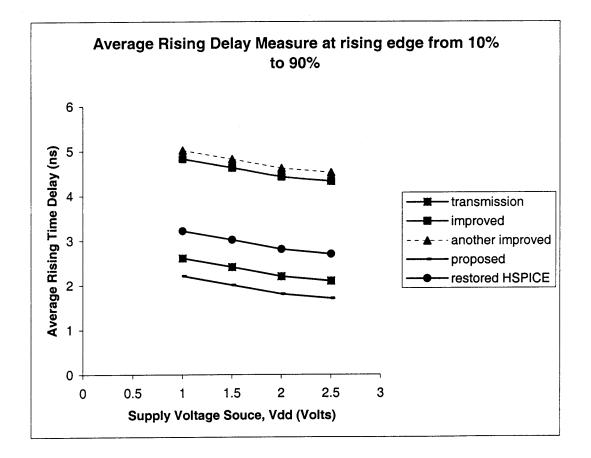

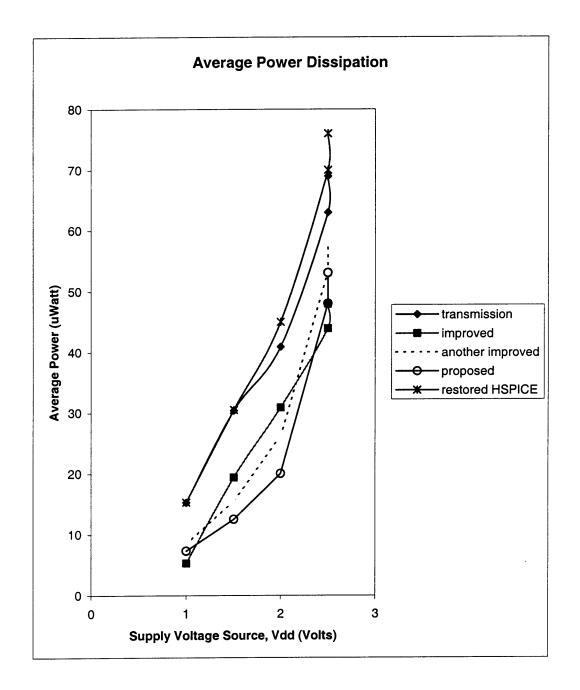

Results of average delay, rising delay time, and falling delay time of the XOR gates are illustrated in Tables 4.1 and 4.2, respectively. When either signal A or signal B changes state due to propagation delay, the **ON** or **OFF** of the transmission gate element would not be fully synchronized to the first inverter in the XOR structure of the improved version XOR structure (Figure 4a). It results in both the NMOS transistor and the PMOS transistor turning on instantly. Comparisons of the XOR gates are summarized in Table 4.3. The competing factors are the number of transistors, the driving capability, non-complementary signal inputs, and the output signal levels. From Table 4.3, it is obvious that these designs are the most competitive ones among all methods. The measured average power dissipation of each XOR gates is shown in Table 4.4. For the data shown in Tables 4.1 to 4.4 and Figures 4.1 to 4.4, all the XOR gates are listed in the Figures 2.2, 2.4(a), 2.4(b), 2.6, and 2.7. These XOR gates have been fully simulated at the HSPICE Level 49 with TSMC 0.35µm fabrication technology.

| Delay Time Analysis of Each XOR Structure at 2.5 Volt |                                        |                                                                                                                                                |                                                                                                                                                                           |                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                |  |

|-------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 00->10                                                | 10->11                                 | 11->01                                                                                                                                         | 01->00                                                                                                                                                                    | Average                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                |  |

| 1.14                                                  | 0.95                                   | 1.21                                                                                                                                           | 1.09                                                                                                                                                                      | 1.10                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                |  |

| 2.26                                                  | 0.51                                   | 1.12                                                                                                                                           | 1.00                                                                                                                                                                      | 1.22                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                |  |

| 2.88                                                  | 3.0                                    | 1.07                                                                                                                                           | 1.09                                                                                                                                                                      | 2.01                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                |  |

| 1.15                                                  | 0.66                                   | 1.08                                                                                                                                           | 0.38                                                                                                                                                                      | 0.85                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                |  |

| 1.45                                                  | 1.31                                   | 1.35                                                                                                                                           | 1.17                                                                                                                                                                      | 1.32                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                |  |

|                                                       | 00->10<br>1.14<br>2.26<br>2.88<br>1.15 | $\begin{array}{c cccc} 00 -> 10 & 10 -> 11 \\ \hline 1.14 & 0.95 \\ \hline 2.26 & 0.51 \\ \hline 2.88 & 3.0 \\ \hline 1.15 & 0.66 \end{array}$ | $\begin{array}{c cccccc} 00 -> 10 & 10 -> 11 & 11 -> 01 \\ \hline 1.14 & 0.95 & 1.21 \\ 2.26 & 0.51 & 1.12 \\ 2.88 & 3.0 & 1.07 \\ \hline 1.15 & 0.66 & 1.08 \end{array}$ | 00->10         10->11         11->01         01->00           1.14         0.95         1.21         1.09           2.26         0.51         1.12         1.00           2.88         3.0         1.07         1.09           1.15         0.66         1.08         0.38 | 00->10         10->11         11->01         01->00         Average           1.14         0.95         1.21         1.09         1.10           2.26         0.51         1.12         1.00         1.22           2.88         3.0         1.07         1.09         2.01           1.15         0.66         1.08         0.38         0.85 |  |

Table 4.1 @2.5volt Fime Analysis of Each XOR Structure at 2.5V

Remark: 00->10: input signals AB change from 00 to 10, delay time = time difference between input transistor 50% level and the 50% output level. This is the time taken for a logic transition to pass from input to output.

| Table 4.1 @2.0volt |

|--------------------|

|--------------------|

| Unit: ns    | 00->10 | 10->11 | 11->01 | 01->00 | Average |

|-------------|--------|--------|--------|--------|---------|

| Figure 2.2  | 0.74   | 1.05   | 1.31   | 1.19   | 1.20    |

| Figure 2.4a | 2.46   | 0.71   | 1.32   | 1.20   | 1.42    |

| Figure 2.4b | 2.98   | 3.20   | 1.17   | 1.39   | 2.18    |

| Figure 2.6  | 1.45   | 0.86   | 1.28   | 0.58   | 1.04    |

| Figure 2.8  | 1.65   | 1.51   | 1.55   | 1.37   | 1.52    |

|             |        |        |        |        |         |

Delay Time Analysis of Each XOR Structure at 2.0Volt

Table 4.1 @1.5volt

Delay Time Analysis of Each XOR Structure at 1.5Volt

| Unit: ns    | 00->10 | 10->11 | 11->01 | 01->00 | Average |

|-------------|--------|--------|--------|--------|---------|

| Figure 2.2  | 1.44   | 1.25   | 1.51   | 1.39   | 1.40    |

| Figure 2.4a | 2.56   | 0.81   | 1.42   | 1.40   | 1.55    |

| Figure 2.4b | 3.08   | 3.32   | 1.97   | 1.79   | 2.54    |

| Figure 2.6  | 1.55   | 1.06   | 1.48   | 0.78   | 1.22    |

| Figure 2.8  | 1.75   | 1.61   | 1.65   | 1.47   | 1.72    |

Table 4.1 @1.0volt

| Delay Time Analysis of Each XOR Structure at 1 | t 1.0Volt |

|------------------------------------------------|-----------|

|------------------------------------------------|-----------|

|             | /      |        |        |        |         |

|-------------|--------|--------|--------|--------|---------|

| Unit: ns    | 00->10 | 10->11 | 11->01 | 01->00 | Average |

| Figure 2.2  | 1.74   | 1.55   | 1.81   | 1.69   | 1.71    |

| Figure 2.4a | 2.86   | 1.11   | 1.72   | 1.60   | 2.06    |

| Figure 2.4b | 3.28   | 3.70   | 2.17   | 1.99   | 2.78    |

| Figure 2.6  | 1.85   | 1.36   | 1.78   | 0.88   | 1.46    |

| Figure 2.8  | 2.15   | 2.01   | 2.05   | 1.87   | 2.11    |

|             |        |        |        |        |         |

Figure 4.1 Average Delay

| Unit: ns    | 00->10     | 10->11     | 11->01   | 01->00       | Average    | Average   |

|-------------|------------|------------|----------|--------------|------------|-----------|

|             | Rising     | Falling    | Rising   | Falling      | Rising     | Falling   |

| Figure 2.2  | 2.1        | 1.46       | 2.09     | 1.5          | 2.1        | 1.48      |

| Figure 2.4a | 4.79       | 3.11       | 3.86     | 2.65         | 4.33       | 2.88      |

| Figure 2.4b | 6.94       | 2.96       | 2.1      | 1.49         | 4.52       | 2.23      |

| Figure 2.6  | 2.1        | 0.98       | 2.22     | 0.26         | 2.11       | 0.62      |

| Figure 2.8  | 2.79       | 4.65       | 2.61     | 4.51         | 2.70       | 4.58      |

| Domark: Dia | ing time - | time for a | wayeform | to rice from | m 10% to 0 | 0% of its |

Table 4.2 @2.5volt Rising/Falling Time Analysis of Each XOR Structure at 2.5volt

Remark: Rising time = time for a waveform to rise from 10% to 90% of its Steady-state value.

Falling time: time for a waveform to fall from 90% to 10% of its Steady-state value.

Table 4.2 @2.0volt

| <b>Rising/Falling Time</b> | Analysis of Each X | OR Structure at 2.0volt |

|----------------------------|--------------------|-------------------------|

|                            |                    |                         |

| Unit: ns    | 00->10<br>Dising | 10->11<br>Falling | 11->01<br>Rising | 01->00<br>Falling | Average<br>Rising | Average<br>Falling |

|-------------|------------------|-------------------|------------------|-------------------|-------------------|--------------------|

|             | Rising           | U                 |                  | 0                 | <b>_</b>          |                    |

| Figure 2.2  | 2.20             | 1.66              | 2.19             | 1.70              | 2.2               | 1.67               |

| Figure 2.4a | 4.89             | 3.31              | 3.96             | 2.85              | 4.43              | 3.08               |

| Figure 2.4b | 7.04             | 3.16              | 2.21             | 1.69              | 4.62              | 2.44               |

| Figure 2.6  | 2.2              | 1.18              | 2.32             | 0.46              | 2.21              | 0.82               |

| Figure 2.8  | 2.89             | 4.85              | 2.70             | 4.71              | 2.81              | 4.78               |

Table 4.2 @1.5volt

| Rising/Falling Time | Analysis of Each | XOR Structure | at 1.5volt |

|---------------------|------------------|---------------|------------|

|                     |                  |               |            |

| Kising/     | Failing 11m | e Allarysis C | n Each AC | K Suuciule |         |         |

|-------------|-------------|---------------|-----------|------------|---------|---------|

| Unit: ns    | 00->10      | 10->11        | 11->01    | 01->00     | Average | Average |

|             | Rising      | Falling       | Rising    | Falling    | Rising  | Falling |

| Figure 2.2  | 2.40        | 1.76          | 2.39      | 1.80       | 2.41    | 1.77    |

| Figure 2.4a | 5.09        | 3.41          | 4.16      | 2.95       | 4.63    | 3.18    |

| Figure 2.4b | 7.24        | 3.26          | 2.41      | 1.79       | 4.82    | 2.54    |

| Figure 2.6  | 2.41        | 1.28          | 2.52      | 0.56       | 2.41    | 0.92    |

| Figure 2.8  | 3.10        | 4.95          | 2.90      | 4.81       | 3.02    | 4.88    |

| Unit: ns    | 00->10 | 10->11  | 11->01 | 01->00  | Average | Average |

|-------------|--------|---------|--------|---------|---------|---------|

|             | Rising | Falling | Rising | Falling | Rising  | Falling |

| Figure 2.2  | 2.60   | 1.96    | 2.59   | 2.00    | 2.61    | 1.97    |

| Figure 2.4a | 5.29   | 3.61    | 4.36   | 3.15    | 4.83    | 3.38    |

| Figure 2.4b | 7.44   | 3.46    | 2.61   | 1.99    | 5.02    | 2.74    |

| Figure 2.6  | 2.61   | 1.48    | 2.72   | 0.76    | 2.61    | 1.12    |

| Figure 2.8  | 3.30   | 5.15    | 3.10   | 5.01    | 3.22    | 5.08    |

Table 4.2 @1.0volt Rising/Falling Time Analysis of Each XOR Structure at 1.0volt

Figure 4.2 Average Rising Delay

Figure 4.3 Average Falling Delay

|             | 00 | 01 | 10 | 11 | #Tr | Driving Output | Complement Output |

|-------------|----|----|----|----|-----|----------------|-------------------|

| Figure 2.1  | 0  | 0  | 0  | 0  | 4   | No             | Yes               |

| Figure 2.2  | 0  | 0  | 0  | 0  | 6   | better         | Yes               |

| Figure 2.3  | X  | X  | 0  | 0  | 4   | No             | No                |

| Figure 2.4a | 0  | 0  | 0  | 0  | 6   | good           | No                |

| Figure 2.4b | 0  | 0  | Α  | 0  | 6   | worse          | No                |

| Figure 2.5  | 0  | 0  | 0  | Χ  | 4   | No             | No                |

| Figure 2.6  | 0  | 0  | 0  | 0  | 6   | best           | No                |

| Figure 2.8  | 0  | 0  | 0  | 0  | 6   | No             | No                |

Table 4.3Comparison of Each XOR Function

Symbols: AB= 00, 01, 10, 11. #Tr is number of transistors, O is good X is poor signal level. A is nearly good signal level.

| Table 4.4                                                   |  |

|-------------------------------------------------------------|--|

| Average Power Dissipation from 0 through 100ns of XOR Gates |  |

| Unit: uW, P | <u>ower@1v, Pc</u> | wer@1.5v, | <u>Power@2v, P</u> | <u>ower@2.5v</u> , 1 | Power@2.5v/Vth |

|-------------|--------------------|-----------|--------------------|----------------------|----------------|

| Figure 2.2  | 15.21uW            | 30.42uW   | 40.92uW            | 62.98uW              | 68.98uW        |

| Figure 2.4a | 5.20uW             | 19.40uW   | 30.90uW            | 43.91uW              | 47.92uW        |

| Figure 2.4b | 8.41uW             | 15.63uW   | 26.13uW            | 53.13uW              | 58.23uW        |

| Figure 2.6  | 7.31uW             | 12.53uW   | 20.03uW            | 48.03uW              | 53.09uW        |

| Figure 2.8  | 15.32uW            | 30.52uW   | 45.02uW            | 70.02uW              | 76.03uW        |

| Power Dissipation Equation measure from HSPICES:               |

|----------------------------------------------------------------|

| .meas tran avg_curr avg I(Vdd) from = $2.0$ ns to = $100.0$ ns |

| .meas avg_power param = ' -avg_curr*Vdd'                       |

Figure 4.4 Average Power Dissipation (Note: Two marks at  $V_{dd} = 2.5$  volt was shown on the chart, for the bottom mark is simulated at  $V_{dd} = 2.5$  volt and the top mark is simulated with decreased threshold voltage)

#### 4.1 **Results of XOR Gates with Mentor Graphics**

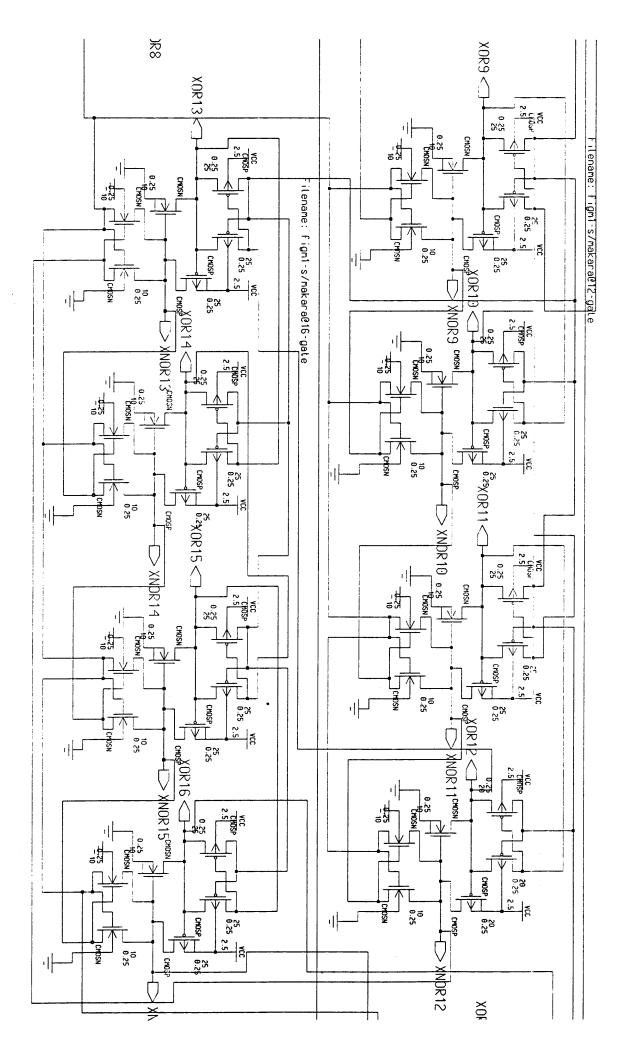

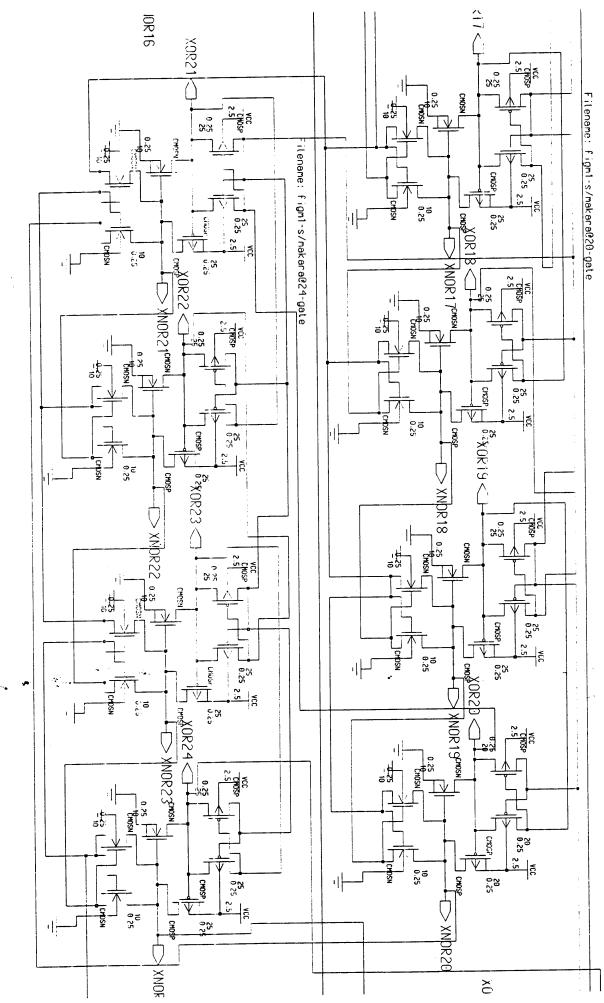

Results of average delay, rising delay time, and falling delay time of XOR gates are listed in Table 4.5 and 4.6. The comparison of each XOR gate is summarized in Table 4.7. The average power dissipation of each XOR gate is summarized in Table 4.8. Charts for data analysis are shown in Table 4.5 to 4.8. For the data shown in Tables 4.5 to 4.8 and Figures 4.5 to 4.8, all the XOR gates are listed in the Figures 2.M1, 2.M2, 2.M3, 2.M4, and 2.M5. These XOR gates have been fully simulated at the Mentor Graphics Level 53 with TSMC 0.25µm fabrication technology.

Table 4.5 @2.5volt with scale Vth

| s of Each X | OR Struct                              | ure at 2.5V                                  | olt with sca                                                                                                                                                                                             | ale Vth                                                                                  |                                                                                                                                                                                                                                                                   |

|-------------|----------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00->10      | 10->11                                 | 11->01                                       | 01->00                                                                                                                                                                                                   | Average                                                                                  |                                                                                                                                                                                                                                                                   |

| 1.80        | 2.01                                   | 1.97                                         | 2.00                                                                                                                                                                                                     | 1.94                                                                                     |                                                                                                                                                                                                                                                                   |

| 3.09        | 3.98                                   | 3.71                                         | 4.01                                                                                                                                                                                                     | 3.69                                                                                     | ]                                                                                                                                                                                                                                                                 |

| 1.21        | 1.41                                   | 1.22                                         | 1.39                                                                                                                                                                                                     | 1.31                                                                                     |                                                                                                                                                                                                                                                                   |

| 0.15        | 0.16                                   | 0.28                                         | 0.08                                                                                                                                                                                                     | 0.22                                                                                     |                                                                                                                                                                                                                                                                   |

| 2.50        | 2.40                                   | 2.50                                         | 2.40                                                                                                                                                                                                     | 2.45                                                                                     |                                                                                                                                                                                                                                                                   |

|             | 00->10<br>1.80<br>3.09<br>1.21<br>0.15 | 00->1010->111.802.013.093.981.211.410.150.16 | 00->10         10->11         11->01           1.80         2.01         1.97           3.09         3.98         3.71           1.21         1.41         1.22           0.15         0.16         0.28 | 00->1010->1111->0101->001.802.011.972.003.093.983.714.011.211.411.221.390.150.160.280.08 | 1.80         2.01         1.97         2.00         1.94           3.09         3.98         3.71         4.01         3.69           1.21         1.41         1.22         1.39         1.31           0.15         0.16         0.28         0.08         0.22 |

Remark: 00->10: Input signals AB change from 00 to 10, delay time = time difference between input transistor 50% level and the 50% output level. This is the time taken for a logic transition to pass from input to output.

| Unit: ns    | 00->10 | 10->11 | 11->01 | 01->00 | Average |

|-------------|--------|--------|--------|--------|---------|

| Figure 2.M1 | 2.20   | 2.21   | 2.27   | 2.43   | 2.03    |

| Figure 2.M2 | 3.29   | 4.18   | 3.91   | 4.21   | 4.04    |

| Figure 2.M3 | 1.41   | 1.61   | 1.42   | 1.59   | 1.51    |

| Figure 2.M4 | 0.35   | 0.26   | 0.38   | 0.28   | 0.31    |

| Figure 2.M5 | 2.80   | 2.70   | 2.80   | 2.70   | 2.75    |

Table 4.5 @2.5volt

| Unit: ns    | 00->10 | 10->11 | 11->01 | 01->00 | Average |

|-------------|--------|--------|--------|--------|---------|

| Figure 2.M1 | 2.50   | 2.41   | 2.57   | 2.73   | 2.33    |

| Figure 2.M2 | 3.49   | 4.38   | 4.11   | 4.41   | 4.24    |

| Figure 2.M3 | 1.61   | 1.81   | 1.62   | 1.79   | 1.71    |

| Figure 2.M4 | 0.65   | 0.56   | 0.68   | 0.58   | 0.60    |

| Figure 2.M5 | 2.90   | 2.80   | 2.90   | 2.80   | 2.85    |

Table 4.5 @2.0volt Delay Time Analysis of Each XOR Structure at 2.0Volt

Table 4.5 @1.5volt

| <br>Unit: ns | 00->10 | 10->11 | 11->01 |      | Average |

|--------------|--------|--------|--------|------|---------|

| Figure 2.M1  | 2.80   | 2.71   | 2.87   | 3.03 | 2.63    |

| Figure 2.M2  | 3.79   | 4.58   | 4.31   | 4.61 | 4.32    |

| Figure 2.M3  | 1.81   | 2.01   | 1.82   | 1.99 | 1.91    |

| Figure 2.M4  | 0.75   | 0.66   | 0.78   | 0.64 | 0.72    |

| Figure 2.M5  | 3.00   | 3.10   | 3.00   | 3.10 | 3.05    |

Analysis of Each XOR Structure at 1 5Volt Dalay Tir

Table 4.5 @1.0volt

| Unit: ns    | 00->10 | 10->11 | 11->01 | 01->00 | Average |

|-------------|--------|--------|--------|--------|---------|

| Figure 2.M1 | 3.10   | 3.01   | 3.17   | 3.33   | 3.15    |

| Figure 2.M2 | 3.99   | 4.88   | 4.61   | 4.81   | 4.57    |

| Figure 2.M3 | 2.11   | 2.31   | 2.12   | 2.19   | 2.20    |

| Figure 2.M4 | 1.05   | 0.96   | 1.08   | 0.94   | 1.02    |

| Figure 2.M5 | 3.20   | 3.30   | 3.20   | 3.30   | 3.25    |

Delay Time Analysis of Each XOR Structure at 1.0Volt

Figure 4.5 Average Delay XOR Gates

(Note: Two marks at  $V_{dd} = 2.5$  volt was shown on the chart, for the bottom mark is simulated at  $V_{dd} = 2.5$  volt and the top mark is simulated with decreased threshold voltage)

| Table 4.6 @2.5volt with scale Vth                                            |

|------------------------------------------------------------------------------|

| Rising/Falling Time Analysis of Each XOR Structure at 2.5volt with scale Vth |

| Unit: ns        | 00->10<br>Rising | 10->11<br>Falling | 11->01<br>Rising | 01->00<br>Falling | Average<br>Rising | Average<br>Falling |

|-----------------|------------------|-------------------|------------------|-------------------|-------------------|--------------------|

| Figure 2.M1/Vth | 2.30             | 2.73              | 2.31             | 2.74              | 2.31              | 2.74               |

| Figure 2.M2/Vth | 3.90             | 4.38              | 3.92             | 4.40              | 3.91              | 4.39               |

| Figure 2.M3/Vth | 1.40             | 1.63              | 1.42             | 1.64              | 1.41              | 1.63               |

| Figure 2.M4/Vth | 0.28             | 0.50              | 0.30             | 0.52              | 0.22              | 0.51               |

| Figure 2.M5/Vth | 2.80             | 2.70              | 2.80             | 2.70              | 2.80              | 2.70               |

Remark: Rising time = time for a waveform to rise from 10% to 90% of its Steady-state value.

Falling time: time for a waveform to fall from 90% to 10% of its Steady-state value.

Table 4.6 @2.5volt

| Rising/Falling Time Analysis of Each XOR Structure at 2.5volt |        |         |        |         |         |         |  |  |  |

|---------------------------------------------------------------|--------|---------|--------|---------|---------|---------|--|--|--|

| Unit: ns                                                      | 00->10 | 10->11  | 11->01 | 01->00  | Average | Average |  |  |  |

|                                                               | Rising | Falling | Rising | Falling | Rising  | Falling |  |  |  |

| Figure 2.M1                                                   | 2.50   | 2.93    | 2.51   | 2.94    | 2.51    | 2.94    |  |  |  |

| Figure 2.M2                                                   | 4.10   | 4.58    | 4.12   | 4.60    | 4.11    | 4.59    |  |  |  |

| Figure 2.M3                                                   | 1.60   | 1.83    | 1.62   | 1.84    | 1.61    | 1.83    |  |  |  |

| Figure 2.M4                                                   | 0.58   | 0.80    | 0.60   | 0.82    | 0.52    | 0.81    |  |  |  |

| Figure 2.M5                                                   | 4.50   | 3.51    | 4.50   | 3.51    | 4.50    | 3.51    |  |  |  |

Rising/Falling Time Analysis of Each XOR Structure at 2.5volt

Table 4.6 @2.0volt

Rising/Falling Time Analysis of Each XOR Structure at 2.0volt

| Unit: ns    | 00->10<br>Rising | 10->11<br>Falling | 11->01<br>Rising | 01->00<br>Falling | Average<br>Rising | Average<br>Falling |

|-------------|------------------|-------------------|------------------|-------------------|-------------------|--------------------|

| Figure 2.M1 | 2.75             | 3.18              | 2.76             | 3.19              | 2.76              | 3.18               |

| Figure 2.M2 | 4.40             | 4.88              | 4.42             | 4.90              | 4.31              | 4.89               |

| Figure 2.M3 | 1.80             | 2.03              | 1.82             | 2.04              | 1.81              | 2.03               |

| Figure 2.M4 | 0.78             | 2.00              | 0.80             | 1.02              | 0.72              | 1.01               |

| Figure 2.M5 | 4.70             | 3.71              | 4.60             | 3.71              | 4.65              | 3.71               |

| Table 4.6 @1.5volt                                            |

|---------------------------------------------------------------|

| Rising/Falling Time Analysis of Each XOR Structure at 1 5volt |

| Unit: ns    | 00->10 | 10->11   | 11->01 | 01->00  | Average | Average |

|-------------|--------|----------|--------|---------|---------|---------|

|             | Rising | Falling_ | Rising | Falling | Rising  | Falling |

| Figure 2.M1 | 2.96   | 3.48     | 2.97   | 3.49    | 2.97    | 3.48    |

| Figure 2.M2 | 4.60   | 5.08     | 4.62   | 5.10    | 4.61    | 5.09    |

| Figure 2.M3 | 2.01   | 2.33     | 2.02   | 2.34    | 2.02    | 2.33    |

| Figure 2.M4 | 0.98   | 2.30     | 1.00   | 1.32    | 0.92    | 1.81    |

| Figure 2.M5 | 4.95   | 3.94     | 5.00   | 3.96    | 4.97    | 3.95    |

Table 4.6 @1.0volt

Rising/Falling Time Analysis of Each XOR Structure at 1.0volt

| Unit: ns    | 00->10<br>Rising | 10->11<br>Falling | 11->01<br>Rising | 01->00<br>Falling | Average<br>Rising | Average<br>Falling |

|-------------|------------------|-------------------|------------------|-------------------|-------------------|--------------------|

| Figure 2.M1 | 3.16             | 3.78              | 3.37             | 3.89              | 3.27              | 3.84               |

| Figure 2.M2 | 5.10             | 5.58              | 5.12             | 5.50              | 5.11              | 5.59               |

| Figure 2.M3 | 2.61             | 3.03              | 2.62             | 3.04              | 2.62              | 3.03               |

| Figure 2.M4 | 1.68             | 2.90              | 1.60             | 1.92              | 1.52              | 2.41               |

| Figure 2.M5 | 5.20             | 4.10              | 5.30             | 4.20              | 5.25              | 4.15               |

Figure 4.6 Average Rising Delay XOR Gates

Figure 4.7 Average Falling Delay XOR

|             | 00 | 01 | 10 | 11 | #Tr | Driving Output | Complement Output |

|-------------|----|----|----|----|-----|----------------|-------------------|

| Figure 2.M1 | 0  | 0  | 0  | 0  | 6   | No             | No                |

| Figure 2.M2 | 0  | 0  | 0  | 0  | 8   | best           | No                |

| Figure 2.M3 | 0  | A  | 0  | 0  | 10  | best           | No                |

| Figure 2.M4 | 0  | A  | 0  | 0  | 8   | best           | No                |

| Figure 2.M5 | 0  | 0  | 0  | 0  | 10  | best           | Yes               |

# Comparison of Each XOR Function