# AC/DC CHARACTERIZATION OF NMOS AND PMOS DEGRADATION UNDER AC/DC STRESS

Mary Dawes B.S.E.E., University of Portland, 1984 B.S. Mathematics, Portland State University, 1982 B.S. Nursing, Oregon Health Sciences University, 1970

A thesis submitted to the faculty

of the Oregon Graduate Center

in partial fulfillment of the

requirements for the degree

Master of Science

in

Electrical Engineering

May 1989

The thesis "AC/DC Characterization of NMOS and PMOS Degradation Under AC/DC Stress," by Mary Dawes has been examined and approved by the following Examination Committee:

> D. M. Kim, Adviso Professor

John S. Blakemore Professor

Mohsen Alavi, Ph.D. Intel Corporation

Ronald Burghard, Ph.D. Intel Corporation

#### ACKNOWLEDGEMENTS

I wish to express my gratitude to my advisor Professor Dae Mann Kim for his encouragement, direction and communication of his love of physics and learning.

I am very grateful to Intel Corporation for allowing me the use of their facilities and the material which made this thesis possible. I am particularly indebted to Mohsen Alavi for directing my work at Intel and to the people in the reliability physics lab (Joan Davis, Tim LaBeck, Yung Huei Lee, Stan Maston, Stan Miller and John Thomas). Without their support and assistance much of this work could not have been done.

I also wish to thank the members of the thesis committee, Dr. John Blakemore, Dr. Ron Burghard, and Dr. Mohsen Alavi for their helpful suggestions and comments.

Finally, I thank God for His faithfulness and goodness in giving me the opportunity to learn and attend OGC.

To my Aunt, who has encouraged and demonstrated the pursuit of excellence.

# Table of Contents

| Chapter 1: Introduction                  | 1   |

|------------------------------------------|-----|

| Chapter 2: Background Literature         | 4   |

| Chapter 3: Description of Experiment     | 26  |

| Chapter 4: Results                       | 36  |

| Chapter 5: Interpretation and Discussion | 84  |

| Chapter 6: Conclusions                   | 108 |

| Appendix                                 | 110 |

| Vita                                     | 115 |

# Table of Figures

| Figure | 1  |   | 28  |

|--------|----|---|-----|

| Figure | 2  |   | 29  |

| Figure | 3  |   | 31  |

| Figure | 4  |   | 34  |

| Figure | 5  |   | ,40 |

| Figure | 6  |   | ,43 |

| Figure | 7  |   | 45  |

| Figure | 8  |   | 47  |

| Figure | 9  |   | 48  |

| Figure | 10 | ) | 50  |

| Figure | 11 |   | 51  |

| Figure | 12 | 2 | 52  |

| Figure | 13 | 3 | 53  |

| Figure | 14 | l | 55  |

| Figure | 15 | 5 | 56  |

| Figure | 16 | <br>57,58 |

|--------|----|-----------|

| Figure | 17 | <br>59,60 |

| Figure | 18 | <br>62    |

| Figure | 19 | <br>63    |

| Figure | 20 | <br>65    |

| Figure | 21 | <br>67    |

| Figure | 22 | <br>68    |

| Figure | 23 | <br>69    |

| Figure | 24 | <br>70    |

| Figure | 25 | <br>72    |

| Figure | 26 | <br>73    |

| Figure | 27 | <br>75    |

| Figure | 28 | <br>76    |

| Figure | 29 | <br>77    |

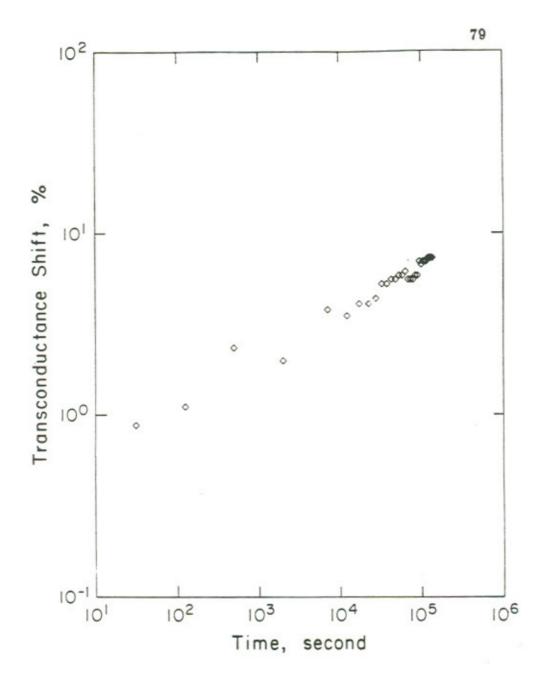

| Figure | 30 | <br>79    |

| Figure | 31 | <br>85    |

| Figure | 32 | <br>90    |

| Figure | 22 | 02        |

| Figure | 34 | <br>94 |

|--------|----|--------|

| Figure | 35 | <br>96 |

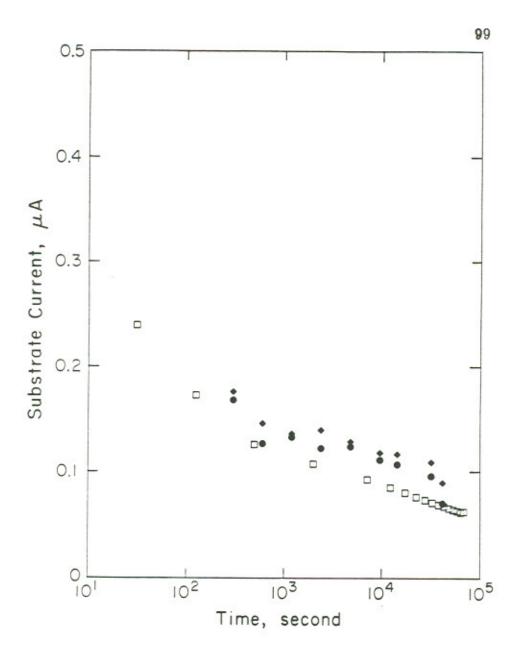

| Figure | 36 | 99     |

#### ABSTRACT

# AC/DC Characterization of NMOS and PMOS Degradation Under AC/DC Stress

Mary Dawes, M.S.

Oregon Graduate Center, 1989

Supervising Professor: D. M. Kim

Hot carrier induced NMOS and PMOS degradation is experimentally examined. AC and DC measurement of n- and p-channel device parameter shifts are compared following DC stress. In both types of devices, there was no appreciable difference in AC and DC measurements of device degradation. The data indicate that hot carrier induced interface states are shallow and fast with lifetimes less than 20 ns. The effects of AC and DC stress on NMOS and PMOS are studied in terms of DC characterization. In PMOS, AC drain stress is generally quasi-static. On the other hand, AC gate stress produced enhanced device degradation corresponding to the worst case DC stress. In NMOS, the effect of AC stress is apparent and drastic. Here, the threshold value of the oxide electric field, Eot is operative. Below Eot AC drain stress is again found to be quasti-static. However, AC gate stress is shown to give rise to enhanced parameter shift compared to the corresponding DC stress. This dynamic stress could lead to device failure for an oxide electric field greater than Eot. Above Eot drain pulsing also results in pronounced device degradation again leading to device failure. The observed AC stress effects are consistent with the two carrier model.

# CHAPTER 1

# INTRODUCTION

As silicon fabrication technology has advanced, the feature size of MOSFETs have been continuously reduced to enhance packing density and device speed in VLSI circuits. Accompanied with this scaling down of device features, however, are many undesirable side effects that can pose serious limitations on reliability. The major concern has been with the increasingly large electric fields that result from the decreasing channel length. Hot carriers resulting from these high electric fields can severely degrade device characteristics. Hence, the stability of short channel MOSFETs is a growing area of concern in VLSI. It has thus become imperative to clarify hot carrier phenomena.

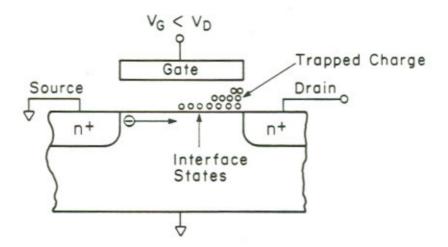

Hot carrier induced degradation of device characteristics under DC bias stress has been well researched. Device degradation has been attributed to carriers being accelerated in the high field region near the drain. This in turn gives rise to hot carrier generation via impact ionization. These hot carriers break or strain interfacial bonds, generating interface

states or are injected into the interface/oxide region, giving rise to interface and/or oxide trapped charge.

More recently, device stability under pulsed or AC biasing is being extensively studied, since AC stress simulates the device operating conditions in actual circuit applications. However, the mechanism for dynamic degradation under AC stress has not been fully clarified thus far. It is not clear to date whether or not the same kind of mechanisms for device degradation may be operative under both AC and DC biases. Also it is not clear whether or not DC and AC measurement of parameter shift arising from a common DC stress are the same. There is growing evidence that additional dynamic mechanisms may enter into AC bias induced hot carrier effects.

Present AC hot carrier treatment is primarily based on empirical modeling and computer simulation rather than upon experimental data. This simulation work makes two important assumptions. First, that the observed degradation of device electrical parameters under DC measurement is the same as that under AC measurement, and second, that AC hot carrier stress behaves similarly to DC stress for a small increment of time (quasi-static assumption). The purpose of this thesis is to test experimentally these two assumptions.

For this purpose, the DC and AC behavior of NMOS and PMOS devices was examined under DC and AC stress. However, there were some experimental limitations that need to be pointed out. AC measurement data was restricted by the 20 ns circuit resolution. Also the frequency of AC stress was limited by circuit parasitics to 10 MHz.

The major thrust of this thesis is directed toward the characterization and comparison of, (i) DC and AC measurement of device parameters following DC stress, and (ii) DC and AC stress in terms of parameter shifts measured under DC bias conditions. This thesis is divided into six chapters. Chapter 2 presents a survey of the background literature in these areas. The description of experiments performed during the course of this study is given in chapter 3. In chapter 4, the results obtained are presented and discussed. Chapter 5 presents the qualitative interpretation of the data, and in chapter 6 the highlights of the work are summarized, together with a few concluding remarks.

#### CHAPTER 2

# BACKGROUND LITERATURE

Hot carrier induced degradation of device characteristics under DC conditions has been well characterized and researched. A survey of published literature shows that the hot carrier problem has been extensively studied for both n- and p-channel MOSFETs. The primary source of device degradation is generally believed to be the same for both n- and p-channel cases, namely high electric fields and the resulting impact ionization [1]. However, the manifestation of this damage is markedly different in these two types of devices.

#### 2.1 NMOS

Hot carrier effects in n-channel transistors were studied by Hu et al. in 1985 [2]. They presented a physical model which relates the large channel electric field to the shifts in pertinent device parameters. The model was based on this high electric field causing (i) impact ionization giving rise to substrate current, (ii) hot electron emission producing gate current, and (iii) interface damage resulting in interface state generation.

Hu et al. pointed out that NMOS degradation shows up primarily in

three device parameters, a shift in threshold voltage, Vt, subthreshold swing, S and transconductance, Gm. The authors proposed that n-channel hot electron induced degradation is mainly caused by the generation of interface states rather than by electron trapping in the oxide. Furthermore, these interface states reduce local carrier density and mobility and are generated by hot electrons rather than by hot holes. Additionally, data were presented to support a linear correlation between Vt, S and Gm via the total number of generated interface states [2].

Much work has been focused on correlating n-channel MOSFET degradation to interface state generation and oxide trapping. In 1988 Robin et al. presented a hot electron oxide trapping model to explain NMOS degradation [3]. They use the bond-stretching model of the Si-SiO2 interface of Sakurai and Sugano [4]. Specifically, weak and stretched bonds with varying angles introduce a continuum of shallow and deep level traps. Robin et al. point out that although improved oxidation technology has reduced trap concentration, shallow trap levels persist in the oxide bulk and deep trap levels near the interface because of its higher density of strained and dangling bonds.

In 1987 Chen et al. studied electron trap generation during high oxide field stressing [5]. They proposed that neutral electron traps could be generated by the energy released during the recombination of free electrons and trapped holes, and that this is the mechanism of electron trap generation during high field oxide stressing. Chen et al. explain this recombination induced trap generation in a manner as may occur in the two carrier model.

The two carrier model was proposed by S. K. Lai in 1981. This model pointed out a key mechanism responsible for generating the interface and/or oxide trap states. The model is based on the (i) injection and subsequent trapping of holes in the oxide, and (ii) the capture of injected electrons by trapped holes [6]. It is important to note, as pointed out by Lai, that this is not the usual recombination process that occurs in silicon. When a hole enters a strained bond, and reaches a lower energy state by deforming it further, it is trapped by the strained bond. Electron trapping by holes could then be described as electron capture by Coulombic attractive charge centers. When trapped holes capture electrons, deformed bonds cannot be restored to their original states. In this manner, neutral traps would be formed both in the oxide bulk and at the interface.

In 1987 Tsuchiya performed experiments to distinguish the effect of the electron trapping in the gate oxide from that of interface trap generation [7]. He concluded that transconductance degradation was caused by both trapped electrons and generated interface traps. However, the effect of interface traps becomes increasingly important and that of trapped electrons less important, as degradation increased.

In 1986 the oxide trapping properties were examined by Nissan-Cohen et al. with charge injection stress experiments [8]. They presented a dynamic oxide trapping model based on two competing processes: (i) the continuous trapping of a portion of the injected electrons in localized oxide states, and (ii) the detrapping of the electrons from occupied traps. Their data showed that the rate of trap generation increased exponentially with the oxide electric field, and that only a small fraction of the newly generated traps are occupied. Hence, measured oxide charge buildup does not accurately reflect the actual increase in generated traps.

Instabilities in n-channel transistors have been reported to be markedly increased at stress bias conditions that cause peak substrate current [9,10]. It has also been suggested that both hot holes and hot electrons generated by impact ionization, together with high energy electrons in the channel, play an important role in device degradation [10-12].

In addition to the interface state generation [2,13,14], increased source/drain series resistance [14-16], decreased effective mobility [2,14,15], velocity saturation [16-18] and charge trapping localized near the drain

[7,19,20] have also been considered as possible mechanisms for device degradation. These phenomena are all collectively responsible for the observed decrease in Gm, decrease in Idsat, increase in Vt and increase in S [2,13, 15,19,21].

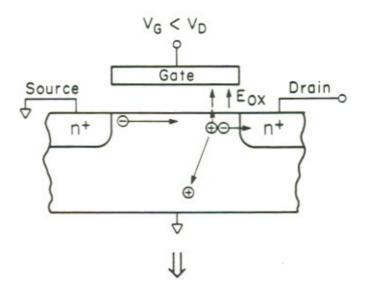

In 1988 Trocino et al. related some of these hot carrier effects in the n-channel to the stress bias [22]. They proposed that the degradation observed with a positive gate oxide electric field stress, i.e. (Vg > Vd) is a result of localized electron trapping in the oxide near the drain. On the other hand, the damage resulting from a negative electric field stress, i.e. (Vg < Vd) is primarily from interface trap generation localized near the drain.

# 2.2 PMOS

Recently, hot carrier induced degradation in p-channel devices has been a growing area of concern as well. Hot carrier effects in p-channel devices differ considerably from those in n-channel devices.

Instabilities in p-channel transistors have also been reported to be considerably enhanced at stress bias conditions causing peak substrate current as in the n-channel case [9,23]. However, more recent work indicate that the enhanced damage in p-channel transistors is more closely

correlated to peak gate current [10,24,25]. Hot electrons induced by impact ionization have been suggested to be primarily responsible for device damage [25]. Again this is in contrast to the n-channel case where both hot electrons and hot holes are believed to cause degradation [12,26]. Differences in the polarity of the effective gate field, i.e. a positive or negative field, account for how the hot carriers are injected into the gate oxide and reach the gate terminal near the drain region. In the p-channel device operating in the saturation region, (Vg > Vd) hot electrons are pulled into the oxide, some will be trapped and others will traverse the oxide to constitute the gate current. Holes are swept from the channel to the drain terminal. Simultaneously hot electrons are also pulled towards the substrate to constitute substrate current. Again this is in contrast with the n-channel operating in the saturation region, where the polarity of the bias is switched. Thus, for the n-channel case, holes contribute to both gate and substrate currents. Most of the electrons are swept from the channel to the drain terminal while some are believed to be trapped in the interface [19,25,26,27].

The different physical processes involved in n- and p-channel devices give rise to contrasting damage effects. Specifically, the directions of device parameter shifts in the n- and p-channel, are often opposite to each other. For the case of the p-channel device, this damage is exhibited in an

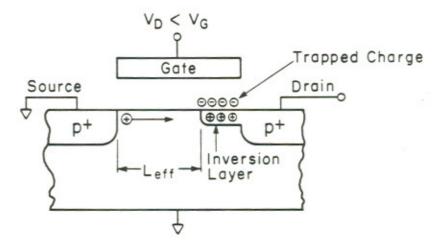

increased Idsat, an increased Gm, a decreased | Vt | and an increased S [10,25,28,29]. These shifts in device parameters are explained in the literature as follows. Impact ionization induced hot electrons are accelerated by the positive gate field into the gate oxide near the drain. Consequently, electrons are trapped near the oxide interface, inverting the surface to p-type, and resulting in an extension of the p+ drain region. This in effect reduces the effective channel length [14,19,25]. Koyanagi et al. caution that the decrease in punchthrough voltage which results from trapped electrons creating a shortened channel, may place a fundamental limitation on device scaling [25].

Hot carrier effects have been examined in n- and p-channel devices when the measurement was done with the source and drain terminals interchanged from that of the applied stress [30-32]. In 1983 Lombardi et al. measured electrical parameters before and after stress using the same (forward) and opposite (reverse) polarity, to that of the applied stress. Data showed an enhanced degradation for parameters measured in the reverse mode. They explained this finding in terms of the potential energy barrier lowering caused by the trapped charge. That is, electrons trapped closer to the injecting terminal (i.e. the terminal used as the source) would be more effective in reducing the surface potential than electrons trapped near the terminal used as the drain [33]. More measurable

degradation in the reverse mode can also be accounted for with the decreased screening of the trapped charge that occurs with the smaller source junction depletion region [32].

# 2.3 AC STRESS

The study of AC hot carrier induced degradation is important since the device operates in a dynamic AC environment in actual circuit applications.

Until recently, most AC hot carrier treatment was primarily based on empirical modeling and computer simulation rather than experimental data. Quasi-static models were used, based upon the assumption that AC hot carrier stress behaves similarly to DC stress for small time increments. Kuo et al. voiced a concern about the applicability of a quasi-static model and the use of DC stressing data for AC stressing lifetime predictions [34]. To support their concern, they cited the work of Weber et al., showing that enhanced degradation occurs as a result of fast high to low gate transients in the presence of a high drain bias [11]. They proposed that this was due to the simultaneous presence of a very high channel field and a large capacitive drain current, which produced an additional component of substrate current during the falling edge of the gate pulse. This

capacitative current cannot be incorporated into the quasi-static substrate current model. Interesting experimental evidence was also reported by Bellens et al. in 1988 [35]. They observed that the switching off of the transistor causes substrate current which keeps flowing during the gate switch off period, another condition not covered in the quasi-static model.

While hot carrier induced damage under DC stress has been well characterized, no unanimous agreement exists on the mechanism for AC degradation. However, there appears to be some consensus, namely, that dynamic degradation may involve an additional mechanism arising from the periodic switching of field conditions [35-37].

In 1988 Cham et al. reported that the degradation of electrical characteristics of AC stressed n-channel MOSFETs is not in general commensurate with the DC results [38]. Specifically, AC drain stress is equivalent to DC stress by the active duty cycle. However, AC gate stress produced much more damage than the duty cycle factor would have indicated. The authors proposed that it was the gate voltage swing from high to low value under constant high drain bias that caused the most severe damage.

In 1988 Ong et al. reported a similar conclusion for p-channel MOS-FETs when the gate pulse turn-off transient was short, concurrent with a high drain voltage [37]. Aoki et al. evaluated hot carrier effects under pulsed stress in CMOS inverters in 1987 [39]. Their data suggested that (i) trap and/or interface state generation was dominant rather than trap filling, and (ii) trap generation was enhanced by pulsed stress.

Various studies on the effects of AC stress on device performance have made use of the two carrier model of S. K. Lai [6] to explain AC degradation phenomena.

In 1988 Weber studied AC stressing using separate pulses applied to the drain and gate [40]. He proposed a qualitative model of AC hot carrier degradation which emphasized the important part that holes had in the final formation of interface states. His model incorporated the two carrier model of S. K. Lai [6], i.e. postulating that injected electrons could be captured by injected trapped holes, resulting in the formation of interface states. Furthermore, Weber proposed that with increasing damage, the number of hole traps increased and the hole energy barrier decreased, so that the hole injection efficiency was further increased.

In 1987 Choi et al. reported the effects of AC gate and drain voltage transients on hot carrier induced NMOS degradation [41]. They concluded that, while AC drain stress voltage transients had little effect on the degradation rate, AC gate voltage transients increased the degradation rate. They further suggested that this finding could be attributed to enhanced surface state generation as may occur in the two carrier model [6]. Doyle et al. reported dynamic NMOS stress data and suggested that both types of charge species were needed in the oxide for enhanced surface state generation [36], again in support of the two carrier model [6].

In 1984 Hofmann et al. carried out n-channel AC stress hot carrier experiments [42]. They also proposed a degradation mechanism in accord with the two carrier model [6], and correlated the observed enhanced degradation under pulsed stress to the presence of fast hole traps close to the interface. For the static case, these traps were postulated to be positively charged, causing the effective carrier injection to be screened by the field near the drain. However, in the pulsed case, these traps emptied in the time between pulses such that there was a certain time elapse before they were filled again. Consequently, under these conditions there was a period of increased effective carrier injection, causing increased degradation.

Igura and Takeda reported on the hot carrier effect from dynamic stressing using different n- and p-channel device structures [43]. They postulated that the initial electric field distribution at the instant of every AC pulse would differ from that of the DC stress, depending upon the amount of electron detrapping, i.e. the trap lifetimes. Data showed that for certain n-channel device structures, the field could become larger, causing more damage than the active duty cycle would have indicated. The majority of p-channel data showed that AC degradation was qualitatively the same as that under DC stress.

# 2.4 CHARGE PUMPING

Hot carrier-assisted interface state generation has been shown to be one of the primary consequences for DC and AC stress in both n- and p-channel devices [14]. It has been pointed out that the charge pumping technique can provide an improved evaluation of the damaged interface. Specifically, the technique can monitor interface state generation free of the various masking effects due to trapped charge [14,44]. Hence, a survey of literature on charge pumping is due.

The charge pumping experiment was first initiated by Brugler and Jespers in 1969 [45]. The experiment consists of applying a pulse train to the gate and a small reverse bias to the source and drain, while the DC substrate current is recorded. Since mobile channel carriers are swept to the source and drain, the substrate current consists of the carriers that are detrapped from the surface states. Thus, the substrate or charge

pumping current can provide useful surface state information.

In 1976 A. Elliot used charge pumping currents to measure surface state densities [46]. He used this technique as a means of separating the contributions made by fast surface states and fixed oxide charges to threshold voltage shift. He noted the importance of surface state time constants. For example, he pointed out that while most measurements were carried out under steady state conditions, devices in actual circuit applications might be operating at speeds faster than the response time of some of the surface states. Consequently, transistors could have some high frequency characteristics that differed from those under steady state conditions.

In 1984 Groeseneken et al. carried out charge pumping measurements to determine the Si-SiO2 interface state density on MOS transistors [47]. They presented a model for charge pumping current, based on the emission of electrons and holes to the conduction and valence bands respectively, under both equilibrium and non-equilibrium conditions. The model also analyzed the surface band bending under transient gate biasing and the concomitant trapping and detrapping of electrons and holes.

In 1987 Tseng modified the standard charge pumping technique used for interface state density measurements [48]. His work was motivated by the fact that interface states can act as either traps or recombination centers depending on the characteristics of the applied gate waveform. By tailoring the gate voltage pulses in time and analyzing the surface band bending with respect to the Fermi level, he was able to separate the states which behaved as traps from those which acted as recombination centers.

In 1986 Heremans et al. used the charge pumping technique in examining NMOS degradation [49]. They concluded that the two carrier model [6] is indeed valid for fast interface states. More recently, they pointed out that device parameter shifts partially reveal the physical damage at the interface, and that a more precise evaluation of interface degradation can only be made using charge pumping data in conjunction with parameter shift data [14].

Thus, much work has been done to contribute toward a better understanding of the hot carrier phenomenon and its effect upon device degradation. Yet the complexity of the problem leaves many areas open to further investigation and some questions still unanswered.

# REFERENCES

- W. Shockley, "Problems related to p-n junctions in silicon," Solid State Electron., vol. 2, No. 1, pp.35-67, 1961.

- C. Hu, S. C. Tam, F.-C. Hsu, P. Ko, T. Chan, and K. W. Terrill,

"Hot -electron-induced MOSFET degradation- model, monitor, and

improvement," IEEE Trans. Electron Devices, vol. ED-32, No. 2, pp.

375-385, 1985.

- P. Roblin, A. Samman, and S. Bibyk, "Simulation of hot-electron trapping and aging in n-MOSFET's," IEEE Trans. Electron Devices, vol. 35, No. 12, pp. 2229-2236, 1988.

- T. Sakurai and T. Sugano, "Gap states of crystalline silicon and amorphous SiO2 system," Proc. Int. Topical Conf. Phys. MOS Insulators (Raleigh, NC, June 18-20, 1980). New York: Pergamon, 1980.

- I. C. Chen, S. Holland, and C. Hu, "Electron-trap generation by recombination of electrons and holes in SiO2," J. Appl. Phys. 61(9), pp.4544-4548, 1987.

- S. K. Lai, "Two-carrier nature of interface-state generation in hole trapping and radiation damage," Appl. Phys. Lett., vol. 39, No. 1, pp. 58-60, 1981.

- T. Tsuchiya, "Trapped-electron and generated interface-trap effects in hot-electron-induced MOSFET degradation," IEEE Trans. Electron Devices, vol. ED-34, No. 11, pp.2291-2296, 1987.

- Y. Nissan-Cohen, J. Shappier, and D. Frohman-Bentchkowsky, "Trap generation and occupation dynamics in SiO2 under charge injection stress," J. Appl. Phys., 60(6) pp.2024-2035, 1986.

- R. Bellens, P. Heremans, G. Groeseneken, and H. E. Maes, "Characterization and analysis of hot-carrier degradation in p-channel transistors using constant current stress experiments," Solid State Devices, pp.261-264, 1988.

- 10. M. Koyanagi, A. G. Lewis, R. A. Martin, T. Huang, and J. Y. Chen, "Hot electron induced punchthrough in submicron PMOSFETs," Extended Abstr. of the 18th Conf. Solid State Devices and Mater. (Tokoyo, Japan), pp.475-478, 1986.

- W. Weber, C. Werner, and G. Dorda, "Degradation of N-MOStransistors after pulsed stress," IEEE Electron Device Lett., vol. EDL-5, No. 12, pp.518-520, 1984.

- K. P. Hofmann, C. Werner, W. Weber, and G. Dorda, "Hot-electron and hole-emission effects in short n-channel MOSFETs" IEEE Trans. Electron Devices, vol. ED-32, No. 3, pp.691-699, 1985.

- F.-C. Hsu and S. Tam, "Relationship between MOSFET degradation and hot-electron-induced interface-state generation," IEEE Electron Device Lett., vol. EDL-5, No. 2, pp.50-52, 1984.

- P. Heremans, R. Bellens, G. Groeseneken, and H. E. Maes, "Consistent model for hot-carrier degradation in n-channel and p-channel MOSFET's, IEEE Tran. Electron Devices, vol. 35, No. 12, pp.2194-2209, 1988.

- F.-C. Hsu and H. R. Grinolds, "Structure-enhanced MOSFET degradation due to hot-electron injection," IEEE Electron Device Lett., vol. EDL-5, No. 3, pp.71-74, 1984.

- H. Shichijo, "A re-examination of practical scalability limits of nchannel and p-channel MOS devices for VLSI," IEDM Tech. Dig., pp.219-222, 1981.

- F. F. Fang and A. B. Fowler, "Hot electron effects and saturation velocities in silicon inversion layers," J. Appl. Phys., vol. 41, No. 4, pp.1825-1831, 1970.

- S. Tam, P. Ko, C. Hu, and R. S. Muller, "Correlation between substrate and gate currents in MOSFET's, IEEE Trans. Electron Devices, vol. ED-29, No. 11, pp.1740-1744, 1982.

- K. K. Ng and G. W. Taylor, "Effects of hot-carrier trapping in nand p-channel MOSFET's," IEEE Trans. Electron Devices, vol. ED-30, No. 8, pp.871-876, 1983.

- 20. H. Matsumoto, K. Sawada, S. Asai, M. Hirayama, and K. Nagasawa, "Effect of long-term stress on IGFET degradations due to hot electron trapping," IEEE Trans. Electron Devices, vol. ED-28, No. 8, pp.923-928, 1981.

- E. Takeda and N. Suzuki, "An empirical model for device degradation due to hot-carrier injection," IEEE Electron Device Lett., vol. EDL-4, No. 4, pp.111-113, 1983.

- M. R. Trocino, K. Fu, and K. Teng, "Stress-bias dependence of hotcarrier-induced degradation in MOSFETs," Solid State Electron., vol. 31, No. 5, pp.873-875, 1988.

- J. J. Tzou, C. C. Yao, R. Cheung, and H. W. K. Chen, "Hotcarrier-induced degradation in p-channel LDD MOSFET's," IEEE Electron Device Lett., vol. EDL-7, No. 1, pp.5-7, 1986.

- 24. M. P. Brassington and R. R. Razouk, "The relationship between gate bias and hot-carrier-induced instabilities in buried-and-surface-channel PMOSFETs," IEEE Trans. Electron Devices, vol. 35, No. 3, pp.320-323, 1988.

- 25. M. Koyanagi, A. G. Lewis, R. A. Martin, T. Huang, and J. Chen, "Hot-electron-induced punchthrough (HEIP) effect in submicrometer PMOSFET's," IEEE Trans. Electron Devices, vol. ED-34, No. 4, pp. 839-844, 1987.

- 26. E. Takeda, H. Kume, T. Toyabe, and S. Asai, "Submicrometer MOS-FET structure for minimizing hot-carrier generation," IEEE Trans. Electron Devices, vol. ED-29, No. 4, pp.611-618, 1982.

- R. B. Fair and R. C. Sun, "Threshold-voltage instability in MOSFET's due to channel hot-hole emission," IEEE Trans. Electron Devices, vol. ED-28, No. 1, pp.83-94, 1981.

- 28. W. Weber and F. Lau, "Hot-carrier induced degradation in submicron p-MOSFET's," IEEE Colloquium on 'Hot Carrier Degradation in Short Channel MOS,' Dig. No. 15, pp. 6/1-6/3, 1987.

- 29. M. P. Brassington and R. R. Razouk, "Relationship between gate bias and hot-carrier induced instabilities in p-channel MOSFETs," Tech. Dig. 1987 Symp. on VLSI Technol., pp. 55-56, 1987.

- C. Lombardi, P. Olivo, B. Ricco, E. Sangiorgi, and M. Vanzi, "Two-dimensional effects in hot-electron modified MOSFETs," IEEE Trans. Electron Devices, vol. ED-30, No. 10, pp.1416-1419, 1983.

- M. Koyanagi, A. Lewis, R. Martin, T. Huang, and J. Chen, "Increased degradation of half-micron PMOSFETs due to swapped pulse stressing," IEDM Tech. Dig., pp.844-847, 1987.

- 32. F. Matsuoka, H. Hayashida, K. Hama, Y. Toyoshima, H. Iwai, and K. Maeguchi, "Drain avalanche hot hole injection mode on PMOS-FETs," IEDM Tech. Dig., pp.18-21, 1988.

- 33. R. R. Troutman, T. V. Harroun, P. E. Cottrell, and S. N. Chravarti, "Hot-electron design considerations for high-density RAM chips," IEEE Trans. Electron Devices, vol. ED-27, No. 8, pp.1629-1639, 1980.

- 34. M. M. Kuo, K. Seki, P. M. Lee J. Y. Choi, P. K. Ko, and C. Hu, "Quasi-static simulation of hot-electron-induced MOSFET degradation under AC (pulse) stress," IEDM Tech. Dig., pp. 47-50, 1987.

- 35. R. Bellens, P. Heremans, G. Groeseneken, and H. E. Maes, "Analysis of mechanisms for the enhanced degradation during AC hot carrier stress of MOSFET's," IEDM Tech. Dig., pp.212-215, 1988.

- 36. B. S. Doyle, M. Bourcerie, J.-C. Marchetaux, and A. Boudou, "Dynamic channel hot-carrier degradation of NMOS transistors by enhanced electron-hole injection into the oxide" IEEE Electron Device Lett., vol. EDL-8, No. 5, pp.237-239, 1987.

- T.-C. Ong, K. Seki, P. K. Ko, and C. Hu, "Hot-carrier-induced degradation in p-MOSFETs under AC stress," IEEE Electron Device Lett., vol.9, No.5, pp.211-213, 1988.

- K. M. Cham, H. Fu, and Y. Nishi, "The dependence of hot carrier degradation on A.C. stress waveforms," IEDM Tech. Dig., pp. 30-33, 1988.

- M. Aoki, K. Yano, T. Masuhara, and K. Komiyaji, "Hot-carrier effects under pulsed stress in CMOS devices," Tech. Dig. 1987 Symp. on VLSI Technol., pp.49-50, 1987.

- W. Weber, "Dynamic stress experiments for understanding hot-carrier degradation phenomena," IEEE Trans. Electron Devices, vol.35, No.9, pp.1476-1486.

- J. Y. Choi, P. K. Ko, and C. Hu, "Hot-carrier-induced MOSFET degradation under AC stress," Electron Device Lett., vol. EDL-8, No. 8, pp.333-335, 1987.

- K. R. Hofmann, W. Weber, C. Werner, and G. Dorda, "Hot carrier degradation mechanism in n-MOSFETs," IEDM Tech. Dig., pp. 104-107, 1984.

- 43. Y. Igura and E. Takeda, "Hot-carrier degradation mechanism under AC stress in MOSFETs," Tech. Dig. 1987 Symp. on VLSI Technol.,

- pp.47-48, 1987.

- 44. R. Bellens, P. Heremans, G. Groeseneken, and H. E. Maes, "A new procedure for lifetime prediction of n-channel MOS-transistors using the charge pumping technique," IRPS Proc., pp.8-14, 1988.

- J. S. Brugler and P. G. Jespers, "Charge pumping in MOS devices,"

IEEE Trans. Electron Devices, vol. ED-16, No. 3, pp.297-302, 1969.

- 46. A. B. M. Elliot, "The use of charge pumping currents to measure surface state densities in MOS transistors," Solid State Electron., vol. 19, pp.241-247, 1976.

- 47. G. Groeseneken, H. E. Maes, N. Belton, and R. F. DeKeersmaecker, "A reliable approach to charge-pumping measurements in MOS transistors," IEEE Trans. Electron Devices, vol. ED-31, No.1, pp.42-53, 1984.

- W. L. Tseng, "A new charge pumping method of measuring Si-SiO2 interface states," J. Appl. Phys., 62(2), pp.591-599, 1987.

- 49. P. Heremans, H. E. Maes, and N. Saks, "Evaluation of hot carrier degradation of n-channel MOSFET's with the charge pumping technique," IEEE Electron Device Lett., vol. EDL-7, No. 7, pp.428-430, 1986.

# CHAPTER 3

# DESCRIPTION OF EXPERIMENT

# 3.1 Experiment

The experimental objectives were to test the two premises upon which previous AC simulation work had been based: 1) AC and DC parameter measurement equivalence, and 2) AC and DC stress equivalence for small time increments (quasi-static assumption).

Single n- and p-channel MOSFETs were fabricated at Intel and packaged for examination. Although the single transistor configuration may not occur in actual circuit applications, it is important to understand the physics of stress, based on the single transistor operation. Stress was applied to devices under both AC and DC conditions. Device stress, as used in this experiment, is the simultaneous application of an increased source-drain voltage and a worst case gate voltage in the saturation region. The worst case gate voltage was the gate bias at which the maximum substrate current for n-channel and the maximum gate current for p-channel devices are induced. It is under these high electric field conditions that carriers in the channel become 'hot', i.e. gain enough energy before an

energy stripping collision to cause device degradation.

#### 3.2 AC vs. DC Measurement

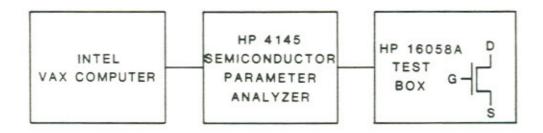

Data was collected using 20 packaged p-channel and 10 n-channel one micron technology MOSFETs. The same testing sequence, DC measurement, AC measurement and charge pumping, was followed before and after DC stress. The electrical parameters of the transistor under test were measured under low noise DC conditions according to the scheme shown in Fig. 1.

The application of DC stress biases and measurement of electrical parameters were performed by the use of an Intel Vax-controlled computer program in conjunction with a HP 4145 semiconductor parameter analyzer and a HP 10658A test box. This DC characterization consisted of measuring quantities such as drain saturation current, Idsat, threshold voltage, Vt, transconductance, Gm and subthreshold swing, S.

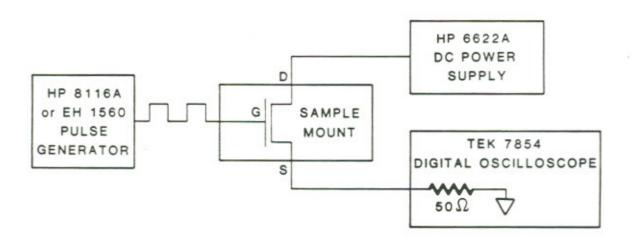

The value of Idsat was also measured under low and high frequency low distortion AC conditions following the setup described in Fig. 2. A packaged transistor was enclosed in a Faraday shielded box, while a HP 8116A pulse generator pulsed the gate and a HP 6622A DC power supply biased the drain. The source was connected to a 50 ohm Tektronix Digital

Figure 1: Block diagram for DC characterization and DC stressing.

Figure 2: Block diagram for AC characterization.

oscilloscope termination. Comparisons of AC and DC measurement were carried out based on AC and DC Idsat values. The parameter of Idsat was selected primarily because of its direct measurability under AC conditions. Idsat values were computed by recording transistor output voltages divided by the 50 ohm oscilloscope termination. This output resistance value was small enough to insure that saturation drain current would be measured and that the resistor voltage drop would be a negligible percentage of the bias voltage.

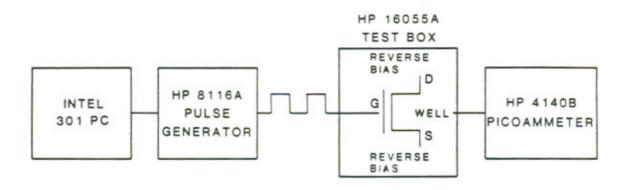

Additionally, charge pumping experiments were carried out both before and after DC stress. The experiment involves the application of a train of voltage pulses to the gate, while a small DC reverse bias is applied to both the source and drain and the DC substrate current is recorded. As shown in Fig. 3, this was performed by means of an Intel 301 PC-controlled computer program, a HP 8116A pulse generator, a HP 16055A test box and a HP 4140B picoammeter. As the gate is pulsed, the channel is cycled between inversion and accumulation, causing a repetitious charging and discharging of the Si-SiO2 interface states. Under this condition, the trapped minority carriers recombine with substrate majority carriers during accumulation, and result in recombination current, i.e. charge pumping current, Icp [1].

Figure 3: Block diagram for charge pumping.

This experiment is based upon the following assumptions. First, that mobile minority carriers induced in the channel drift back to the source and drain, and do not contribute to the charge pumping current. Second, that channel inversion time is sufficiently long for carriers to be trapped at the interface. Third, that pulse switching time is long enough to allow mobile inversion minority carriers to drift back to the source and drain. Additionally, the application of square gate pulses with fixed rise and fall times, made possible the assumption that there was a constant amount of emitted charge per cycle, and consequently, the same recombining charge, Qss per cycle [1-4].

$$Icp = \frac{Qss}{second} \tag{1}$$

$$Icp = Qss \cdot frequency$$

(2)

The increase in charge pumping current, if any, can be considered to be a monitor of interface trap density. The measurements can thus be used to evaluate hot carrier degradation in terms of interface damage and/or interface state generation [1].

## 3.3 AC vs. DC Stress

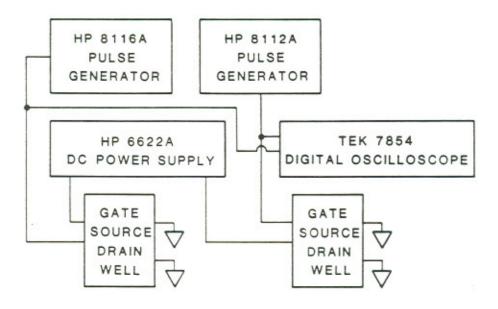

Data was collected from 30 p-channel and 20 n-channel submicron technology devices from the same run using the scheme shown in Fig. 4.

DC electrical parameter measurements were made on devices before and after high frequency low distortion AC stress. AC stress time was assumed to correspond to the pulse active duty cycle time.

Comparisons were made for three groups of bias conditions, differing in whether the applied voltage was AC or DC. These included (a) DC drain with DC gate bias, (b) AC drain with DC gate bias and (c) AC gate with DC drain bias. The transistors which were compared were from the same process run and device structure. An additional precaution was made by selecting devices with essentially the same substrate current for each of the above three stress conditions. The substrate current was measured at fixed bias conditions before any applied stress. These measurement conditions consisted of a fixed drain voltage under worst case bias conditions, i.e. Vd=7.0V and Vg =2.0V for n-channel and Vd=-5.5V and Vg=-1.0V for p-channel devices. This method of categorization compensated for any discrepancies in effective channel length and bias that might be present. In this way, any differences in transistor degradation could be attributed to differences in the three stress cases, (a),(b) and (c).

Figure 4: Block diagram for AC stressing.

The details of the test conditions have been relegated to the appendix.

### REFERENCES

- R. Bellens, P. Heremans, G. Groeseneken, and H.E. Maes, "A new procedure for lifetime prediction of n-channel MOS-transistors using the charge pumping technique," IRPS Proc., pp. 8-14, 1988.

- G. Groeneken, H. E. Maes, N. Belton, and R. F. DeKeersmaecker, "A reliable approach to charge-pumping measurements in MOS transistors," IEEE Trans. Electron Devices, vol. ED-31, No. 1, pp.42-53, 1984.

- J. S. Brugler and P. G. Jespers, "Charge pumping in MOS devices,"

IEEE Trans. Electron Devices, vol. ED-16, No. 3, pp. 297-302, 1969.

- A. B. M. Elliot, "The use of charge pumping currents to measure surface state densities in MOS transistors," Solid State Electron., vol. 19, pp.241-247, 1976.

#### CHAPTER 4

## RESULTS

This chapter summarizes the experimental results obtained during the course of this thesis. As mentioned in the previous chapter, the experiments were designed (i) to compare AC and DC measurements of MOS-FET parameters before and after DC stress and, (ii) to compare AC and DC stress in terms of DC measurements of MOSFET parameters before and after stress.

A brief look at MOSFET operation is needed at this point for a clearer presentation of these results. The MOSFET is a three terminal device, in which source-drain current is controlled by the gate voltage. Since the gate terminal is insulated from the channel by a high impedance dielectric material, it draws virtually no current. Hence, by changing the gate bias, the conducting channel between the source and drain turns off and on [1]. Three types of charge states are induced under the gate as a result of the change in gate bias. These include (i) the 'accumulation' of majority carriers, (ii) the 'depletion' of majority carriers, and (iii) the induction of minority carriers. The device turns on when the gate voltage exceeds the threshold voltage, Vt the minimum gate voltage required to

invert the surface and induce the conducting channel.

It is important to define threshold voltage measurement, since it can be measured in different ways. Threshold voltage as defined in this experiment, was the gate voltage at which 10  $\mu$ A of drain current were measured for a fixed aspect ratio under a fixed drain voltage of  $\pm$  0.1V. The aspect ratio was 50 for the n-channel devices and 60 for the p-channel devices.

When a gate voltage, Vg larger than Vt is applied, the drain bias, Vd produces a a resistor-type operation. In this triode region, the drain current, Id depends on both the gate and drain voltages, the oxide capacitance (Cox), mobility  $(\mu)$  and channel length (L) as [2]:

$$Id = K \cdot \left[ (Vg - Vt) \cdot Vd - \frac{Vd^2}{2} \right]$$

(3.1)

$$K = \frac{\mu \cdot Cox}{I} \tag{3.2}$$

As Vd is increased, the channel pinches off and the voltage across the channel remains fixed. In this saturation region, the drain current is controlled by the gate voltage and becomes almost independent of the drain voltage [2]:

$$Idsat = \frac{K}{2} \cdot (Vg - Vt)^2 \tag{4}$$

The transconductance is defined as  $Gm = \Delta Id/\Delta Vg$ , Vd = constant and is an important parameter affecting the small signal amplification. It is given in the linear and saturation regions respectively as [1],

$$Gm = K \cdot Vd$$

(5.1)

$$Gm = K \cdot (Vg - Vt) \tag{5.2}$$

For gate voltages less than Vt, no channel is formed, so that there is only a very low subthreshold drain current. The subthreshold swing, S is a measure of the MOSFET's turn-off characteristic. Specifically, the subthreshold swing is the gate voltage swing needed to reduce the subthreshold drain current by one decade [3]:

$$S = \frac{\Delta Vg}{\Delta Log_{10}(Id)}$$

(6)

#### 4.1 DC Measurement

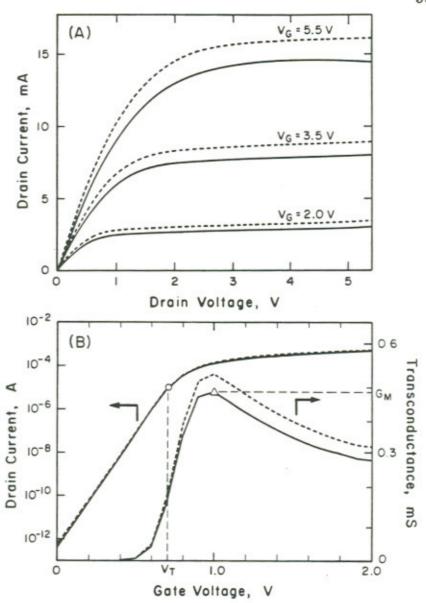

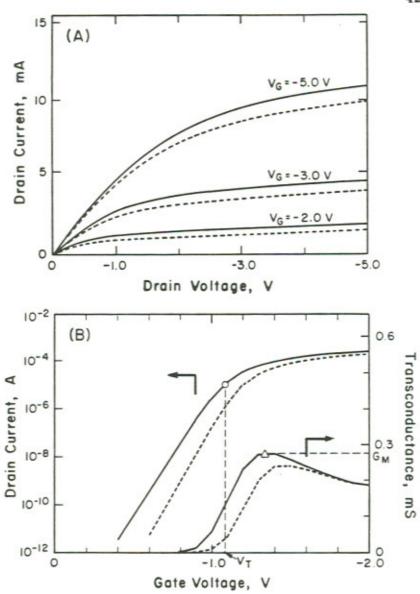

Figure 5 summarizes the typical characteristics of a n-channel transistor, i.e. Id as a function of drain voltage (A), Id, Vt and peak Gm as a function of gate voltage (B) and S as a function of stress time (C). The parameters under study, Idsat, Gm, Vt and S were measured under DC conditions before and after DC stress. Notice that Idsat and Gm are the most sensitive monitors of stress induced degradation. The effect of DC

Figure 5: N-channel transistor I-V curves (A), subthreshold characteristics and transconductance (B), before (---) and after (--) DC stress, and subthreshold swing vs. stress time (C). Stress conditions for (A) and (B) were Vd=7.0V, Vg=2.5V for 3 days. Stress conditions for (C) were Vd=7.0V, Vg=2.5V. Measurements were made with the source/drain terminals interchanged from that of the applied stress (reverse).

stress for the n-channel is manifested in:

- i) a decrease in Idsat, i.e. by 11%

- ii) a decrease in Gm, i.e. by 10%

- iii) an increase in Vt, i.e. by 1%

- iv) an increase in S, i.e. by 5%

These measured values of stress induced shifts are consistent with those reported in literature [4-7]. From these data one can conclude that (i) a degradation in mobility, (ii) an increase in series resistance, (iii) reduced surface mobile charge density via interface state generation or (iv) the combination thereof have occurred following DC stress. Note that the rise in S as a function of stress time is distinctly bimodal.

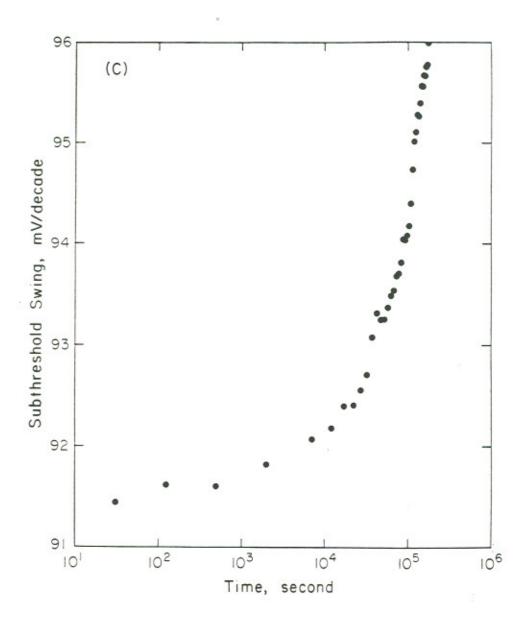

Figure 6 shows the corresponding p-channel data measured under DC conditions before and after DC stress. It is interesting to note that for the case of p-channel, most of the direction of stress induced parameter shift is in marked contrast with the n-channel case. Again Idsat and Gm are the most sensitive monitors of degradation. The effect of DC stress is manifested in:

- i) an increase in Idsat, i.e. by 30%

- ii) an increase in Gm, i.e. by 14%

- iii) a decrease in | Vt |, i.e. by 10%

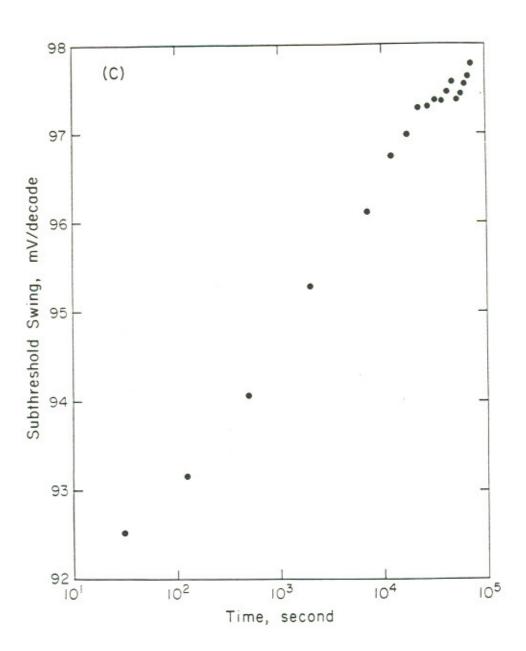

Figure 6: P-channel transistor I-V curves (A), subthreshold characteristics and transconductance (B), before (---) and after (---) DC stress, and subthreshold swing vs. stress time (C). Stress conditions for (A) and (B) were Vd=-8.0V, Vg=-1.7V for 6 hrs. Stress conditions for (C) were Vd=-9.0V, Vg=-1.7V.

# iv) an increase in S, i.e. by 11%

These measured parameter shifts again are consistent with the values reported in the literature [7-10]. A striking feature of p-channel degradation is the apparent channel shortening, as may be seen from Eqs. (3.1)-(5.2). Note that S as a function of stress time is unimodal in contrast with the n-channel case.

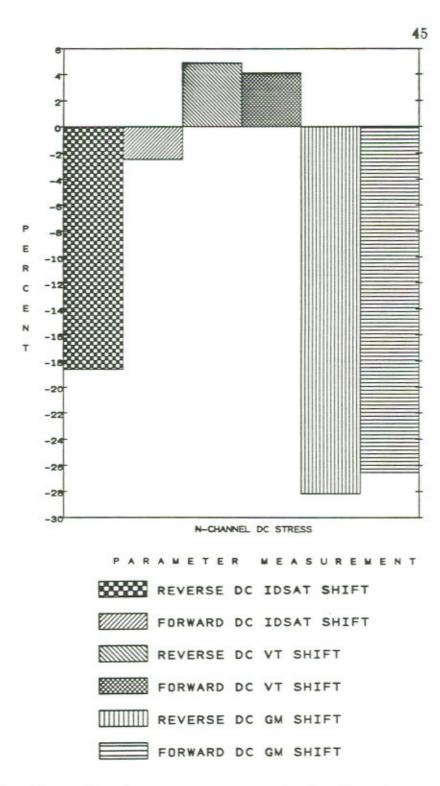

The degree of change in device characteristics measured under DC conditions is quite sensitive to the polarity of measurement with respect to the applied stress. Figure 7 presents a n-channel example of this effect. Parameters were measured with the same source/drain configuration as that of the applied stress (forward), and with the source and drain terminals interchanged (reverse). As observed in this figure, Idsat as measured in the reverse direction, decreased by 19%, while Idsat as measured in the forward direction decreased by about 3%.

This larger parameter shift measured with the source and drain terminals interchanged has been noted in literature [11]. As mentioned in chapter 2, this can be qualitatively understood as follows. A trapped charge affects the device performance more directly when it is not hidden by the depletion region, and is close to the injecting terminal where the potential energy barrier lowering is more significant [12,13].

Figure 7: Forward and reverse measurement of n-channel parameter shifts after DC stress. Stress conditions were Vd=7.0V, Vg=2.5V for 2 days.

#### 4.2 AC Measurement

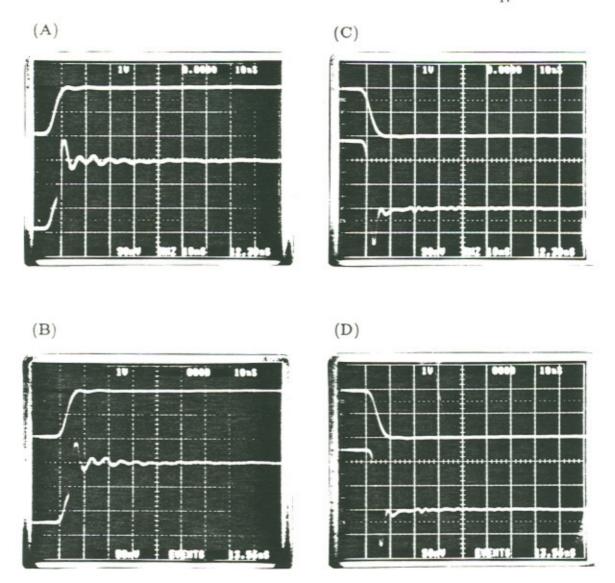

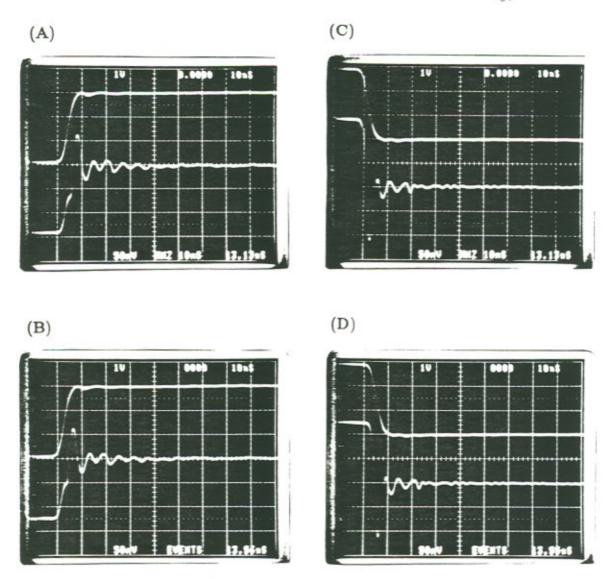

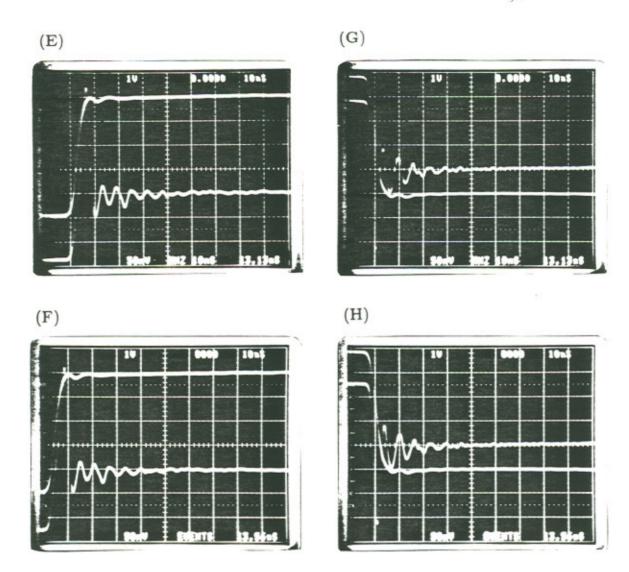

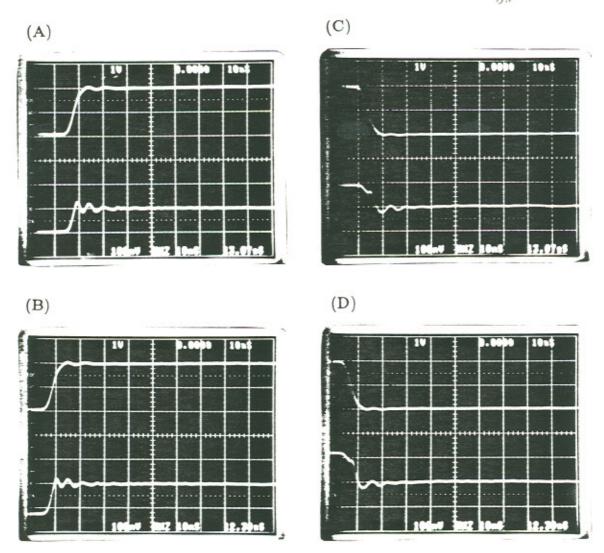

Figures 8 and 9 present the AC data, measured from the same devices whose DC data have been discussed in Figs. 5 and 6. Figures 8 (A),(B),(C) and (D) display the n-channel pre- and post-stress AC voltage waveforms measured at a frequency of 10 kHz. Each oscilloscope trace exhibits the input voltage waveform (upper signal) and the output voltage waveform (lower signal). Figures 8 (A) and (B) show the rising edge of both the input and output waveforms before and after DC stress. Figures 8 (C) and (D) show the corresponding falling edge. Circuit parasitics restricted measurement resolution to 20 ns, i.e. the time to reach steady state following overshoot. Note that the effect of stress manifests itself in the difference in the steady state output voltages, as can be clearly observed from these figures. Parasitic induced waveform overshoot and ringing is essentially the same before and after DC stress. Specifically, this n-channel device showed a 11% decrease in steady state output voltage. This explicitly indicates that Idsat is decreased by 11%, in agreement with the DC data discussed earlier. Impact ionization induced breakdown limited the upper range of stress voltages to 7.5V. Hence, stress voltages were applied for longer periods of time and measurements were taken with the source and drain terminals interchanged in order to enhance stress induced

Figure 8: N-channel gate input and load output waveforms: (A).(B) the rising edge before and after DC stress. (C).(D) the respective falling edge. Stress conditions were Vd=7.0V, Vg=2.5V for 3 days. Measurements were made in the reverse direction with 50% duty cycle pulses at a frequency of 1 MHz.

Figure 9: P-channel gate input and load output waveforms; (A),(B) the rising edge before and after DC stress, (C),(D) the respective falling edge. Stress conditions were Vd=-8.0V, Vg=-1.7V for 6 hrs. Measurements were made with 50% duty cycle pulses at a frequency of 1 MHz.

damage for examination (appendix).

Figure 9 presents the corresponding data obtained from a p-channel device using a frequency of 1 MHz. Again, the effect of stress is exhibited in the difference in the steady state output voltages. Note that the 31% output voltage level increase is in agreement with the corresponding DC data of Fig. 6. The p-channel devices were not restricted in stress voltage levels. Hence the higher bias conditions used (Vd=-8.0V, Vg=-1.7V) resulted in greater Idsat shifts.

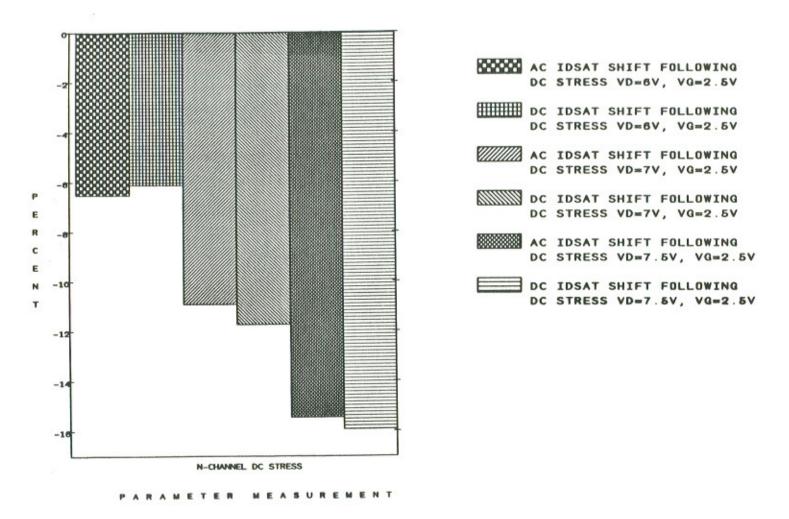

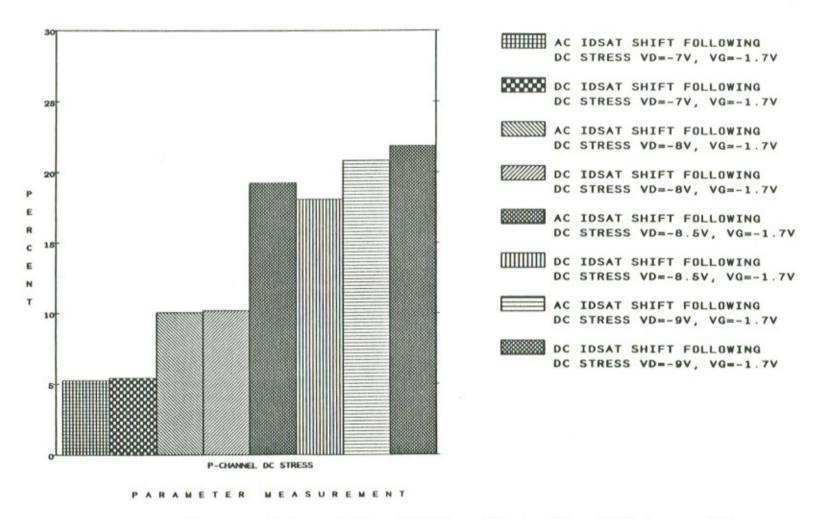

The comparison between AC and DC measurements was further carried out by systematically varying the stress conditions, i.e. by changing the drain voltages for a fixed gate voltage. As can be observed from Figs. 10 and 11, the AC and DC measured shifts in n- and p-channel Idsat values, are in good agreement for all the drain voltages used.

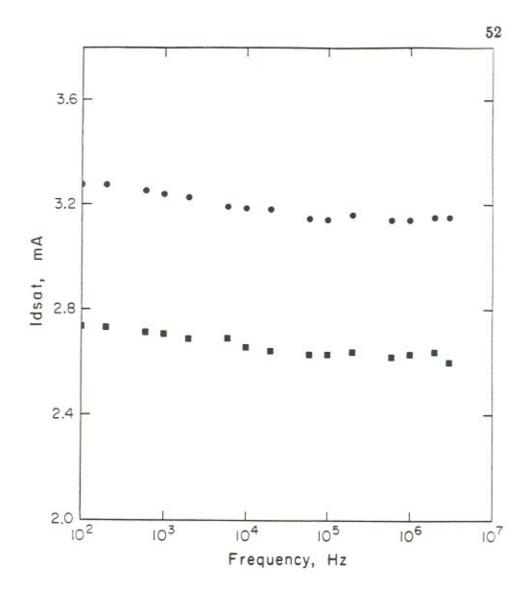

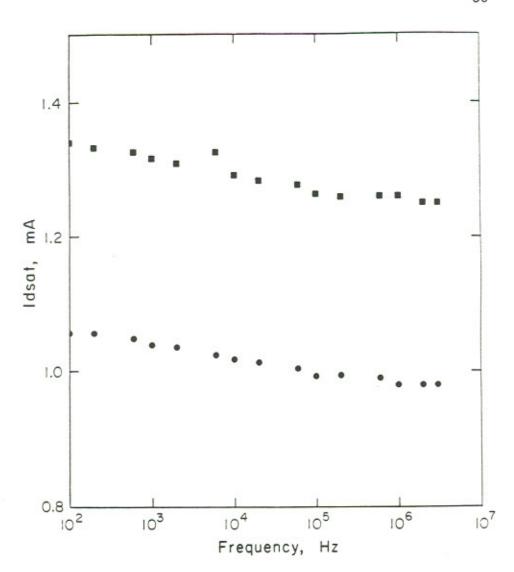

The shifts in AC Idsat values in n- and p-channel devices are now plotted in Figs. 12 and 13 respectively as a function of frequency, ranging from 100 Hz to 3 MHz. Note that the 11% decrease in n-channel Idsat and 27% increase in p-channel Idsat remain approximately independent of frequency. The slight downward trend in Idsat values with increasing frequencies is due to the low pass nature of the parasitic capacitances in the circuit. This frequency independence of the parameter shift again indicates

Figure 10: N-channel AC and DC Idsat shifts for different DC stress conditions.

Measurements were made in the reverse direction with 50% duty cycle pulses at a frequency of 100 Hz.

Figure 11: P-channel AC and DC Idsat shifts for different DC stress conditions.

Measurements were made with 50% duty cycle pulses at a frequency of 100 Hz.

Figure 12: N-channel Idsat vs. frequency before (a) and after (a) DC stress.

Stress conditions were Vd=7.5V, Vg=2.0V for 8 days. Measurements were made in the reverse direction with 50% duty cycle pulses.

Figure 13: P-channel Idsat vs. frequency before (●) and after (■) DC stress.

Stress conditions were Vd=-9.0V, Vg=-1.7V for 21 hrs.

that the characteristic time for charge trapping and/or detrapping as affects device performance is short (< 300 ns). Again the higher stress voltages used with p-channel devices resulted in larger Idsat shifts.

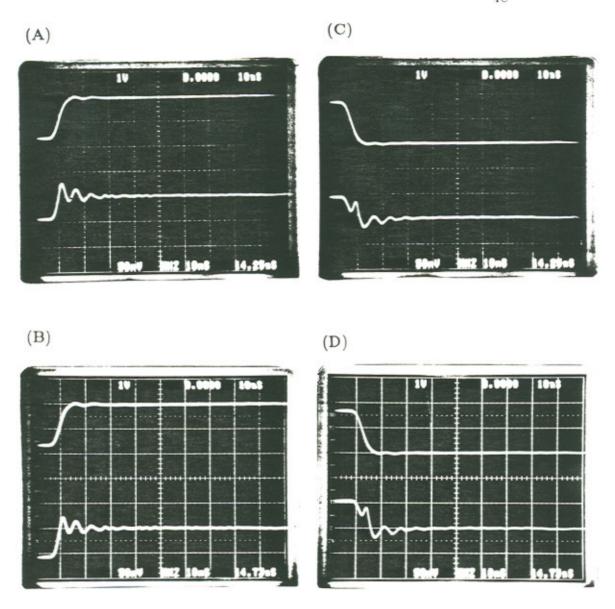

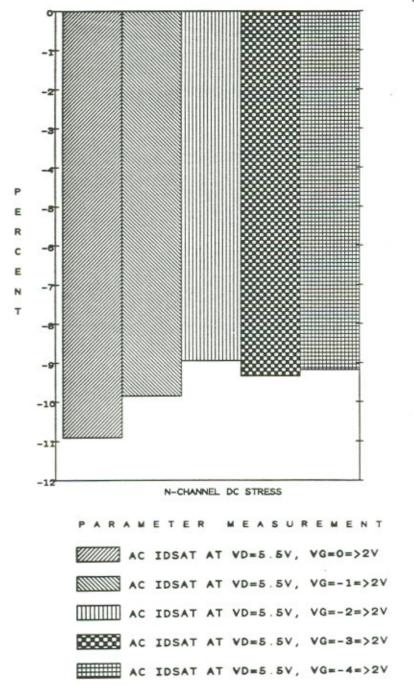

The measurement of Idsat shifts was repeated for different gate voltage base-levels. The surface band bending and concomitant degree of carrier accumulation, trapping or detrapping for a fixed inversion, can be varied by using different gate pulse base-levels. Furthermore, the measurement was carried out at high and low frequencies. In this way, accumulative charge build-up, if any, from incomplete trap emptying in the time between gate pulses, could be observed. Figures 14 and 15 show that changing the base-levels of of the gate voltage do not significantly alter Idsat shifts for either the n- or p-channel transistors. From this one may infer that the stress induced trap level is shallow and that the trap lifetime is shorter than 20 ns. Additionally, the charge trapping or detrapping from deep levels, if any, does not play a significant role in changing Idsat levels.

It is interesting to point out that the parasitic effects associated with AC measurement depend sensitively on the gate base-level used. As can be observed from Figs. 16 and 17, the Idsat shift remains more or less constant at approximately 16% and 30% for n- and p-channel devices respec-

Figure 14: AC measurement of n-channel Idsat shifts for different gate base-levels after DC stress. Stress conditions were Vd=7.5V, Vg=2.5V for 3 days. Measurements were made in the reverse direction with 50% duty cycle pulses at a frequency of 100 Hz.

Figure 15: AC measurement of p-channel Idsat shifts for different gate base-levels after DC stress. Stress conditions were Vd=-10.0V, Vg=-1.7V for 16 hrs. Measurements were made with 50% duty cycle pulses at a frequency of 100 Hz.

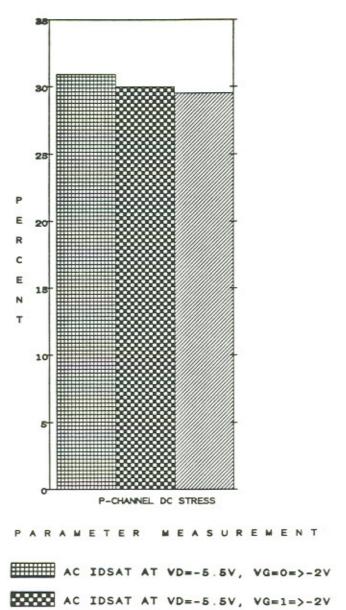

AC IDSAT AT VD=-5.5V, VG=2=>-2V

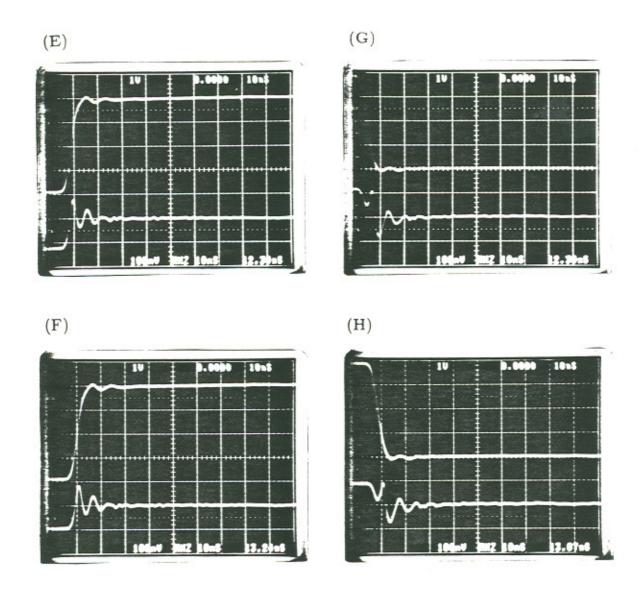

Figure 16: N-channel gate input and load output waveforms; (A),(B) the rising edge measured before and after DC stress with a gate base-level, Vg=-1=>+2V, (C),(D) the respective falling edge, (E),(F) the rising edge measured with a gate base-level, Vg=-3=>+2V, (G),(H) the respective falling edge. Stress conditions were Vd=7.0V, Vg=2.5V for 3 days. Measurements were made in the reverse direction with 50% duty cycle pulses at a frequency of 10 kHz.

Figure 17: P-channel gate input and load output waveforms; (A),(B) the rising edge measured before and after DC stress with a gate base-level, Vg=0=>-2V, (C),(D) the respective falling edge, (E),(F) the rising edge measured with a gate base-level, Vg=+2=>-2V, (G),(H) the respective falling edge. Stress conditions were Vd=-10.0V, Vg=-1.7V for 16 hrs. Measurements were made with 50% duty cycle pulses at a frequency of 10 kHz.

tively. However, waveform overshoot and ringing are more pronounced with increasing base-level magnitude.

## 4.3 Charge Pumping Measurement

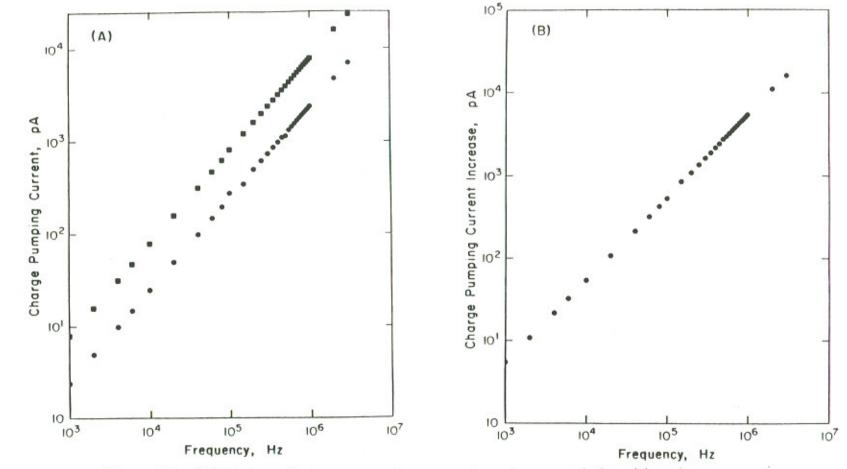

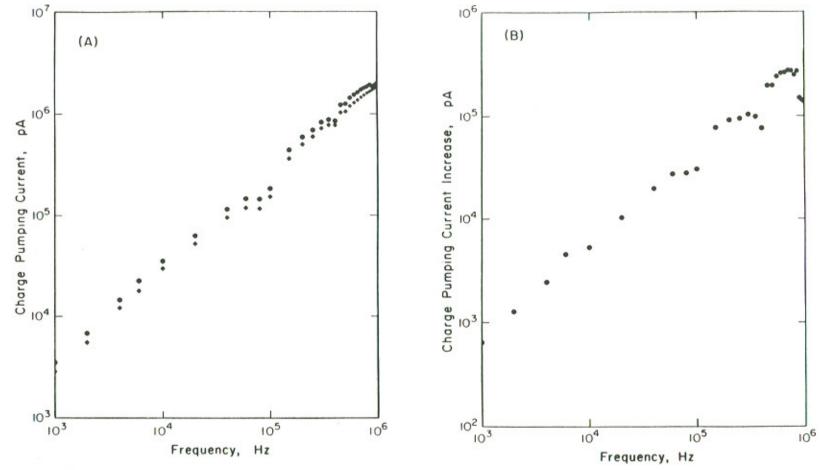

Charge pumping measurements were made before and after DC stress for n- and p-channel devices. Figures 18 and 19 show that charge pumping current increases following stress, in agreement with reported results [14,15]. Figure 18 presents the n-channel pre- and (higher) post-stress charge pumping current, (A) and corresponding difference, (B) as functions of frequency. Figure 19 shows the same data measured from the p-channel case. Note that charge pumping current is significantly increased after stress in both cases. This is experimental evidence that hot carriers damage the interface and generate interface states. The degree of damage is primarily determined by the bias voltages: Vg by controlling the carrier injection rate into the high field region, and Vd by dictating the channel electric field near the drain. Notice also that charge pumping current is proportional to frequency. This can be expected from equations (1) and (2), and from published findings [16,17].

Figure 18: (A) N-channel charge pumping current vs. frequency before (♠) and after (♠) DC stress, (B) the corresponding change in charge pumping current vs. frequency. Stress conditions were Vd=7.5V, Vg=2.5V for 2 days.

Figure 19: (A) P-channel charge pumping current vs. frequency before (•) and after (•) DC stress, (B) the corresponding change in charge pumping current vs. frequency. Stress conditions were Vd=-10V, Vg=-1.7V for 21 hrs.

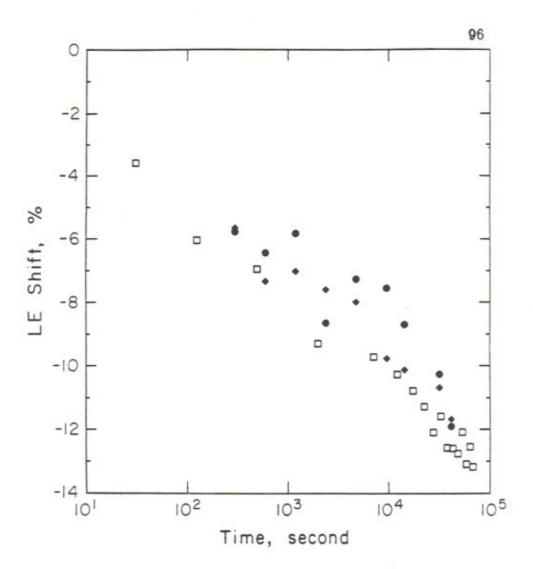

### 4.4 AC vs. DC Stress

The focus of this section is to present the data collected in testing the assumption that AC and DC stresses are equivalent for small time increments. As mentioned in the previous section, AC and DC data under DC stress were found to be the same. Here, the effects of AC and DC stresses are compared in terms of DC parameter measurement.

Devices with the same initial substrate current were evaluated in terms of the following stress conditions: (a) DC drain with DC gate bias, (b) AC drain with DC gate bias and (c) AC gate with DC drain bias. The shifts in Gm and Idsat were examined for n- and p-channel devices.

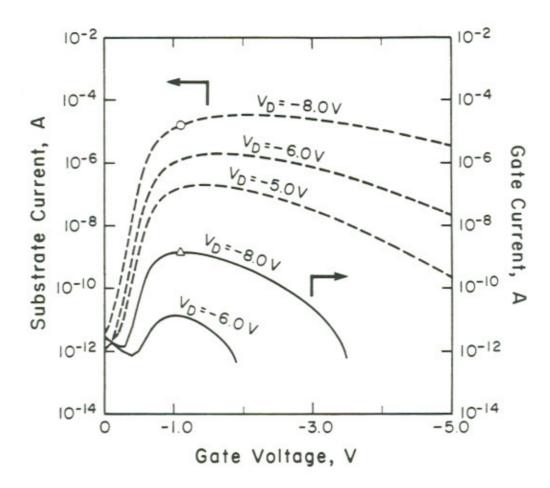

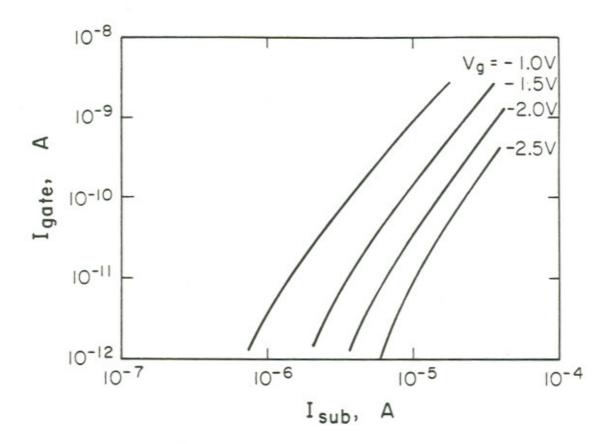

#### 4.4.1 PMOS

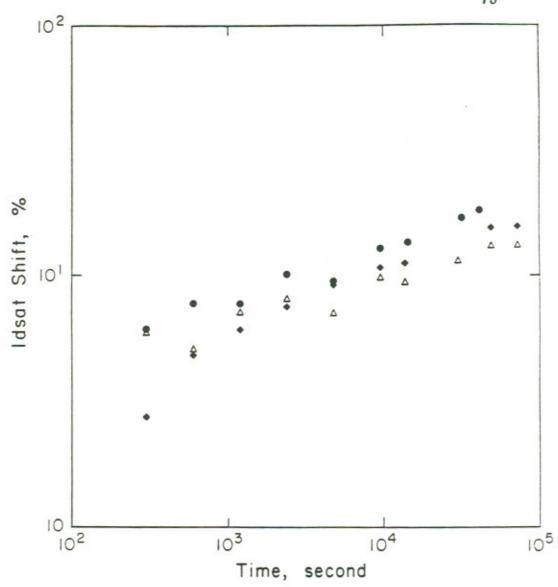

As discussed in the previous chapter, instabilities in p-channel parameters can be significantly enhanced at stress bias conditions that cause peak gate current to flow [18,19]. Figure 20 displays both substrate and gate currents as functions of gate voltage for different Vd's. Note that the peak gate current for a fixed drain voltage (Vd=-8.0V), occurs when Vg≈-1.0V. Devices were tested for the three cases, (a),(b) and (c) near the worst case condition, namely at Vd=-8.0V, Vg=-1.0V and Vd=-8.0V, Vg=-2.0V.

Figure 20: P-channel substrate (---) and gate (---) current vs. gate voltage for different drain voltages.

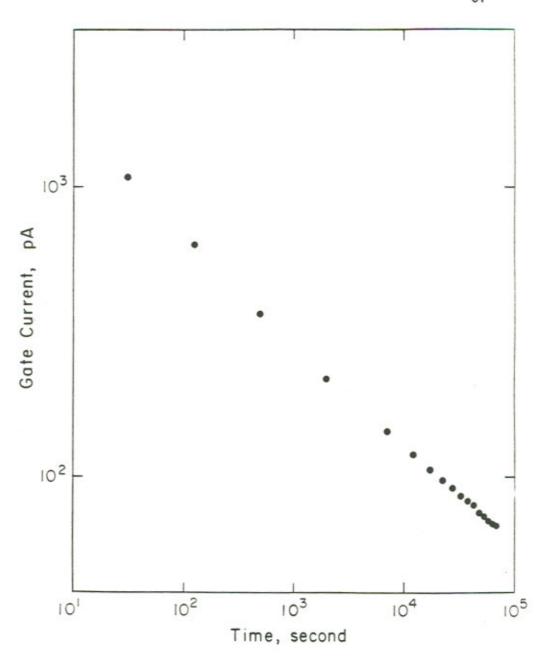

Figure 21 shows typical stress gate current as a function of DC stress time from case (a). Note that it starts at a maximum and monotonically decreases as time increases. This can be qualitatively understood as increased hot electron trapping reducing the channel field near the drain end [20,21].

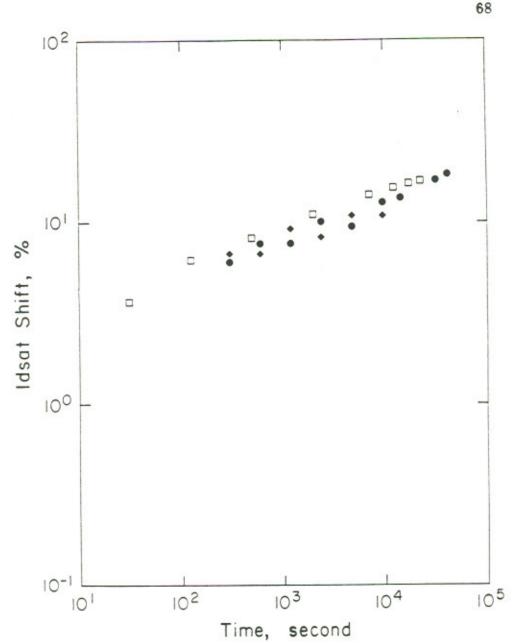

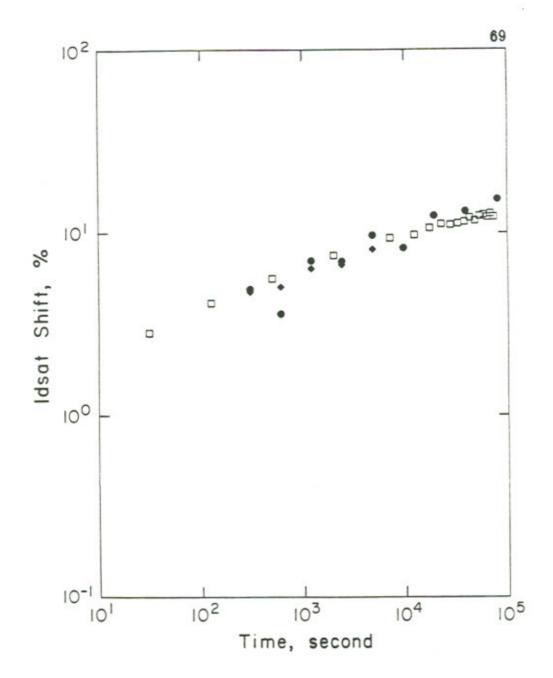

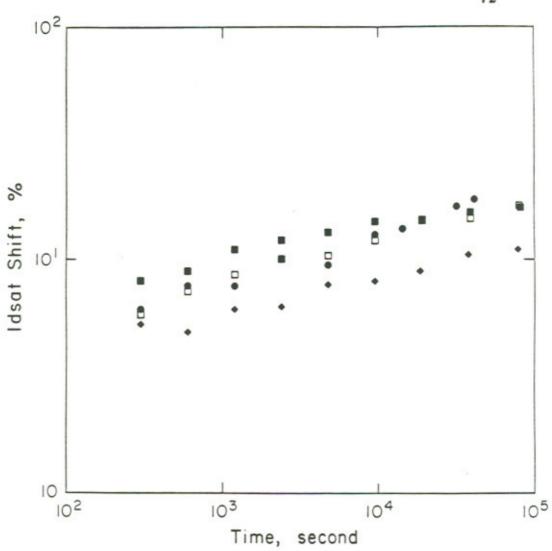

The resulting Idsat shifts measured for the three cases, (a), (b) and (c) near the maximum gate current are plotted as a function of stress time in Fig. 22 (Vd=-8.0V, Vg=-1.0V) and Fig. 23 (Vd=-8.0V, Vg=-2.0V). AC stress time was compared with DC stress time in terms of the active duty cycle pulse 'on time'. Notice that there does not exist a significant difference among these three cases. This implies that near the worst case gate bias, AC gate or AC drain stress result in degradation comparable to the DC case in terms of the active duty cycle. Note also (i) the non-saturating behavior of the Idsat shifts as a function of stress time, and (ii) that the peak gate current (Vg=-1.0V), is consistently associated with higher Idsat shifts.

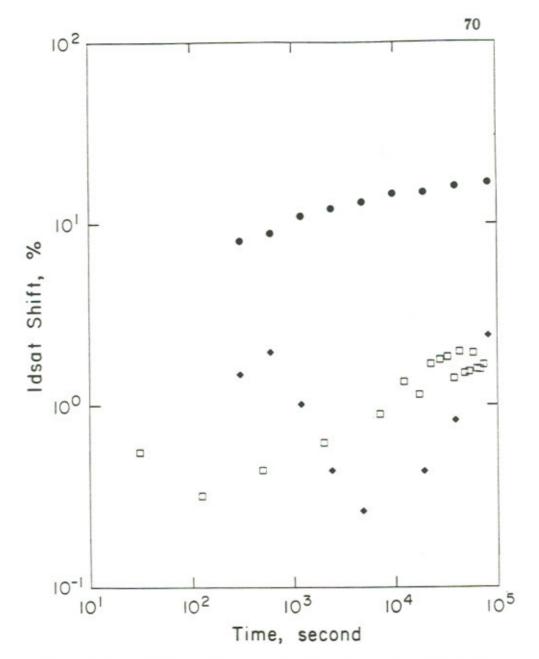

When these three stress cases are compared at a gate bias much higher in magnitude than the worst case, i.e. Vg=-5V, there is a distinct difference in the parameter shifts. As observed in Fig. 24, cases (a) and (b) do not show much shift at all (within the 1% limit of the system

Figure 21: P-channel gate current vs. DC stress time. Stress conditions were Vd=-8.0V, Vg=-1.0V.

Figure 22: P-channel Idsat shifts vs. effective stress time: filled diamonds (♠) represent an AC stress with Vd=-8.0V drain pulse, Vg=-1.0V DC gate bias, filled circles (e) represent an AC stress with Vg=-1.0V gate pulse, Vd=-8.0V DC drain bias and open squares (D) represent a DC stress with Vd=-8.0V, Vg=-1.0V. Stress was applied with 50% duty cycle pulses at a frequency of 10 MHz.

Figure 23: P-channel Idsat shifts vs. effective stress time: filled diamonds (•)

represent an AC stress with Vd=-8.0V drain pulse, Vg=-2.0V DC

gate bias, filled circles (•) represent an AC stress with Vg=-2.0V

gate pulse, Vd=-8.0V DC drain bias and open squares (□) represent

a DC stress with Vd=-8.0V, Vg=-2.0V. Stress was applied with

50% duty cycle pulses at a frequency of 10 MHz.

Figure 24: P-channel Idsat shifts vs. effective stress time: filled diamonds (•)

represent an AC stress with Vd=-8.0V drain pulse, Vg=-5.0V DC

gate bias, filled circles (•) represent an AC stress with Vg=-5.0V

gate pulse, Vd=-8.0V DC drain bias and open squares (□) represent

a DC stress with Vd=-8.0V, Vg=-5.0V. Stress was applied with

50% duty cycle pulses at a frequency of 10 MHz.

resolution). This is in marked contrast with the results of Figs. 22 and 23 where Idsat shifts as much as 10% were observed for (a) and (b). However, unlike (a) and (b), case (c) shows the same non-saturating 10% Idsat shift as in Figs. 22 and 23. To the best of our knowledge, the striking difference observed in case (c) from those of (a) and (b) is reported here for the first time.

Since the AC gate stress resulted in more pronounced Idsat shift, the p-channel degradation behavior was further examined using different gate pulsing conditions. Figure 25 presents the shift in Idsat as a function of stress time for several different gate pulse amplitudes at a fixed off-bias, i.e. Vg=0V. As can be seen from this figure, Idsat shift is essentially the same for all the gate pulse amplitudes used. As mentioned earlier, the maximum degradation in p-channel devices occurs at a gate bias, Vgm causing maximum gate current. Hence, as long as the gate pulse amplitude crosses Vgm, the parameter shift is essentially the same.

Next, the gate voltage amplitude was varied by changing the pulse base-level for a fixed on-bias, i.e. Vg=-1.0V. Figure 26 presents the corresponding Idsat shifts as a function of stress time for different gate pulse base-levels. Again the effect of gate base-level on device degradation is not significant.

Figure 25: P-channel Idsat shifts vs. effective stress time for different gate pulse amplitudes at a common voltage high, (Vg=0V) and a common DC drain bias, Vd=-8.0V: filled circles (a) represent an AC stress with a Vg=-1=>0V gate pulse, open squares (a) with a Vg=-2=>0V gate pulse, filled diamonds (b) with a Vg=-4=>0V gate pulse and filled squares (a) with a Vg=-5=>0V gate pulse. Stress was applied with 50% duty cycle gate pulses at a frequency of 10 MHz.

Figure 26: P-channel Idsat shifts for different gate pulse base-levels at a common voltage low, (Vg=-1.0V) and a common DC drain bias, Vd=-8.0V: filled circles (•) represent an AC stress with a Vg=0=>-1V gate pulse, filled diamonds (•) with a Vg=+1=>-1V gate pulse and open triangles (Δ) with a Vg=+2=>-1V gate pulse. Stress was applied with 50% duty cycle gate pulses at a frequency of 10 MHz.

#### 4.4.2 NMOS

The performance of n-channel transistors was likewise examined under the three stress conditions, (a),(b) and (c). The instabilities in n-channel transistors are sharply peaked at stress bias causing the maximum substrate current [19,20].

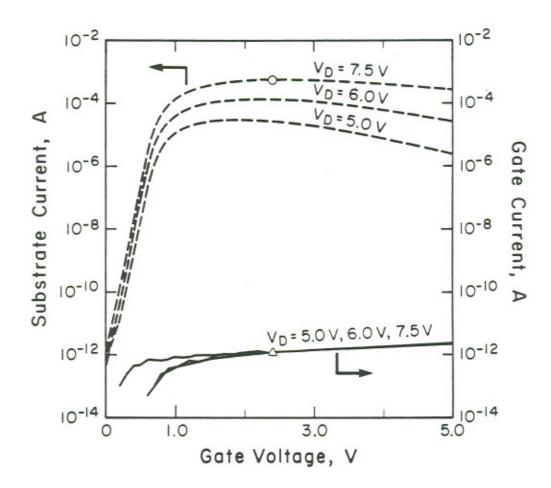

Figure 27 shows both substrate and gate currents as functions of gate voltage for different Vds. The peak substrate current for a fixed drain voltage (Vd=7.5V) is shown to occur when Vg  $\approx$  2.0V. Figure 28 presents the substrate current as a function of DC stress time from case (a). Again the substrate current monotonically decreases as stress time increases.

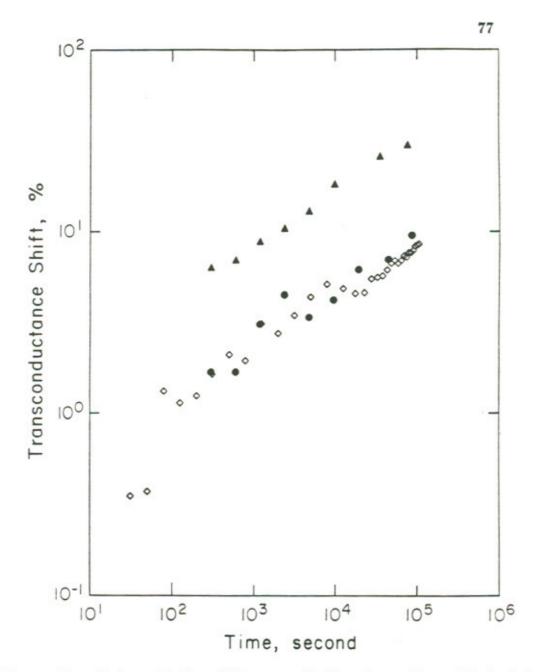

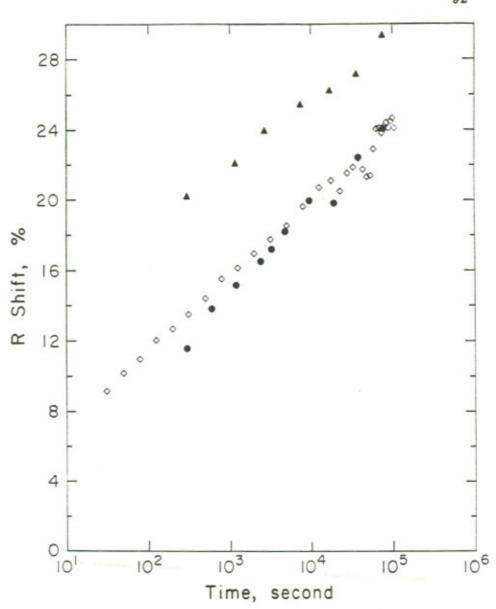

Figure 29 is the n-channel counterpart of the p-channel data presented in Fig. 22. The gate voltage was chosen near the worst case bias, i.e. near Vg=2.0V. The same observed Gm shift for cases (a) and (b) suggests that AC drain stress results in degradation identical to the DC case in terms of the active duty cycle. The gate pulsing stress, case (c) however, gives rise to considerably larger Gm shift for all the examined stress times. This is in marked contrast with the p-channel case (Fig. 22). The work of Cham et al using gate and drain pulse stress on submicron NMOS devices is in agreement with this data [22].

Figure 27: N-channel substrate (---) and gate (---) current vs. gate voltage for different drain voltages.

Figure 28: N-channel substrate current vs. DC stress time. Stress conditions were Vd=7.5V, Vg= 2.0V.

Figure 29: N-channel Gm shifts vs. effective stress time: filled circles (●)

represent an AC stress with Vd=7.5V drain pulse, Vg=2.0V DC

gate bias, filled triangles (▲) represent an AC stress with Vg=2.0V

gate pulse, Vd=7.5V DC drain bias and open diamonds (⋄) represent

a DC stress with Vd=7.5V, Vg=2.0V. Stress was applied with 50%

duty cycle pulses at a frequency of 10 MHz.

Next, attempts were made to compare these cases at a bias much higher than worst case, i.e. Vg=5V. Figure 30 presents the Gm shift for case (a) only. In contrast to the p-channel case, the parameter shift is almost the same as that in Fig. 29. The data for cases (b) and (c) could not be obtained because of repeated device failure via gate burn-out. Devices failed for both case (b) (Vd=7.5V AC, Vg=5.0V DC) and case (c) (Vg=5.0V AC, Vd=7.5V DC).

Figure 30: N-channel Gm shift vs. effective stress time: open diamonds (\$\0) represent a DC stress with Vd=7.5V, Vg=5.0V.

### REFERENCES

- P. Horowitz and W. Hill, The Art of Electronics, Cambridge University Press, New York, 1983.

- N. H. E. Weste and K. Eshraghian, Principles of CMOS VLSI Design, Addison-Wesley Publishing Company, California, 1988.

- S. M. Sze, Physics of Semiconductor Devices, John Wiley and Sons, New York, 1981.

- C. Hu, S. C. Tam, F.-C. Hsu, P. Ko, T. Chan, and K. W. Terrill, "Hot-electron-induced MOSFET degradation- model, monitor, and improvement," IEEE Trans. Electron Devices, vol. ED-32, No. 2, pp. 375-385, 1985.

- F.-C. Hsu and S. Tam, "Relationship between MOSFET degradation and hot-electron-induced interface-state generation," IEEE Electron Device Lett., vol. EDL-5, No. 2, pp.50-52, 1984.

- E. Takeda and N. Suzuki, "An empirical model for device degradation due to hot-carrier injection," IEEE Electron Device Lett., vol. EDL-4, No. 4, pp.111-113, 1983.

- E. Takeda, Y. Nakagome, H. Kume, N. Suzuki, and S. Asai, "Comparison of n-channel and p-channel MOSFET's for VLSIs," IEEE

- Trans. Electron Devices, vol. ED-30, No. 6, pp.675-680, 1983.

- M. Koyanagi, A. G. Lewis, R. A. Martin, T. Huang, and J. Chen, "Hot-electron-induced punchthrough (HEIP) effect in submicrometer PMOSFET's," IEEE Trans. Electron Devices, vol. ED-34, No. 4, pp.839-844, 1987.

- M. P. Brassington and R. R. Razouk, "Relationship between gate bias and hot-carrier induced instabilities in p-channel MOSFETs," Tech. Dig. of the 1987 Symposium on VLSI Technol., pp.55-56, 1987.

- W. Weber and F. Lau, "Hot-carrier induced degradation in submicron p-MOSFET's," IEEE Coloquium on 'Hot Carrier Degradation in Short Channel MOS,' Dig. No. 15, pp.6/1-6/3, 1987.

- C. Lombardi, P. Olivo, B. Ricco, E. Sangiorgi, and M. Vanzi, "Two-dimensional effects in hot-electron modified MOSFETs," IEEE Trans. Electron Devices, vol. ED-30, No. 10, pp.1416-1419, 1983.

- F. Matsuoka, H. Hayashida, K. Hama, Y. Toyoshima, H. Iwai, and K. Malguchi, "Drain avalanche hot hole injection mode on PMOS-FETs," IEDM Tech. Dig., pp.18-21, 1988.

- 13. R. R. Troutman, T. V. Harroun, P. E. Cottrell, and S. N. Chravarti, "Hot-electron design considerations for high-density RAM chips," IEEE Trans. Electron Devices, vol. ED-27, No. 8, pp.1629-1639, 1980.

- 14. P. Heremans, G. Groeseneken, and H. E. Maes, "Study of channel hot carrier degradation in NMOS and PMOS transistors using the charge pumping technique," SISC conference, San Diego, California, 1986.

- 15. R. Bellens, P. Heremans, G. Groeseneken, and H. E. Maes, "A new procedure for lifetime prediction of n-channel MOS-transistors using the charge pumping technique," IRPS Proc., pp.8-14, 1988.

- 16. G. Groeseneken, H. E. Maes, N. Belton, and R. F. DeKeersmaecker, "A reliable approach to charge-pumping measurements in MOS transistors," IEEE Trans. Electron Devices, vol. ED-31, No. 1, pp.42-53, 1984.

- J. S. Brugler and P. G. Jespers, "Charge pumping in MOS devices,"

IEEE Trans. Electron Devices, vol. ED-16, No. 3, pp. 297-302, 1969.

- M. P. Brassington and R. R. Razouk, "The relationship between gate bias and hot-carrier-induced instabilities in buried-and surface-channel PMOSFET's," IEEE Trans. Electron Devices, vol. 35, No. 3, pp.320-324, 1988.

- 19. M. Koyanagi, A. G. Lewis, R. A. Martin, T. Huang, and J. Chen, "Hot electron induced punchthrough in submicron PMOSFETs," Extended Abstr. of the 18th Conf. Solid State Devices and Mater.,

(Tokoyo, Japan), pp.475-478, 1986.

- R. Bellens, P. Heremans, G. Groeseneken, and H. E. Maes, "Characterization and analysis of hot-carrier degradation in p-channel transistors using constant current stress experiments," Solid State Devices, pp.261-264, 1988.

- C. Yao, J. Tzou, R. Cheung, and H. Chan, "Structure and frequency of hot-carrier-induced degradation in CMOS VLSI," IRPS Proc., pp.195-200, 1987.

- K. M. Cham, H. Fu, and Y. Nishi, "The dependence of hot carrier degradation on A.C. stress waveforms," IEDM Tech. Dig., pp.30-33, 1988.

#### CHAPTER 5

### INTERPRETATION AND DISCUSSION

In this section the physical processes associated with stress induced degradation will be highlighted. First a general discussion of the physics behind the hot carrier phenomenon will be briefly summarized. Following this, the specific hot carrier effects as applied to the data presented in this thesis will be discussed.

### 5.1 General Discussion

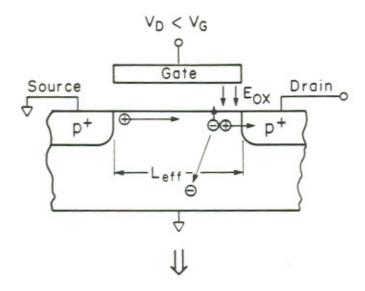

As mentioned in the introduction, there is a general consensus that the driving force behind all hot carrier effects is the large electric field induced at the drain end of short channel devices. In the presence of a high field, a carrier can gain enough kinetic energy that upon collision with an atom, it can break lattice bonds and create an electron-hole pair. This is illustrated schematically for the case of the n-channel device in Fig. 31.

The stress enhanced substrate current is a direct consequence of hot carrier effects. The substrate current can be phenomenologically expressed as,

Isub

$$\propto$$

Id  $\cdot \exp(-Qi/q\lambda Em)$  (7)

## N-Channel Hot Carrier Effects

# Hot Carrier Injection and Impact Ionization

# Resulting Device Degradation

Figure 31: N-channel hot carrier induced degradation model.

where Id is the drain current, Qi the minimum energy for impact ionization, q the electronic charge,  $\lambda$  the carrier mean free path and Em the maximum channel electric field [1-4]. The substrate current is determined by two factors, first Id, a measure of the number of carriers injected into the high field region, and second, the exponential term representing the probability that the hot carrier gains sufficient energy to give rise to impact ionization. As the electric field, Em is increased, Isub exponentially grows.

The failure mechanism in devices involves two steps: (i) a high field giving rise to hot carriers, and (ii) the injection and/or trapping of these hot carriers in the oxide/interface region. An important consequence of this is the formation of interface states or traps. Interface trap generation therefore can be empirically modeled as,

$$\Delta Nit \propto \left[ \frac{t \cdot Id}{W} \cdot \exp(-Qit/q\lambda Em) \right]^n$$

(8)

where  $\Delta$ Nit is the generated interface trap density, t the stress time, W the channel width, Qit the critical energy required to create an interface trap and n an empirical fitting parameter [1,4].

Interface state generation also is comprised of two factors; the total number of carriers spilling into the high field region during the stress time t, t·Id/W and the probability to create an interface trap.

Charge pumping current, Icp is a monitor of interface state generation. The current can be correlated to Nit as,

$$Icp \propto q \cdot f \cdot A \cdot Nit \cdot \Delta E$$

(9)

where f is the pulse frequency, A the effective gate area and  $\Delta E$  the interface state energy range [4-7]. Charge pumping current can, in essence, be interpretated as being due to the carriers which are detrapped from the interface states via the gate bias. Thus an increase in interface state density due to stress will be accordingly reflected in an increase in charge pumping current [8].

The physical damages introduced by hot carriers are not only reflected in interface trap generation, but also in shifts in such device electrical parameters as Gm, Vt, Idsat and S. The stress induced parameter shift in the normalized subthreshold swing, S/So is related to the shift in the normalized interface state generation, Nit/Nito as,

$$\frac{\Delta S}{So} \propto \frac{\Delta Nit}{Nito} \cdot \frac{Csso}{Cox + Cd + Csso}$$

(10)

where So is the initial subthreshold swing, Nito the initial interface state density, Csso the initial surface state capacitance. Cox the gate oxide capacitance and Cd the depletion region capacitance [9].

### 5.2 DC Stress and DC Characterization

The data presented in this thesis are now discussed. Charge pumping current measurements before and after stress (Figs. 18 and 19) show that indeed interface states are generated as a result of stress for both n- and p-channel devices. For both the cases, Nit is approximately proportional to stress time for all frequencies used for measurement, i.e. the empirical factor in Eq. (8) is approximately one.

For PMOS, both substrate and gate current exhibit pronounced peak as a function of gate voltage (Fig. 20). This trend can be understood with the use of Eq. (7) in conjunction with the electric field distribution in the channel. For a fixed Vd in the leakage region of device operation, most of the drain voltage is dropped across the reverse-biased p-n junction region at the drain end. The field is therefore highly localized and Em at the drain end is large. This field configuration remains more or less the same throughout the subthreshold region.

With the onset of channel formation, Em is still high since the device is saturated. With increasing Vg, the device enters into the linear region, and Em will be rapidly reduced. In the leakage and subthreshold regions, Em will remain essentially flat and the impact ionization rate is constant. At fixed Vd, the drain current exponentially increases with increasing Vg in the subthreshold region. Thus, the resulting electron flux into the high field region gives rise to the rapid increase in substrate current.

For Vg > Vt, Id increases according to the power law Vg (linear region) or Vg<sup>2</sup> (saturation region). Simultaneously, Em decreases slightly for the reasons discussed in [10]. The effect of the slight decrease in Em is exponentially amplified (Eq. (7)). Hence, the decrease in probability for impact ionization outweighs the increase in Id, and Isub should fall with increasing Vg. Therefore, Isub will be peaked at an appropriate Vg value. One can understand the substrate current data obtained from the NMOS (Fig. 27) in the same manner.

The behavior of Ig (Fig. 20) can also be understood in a similar manner. Here Isub can be viewed as a source for generating Ig. The same electron, if pulled toward the substrate, constitutes Isub. For the later process, however, the electron can further induce impact ionization, making more carriers available for Isub and Ig. This point was further examined experimentally by measuring Ig and Isub simultaneously. Figure 32 presents Ig vs. Isub plots for several PMOS gate voltages. Clearly, Ig is seen to follow the square law with respect to Isub, viz.

$$Ig = C \cdot Isub^{2} \tag{11}$$

Here, the proportionality constant, C is found to be independent of

Figure 32: P-channel gate current vs. substrate current for different gate biases with Vd varied from -5.0V to -8.0V.

temperature, but is weakly dependent on Vg. The data presented in Figs. 20 and 32 are consistent with each other. According to Eqs. (7) and (11), Ig is more sensitively dependent on Em than Isub. That is, the peak of Ig should be shifted to the left of the Vg axis from the corresponding Isub-peaks, which is in agreement with the data.

Next, the device parameter shift measured under DC conditions following stress is discussed. For the NMOS, Idsat and Gm decrease due to stress. The Vt-shift is insignificant because Vt is measured with a small Vd bias. The decrease in Idsat and Gm is an indication that the effective channel mobility has decreased, series resistance has increased or the combination thereof. Figure 33 shows that the extracted series resistance does indeed increase with stress time with both DC and AC stress time. The observed transconductance, Gm(obs) depends on the series resistance at the source (Rs) according to

$$Gm(obs) = \frac{Gm}{1 + Rs \cdot Gm}$$

(12)

where Gm is the true transconductance [11]. The monotonic increase in S as a function of stress time is consistent with the monotonic increase in Nit with stress time (Eq. (8)).

Next consider the change in parameter shift as measured in forward

Figure 33: N-channel series resistance vs. effective stress time: filled circles (●)

represent an AC stress with Vd=7.5V drain pulse, Vg=2.0V DC

gate bias, filled triangles (▲) represent an AC stress with Vg=2.0V

gate pulse, Vd=7.5V DC drain bias and open diamonds (⋄) represent

a DC stress with Vd=7.5V, Vg=2.0V. Stress was applied with 50%