# A REAL-TIME SOFTWARE PERFORMANCE ANALYSIS CHIP

Mehul S. Dave B.E., University of Bombay, India, 1987

A thesis submitted to the faculty of the Oregon Graduate Institute of Science and Technology in partial fulfillment of the requirements for the degree Master of Science in Electrical Engineering

September, 1990

The thesis "A Real Time Software Performance Analysis Chip" by Mehul S. Dave has been examined and approved by the following Examination Committee:

> Charles L. Saxe, Thesis Advisor, Tektronix Inc.

Dr. John Murray Associate Professor, Department of Electrical and Computer Engineering, Oregon State University, Corvallis, OR

Dr. V. S. Rao Gudimetla Assistant Professor, Department of Applied Physics and Electrical Engineering, Oregon Graduate Institute of Science and Technology

Dr. Raj Solanki Associate Professor Department of Applied Physics and Electrical Engineering, Oregon Graduate Institute of Science and Technology

#### ACKNOWLEDGMENTS

I would like to thank several people without whose help this project would not have been possible. My thanks to Dr. V. S. Rao Gudimetla who got the project for me and who was extremely supportive all through the project. I am also thankful to Dr. Paul Davis for supporting this project and to Dr. John Murray and Dr. Raj Solanki for agreeing to examine this thesis.

Special thanks are due to my thesis advisor, Chuck Saxe. He provided valuable guidance throughout the project and taught me many things. Without his guidance and support, this project would not have been possible. My thanks to all the members of the Advanced Development Group (ADG) at Tektronix. In particular, thanks to Craig Overhage for suggesting this project and his help with critical path analysis using the fastta timing analyzer. Thanks to Dave McKinney for designing new standard cells almost on demand and for giving extremely helpful suggestions about the design of the chip. Finally, I am thankful to Tektronix Inc. for funding this project.

# Table of Contents

| Abstract |               |                                                             |    |  |  |

|----------|---------------|-------------------------------------------------------------|----|--|--|

| 1.       | Introduction  |                                                             |    |  |  |

| 2.       | 2. Background |                                                             |    |  |  |

|          | 2.1           | Need for testing and performance analysis of software       | 3  |  |  |

|          | 2.2           | Types of testing                                            | 5  |  |  |

|          | 2.3           | Real time needs and traditional methods of testing and per- |    |  |  |

|          | form          | ance analysis                                               | 6  |  |  |

|          | 2.4           | Progress toward comprehensive real-time testing techniques  |    |  |  |

|          | tools         | 9                                                           |    |  |  |

| 3.       | Macro         | architecture of the chip                                    | 14 |  |  |

|          | 3.1           | Goals of this project                                       | 14 |  |  |

|          | 3.2           | Discussion of possible architectures                        | 16 |  |  |

|          | 3.3           | Description of macroarchitecture of the chip                | 20 |  |  |

| 4.       | Microa        | architecture of the chip                                    | 25 |  |  |

|          | 4.1           | Introduction                                                | 25 |  |  |

|          | 4.2           | Global view of the microarchitecture                        | 26 |  |  |

|          |               | 4.2.1 The Processing Section                                | 26 |  |  |

|          |               | 4.2.2 The Input Section                                     | 30 |  |  |

|          |               | 4.2.3 The Output Section                                    | 33 |  |  |

|          | 4.3           | The Range Recognizer Circuit                                | 35 |  |  |

| 4.4       | The Priority Resolver Circuit | 41  |

|-----------|-------------------------------|-----|

| 4.5       | The RAM circuit               | 44  |

| 4.6       | Results and discussion        | 49  |

| 5. Sumn   | nary and conclusions          | 59  |

| Reference | S                             | 61  |

| Appendix  | Α                             | 63  |

| Appendix  | В                             | 67  |

| Appendix  | C                             | 74  |

| Appendix  | D                             | 104 |

v

# List of Figures

| Figure 1 |        | 27 |

|----------|--------|----|

| Figure 2 | 5<br>  | 36 |

| Figure 3 | ······ | 42 |

| Figure 4 |        | 45 |

#### ABSTRACT

#### A REAL TIME SOFTWARE PERFORMANCE ANALYSIS CHIP

Mehul S. Dave, M.S.

Oregon Graduate Institute of Science and Technology, 1990

Supervising Professor: Charles L. Saxe

An essential stage in software development is debugging the code and checking it for correctness. Another related stage is performance analysis of the developed software which involves making sure that the program in question runs at the optimal speed required for a particular application.

In many real time applications, fast and efficient code is needed. However, the techniques and tools for the debugging and performance analysis of real time software are still, by and large, primitive and have not kept pace with the advances in software technology. Traditional hardware tools such as logic and state analyzers are useful only at the machine language or assembly language level. Software based performance analysis tools such as program profilers interfere with the real time behavior of the program by inserting additional code and thus do not provide accurate information. A tool to perform non-intrusive performance analysis at the source level for programs written in high level languages is needed. In this thesis, the design and implementation of a CMOS chip to aid high level non-intrusive performance analysis is reported.

### 1. INTRODUCTION

The testing and validation of programs has received considerable amount of attention in the past decade. With the increasing availability and use of high level languages, the programmer has moved increasingly away from the low level machine details and more complex abstractions can now be implemented with ease. With the increasing complexity of programming projects, the need for testing and debugging the code becomes even more crucial. To handle the increasing complexity, the tools for debugging and testing also must become more sophisticated.

Very often, it is not only necessary to test the program for correctness but also performance. There are programs that may run correctly i.e they may perform the necessary function but execute too slowly. This has sometimes been called a "performance bug".<sup>1</sup> It would be desirable to do some performance analysis of such a program to improve its running time. In real time systems, it is often mandatory to make such improvements. Consider, for example, a mechanical arm in an assembly line that moves at fixed intervals of time. The software driving the arm must be capable of finishing its task within this interval. A tool to facilitate performance analysis of such software would be extremely helpful to programmers. However, there are very few tools available to facilitate the real time programmer in testing and debugging. As Robert Glass puts it,<sup>2</sup> the world of debugging and testing of real time software is a "lost world".

The techniques and tools available to the programmer of real time systems have not kept pace with the advances in software. A typical real time program is still tested at the machine language or the assembly level. Traditional tools such as logic and state analyzers help the programmer in debugging at the machine language or assembly language level but are not useful to do performance analysis at the high level in which programs are typically written. Software tools such as profilers, where available, are not useful for real time systems since they are intrusive by nature and thus do not give accurate measure of the timing of some sections of the code.

In this thesis, I will discuss the design and implementation of a CMOS chip which is intended to be a hardware tool for non-intrusive real time performance analysis and which can be used at high level with proper software. Chapter 2 presents the history and background of software testing and performance analysis. Some other tools developed for non-intrusive performance analysis and related work are also discussed.

In chapter 3, the macroarchitecture of the chip is discussed. Various modes and features of the chip and the reasons for choosing a certain architecture instead of other possible architectures is discussed.

Chapter 4 discussed the microarchitecture and the logic level details of the chip. The results of simulation using the Tektronix ADG standard cell library are presented. The final layout of the chip and the simulation after the layout are also presented.

Discussion of results, conclusions and suggestions for further research are presented in chapter 5.

#### 2. BACKGROUND

# 2.1 Need for testing and performance analysis of software

The need to test software is obvious. The program should be able to implement the function that it is designed to implement. Since any program of a reasonable size can, and almost always does have bugs, one needs to test the programs for their correctness. The amount, scope and methods of testing of programs may vary depending upon several factors such as the nature of the application, the resources available to the software developer, ease with which testing can be done etc. However, at the very least, functional testing of a program must be done, i.e. it must be made certain that the program implements the required function correctly and that there are no bugs in the program. Detection and elimination of redundant code, unused variables, bad programming constructs, incorrect logic, rare conditions which can lead to bugs and optimizing code for performance etc. are among the goals of testing to develop more reliable software. Bug free code is always desirable and a little time invested in testing can uncover sources of potential later disasters.

The level of testing done depends on several factors such as the nature of the programs, the tools available, the cost, the nature of the application etc. In certain cases, extensive testing must be done to make certain that no bugs are left in the code because the costs of errors, both tangible and intangible can be enormous. Consider, for example, programs for missile control or control of equipment in a nuclear power plant. In other, less critical applications, such as for example, payroll processing, the standards for testing and optimization may not be as strict as the former case because

such standards are not needed and neither are they economically viable. The amount of testing done is also largely dependent on the ease of testing. If sophisticated tools are available to enable fast, easy, efficient, comprehensive and cost effective testing, the programmer will devote more time to testing since bug free code is always desirable. On the other hand, in absence of such tools, only as much of testing as is absolutely necessary, will be done. It is clear, however, that irrespective of the level of testing done, it is almost mandatory to perform some testing on programs.

The increasing complexity of software emphasizes the need for testing even more. As software has evolved from the machine language to assembly language to finally the high level languages of today, the programmer is increasingly shielded from the low level machine details. It is now possible to implement increasingly complex abstractions much more easily by using sophisticated compiler technology. Software written using such languages can thus perform functions far more complex and far wider in scope than before. This also means, however, that the bugs in such software are more difficult to uncover and that the likelihood of having bugs is increased because several layers of software lie between the programmer and the hardware. Therefore not only are more sophisticated tools for debugging needed but also more extensive testing of code is needed. The tool for testing or performance analysis has to interpret the low machine level events and pass through several layers of abstractions to output data at the source level. Thus, tools with greater functionality and more sophistication are needed.

While it is true that unlike debugging, it is not necessary to do performance analysis in all cases, in many applications it is desirable and even mandatory to undertake performance analysis. Real time applications are a very good example. Real time software is constrained by latencies between events. The software must complete its task in the time between inter-event latencies. It is often the case that while the software implements the required function, it runs too slowly and may be unacceptable for a real time application. In such a case, performance analysis of such software is necessary to ascertain which areas of the code need improvement. Even in case of batch processing, if the programs run for a long period of time, it would be desirable to analyze the program to discover the performance bottlenecks and correct them so that the program executes faster. Thus performance analysis of code is also a crucial part of testing for several applications.

#### 2.2 Types of testing

Considerable attention has been directed in the last decade to the subject of testing and reliability of software. A lot of literature has been published on the subject (see, for instance<sup>3-5</sup>). Tools such as static analyzers, program provers, profilers and source level debuggers are more widely available. The testing techniques may be broadly classified as *static testing* and *dynamic testing*. In static testing, the source code is run through a program which analyzes the code for certain errors that can be detected solely by looking at the text of the program. Such a tool can identify such errors as incorrect data constructs, uninitialized variables, unreachable code, nonportable code etc. An example of such a tool is *Lint*6 for the C programming language. In dynamic testing, the program is executed in a controlled manner so as to test that the required functions execute correctly. This generally involves giving the program a set of predetermined inputs and observing the output.

As discussed previously, several times it may be the case that the program in question executes correctly but it executes too slow for the task at hand. Performance analysis of the program needs to be done for such a case to determine in which part of the code does the program spend most of its time. The efforts may then be directed at this part of the code to make it more efficient by rewriting it. Program profilers are the tools designed to facilitate performance analysis of a program. Typically, a program profiler inserts counters at critical nodes in the code and the counters are incremented dynamically when that part of the code is reached. Then, based on the available count and a statistical sampling of the program counter during the execution of the program, the profiler gives the data about which part of the code is most frequently used. The gprof<sup>7</sup> profiler on UNIX<sup>†</sup> operating system is an example of such a tool.

The tools for testing and performance analysis may be hardware or software tools. Programs such as static analyzers and program profilers are software tools. On the other hand, one can use hardware tools such as logic analyzers, state analyzers and in-circuit simulators also as tools for testing and performance analysis. Such hardware tools most often monitor the signals at the pins of the microprocessor or the bus and when a certain combination of signals is detected, they start taking the data till a certain point of time. They also may be time triggered i.e. at regular intervals of time, they interrupt the microprocessor for a brief period and acquire data and store it for later analysis.

2.3 Real time needs and traditional methods of testing and performance analysis

requirements and the limitations imposed by its environment. A discussion of these follows.

Real time software is software running on a computer that interacts with functioning external devices. It is called real-time because the software actions control activities that are occurring in an ongoing process.<sup>2</sup> The task of developing reliable real time software is particularly more difficult for several reasons. Most of the times, such a software is part of a larger system (sometimes also called embedded systems) and must interact with several different devices often functioning asynchronously. In contrast with the traditional computer systems, such systems do not have the sophisticated supporting software such as complex operating systems, debuggers, program profilers and other utility programs. In fact, in most of the systems, the hardware is cheap, light and small due to economic reasons. Consider, for example, a computer driving a missile system. It is a throw away piece of hardware and it is therefore necessary to make it as cheap as possible. This results in complexity being transferred from hardware to software. It is also desirable to transfer complexity from hardware to software since multiple copies of software do not cost much but every additional copy of hardware costs. Also, many times due to the nature of environment in which a real time system operates such as excessive heat or moisture, it is not possible to use complex hardware which requires more stable environmental conditions. So the function must be taken care of by software again. To add to this already bad picture, real time software is constrained by latencies between events. The software must be able to complete its task within the time between interevent latencies. So the real time software developer has to develop more powerful software in a more primitive environment.

Given these conditions, it follows that a tool to facilitate debugging and performance analysis which is geared towards real-time environments would be extremely valuable to the real-time developer. Most of the traditional tools for testing and debugging are, however, not geared for the real-time environment. Static performance analyzers are not too useful because most of the software developed for realtime applications is developed in a host-target environment. The program is developed on the host, a more powerful and more sophisticated computer and then cross-compiled for the real-time environment. The static analyzer can be useful in the host environment and it will eliminate certain bugs but it is not enough.

Program profilers are not useful since they are intrusive by nature. They add some additional code to ascertain the real-time behavior of the program and thus provide an inaccurate measure of the timing. They often intrude to the point where the distortion is significant and thus the tool loses its effectiveness. Also, in several applications such as embedded systems for instance, it may not be possible to insert additional code into the real-time program. In such systems, the program is hard coded and thus introduction of any additional piece of code is impossible. Also, such a tool will often miss some crucial event which occurs rarely and is a source of a bug. The program profilers also obtain their data on timing by sampling the location of the program counter. This technique is inherently statistical in nature and thus several runs of the program may be necessary before the accumulated data reaches as acceptable level of confidence.

Hardware tools are most commonly used for real-time debugging and testing. Tools such as logic and state analyzers, in circuit simulators etc. are very useful for debugging of real-time programs. These tools observe the signals at the pins of the microprocessor or the bus and acquire the data when a particular sequence of events is observed. Some of these tools use an interrupt technique based on event triggering. The tool interrupts the microprocessor when it detects a predefined event and acquires data and stores it for later analysis. Such a technique, by its nature is intrusive and is not suited for performance analysis. Other tools start data acquisition by storing some signals on the bus when they detect a particular event and stop the acquisition after a period of time. This technique is not intrusive but since the amount of data to be stored is so much, typically the tool can only save the activity for a few milliseconds. When its buffer is exhausted, it cannot store any data any longer. Such a tool is not useful for observing the behavior of the program for extended periods of time.

The most serious limitation of traditional hardware tools, however, is that they cannot display the results of the program at the source level. Typically, they give data either in terms of machine language level or assembly level. This is a very serious limitation. The programmer, thus, has to be knowledgeable about assembly language and other low level details of the system he is working on. Thus more training effort has to be expended. And more importantly, since the low level machine details differ from one system to another, the training effort has to be expended for every new system. Moreover, debugging the program at assembly level is more difficult and time consuming. This combined with the fact that in real time systems, programmers typically have to deal with additional complexity transferred from hardware makes it clear that a tool which affords source level analysis of real-time software is required.

#### 2.4 Progress toward comprehensive real-time testing techniques and tools

There have been a few attempts to develop tools and techniques particularly suited for real-time applications. There have even been attempts at a systematic study of the field and formalization.<sup>8</sup> Some of the tools reported were developed exclusively for some particular system <sup>9,10</sup> and while these make important observations, they are not helpful for systems other than those for which they are designed. There were also some early attempts which suggested hardware support for debugging and testing but these did not strictly deal with the subject of real-time testing but rather with other related subjects such as multiprogramming environments.<sup>11</sup>

Many of the other tools developed focussed on the problem of debugging and testing and proposed having large buffers to store all the activity of the program from a certain point and then try to reconstruct the program to trace back to the point where the error occurred.<sup>10, 12</sup> Such tools are suited more for the task of debugging and not for performance analysis and they also propose storage of large amount of data, quite a bit of which may be useless. Besides, the problem of being able to store only limited amount of data due to limited size of buffer remains and these tools, therefore cannot be used for programs which execute for long time. The tools also require a reconstruction of the program after its execution and it may not be easy to accomplish this in all cases and the effort required to develop the software to reconstruct the program from the stored data is quite large.

There are other tools proposed<sup>13</sup> which are of more interest since they propose real time monitoring of the program and storing only the essential data. Plattner<sup>14</sup> proposes a tool to facilitate real time monitoring of programs and develops means to specify actions to be taken by the monitoring program based on predicates formed on the text of the source program. He describes, in detail, an elaborate hardware scheme to accomplish this objective and reports the development of a prototype. A similar tool is reported by Bemmerl.<sup>15</sup>

The main advantage of these tools is that they afford real-time analysis at the *source level*. This is a significant improvement over other methods proposed. It is also an attempt to bring the tools for debugging and testing up to date with the advances in software technology. Such a tool would be of great help to a real-time software developer particularly if working in host-target environment where the software is written in a high level language on a host and cross compiled for the target. However, there are some disadvantages. Most significantly, the disadvantage is the limited capability of the tool. For instance, in the prototype implemented by Plattner, only 10 monitoring actions can be specified for a single run of the program.

This limitation overshadows most of the advantages of the tool. The tool offers a variety of functions. Any sort of monitoring function can be specified to aid debugging. One can keep track of changes in values of a particular variable, trace execution of a set of statements, set counters based on conditions etc. But only 10 of such actions can be executed for one run of the program. So, most of the capabilities of the tool which make it potentially useful for real-time applications are rendered useless since only a few can be used at a time.

There has been progress made even in logic and state analyzers.<sup>16</sup> The state analyzers have become more sophisticated. Tools such as microprocessor analyzers can be used to interpret the activities on the pins of a specific microprocessor and relate these signals to high level events. However, these are microprocessor specific and not useful in general for several systems. Hewlett-Packard's HP 64340A software analyzer is another hardware tool to aid software analysis.<sup>17</sup> The tool helps the analysis of software at high-level. The disadvantage of this tool, like Plattner's, is that the tool has limited capability. It can only monitor four ranges of code for a given run of the program.

Another tool recently reported overcomes several of the disadvantages of the tools mentioned above. *Softanalyst* by Northwest Instruments Inc., offers the capability to do non-intrusive source level performance analysis in real-time.<sup>18-21</sup> The tool offers several capabilities. The symbolic trace option lets the user keep a trace of the order of program execution and trace individual statements. Performance analysis mode lets the user time up to 80 ranges of code and the code coverage option keeps a track of which statements of the program were executed in a single run. The significant feature of the tool is that it allows the user to observe the performance of the program at source level. By looking at the symbolic table generated by the compiler, the tool relates the software events such as entry into a procedure and exit from it or activity of a particular variable etc. to their hardware equivalents. The tool gath-

ers the data, processes it and displays the results back in terms of source level constructs. It has many more ranges than the other tools and unlike logic analyzers, it can gather execution data for the programs having execution time of the order of seconds rather than the typical milliseconds for logic analyzers.

Softanalyst represents a significant advance in non-intrusive, real-time, sourcelevel performance analysis. However, in spite of its wider capabilities and resources, it is often not extremely useful. The timing of code is the important capability offered by it. But owing to the architecture of the tool, it can only store data for programs whose execution time is of the order of seconds. After that, its buffer overflows and it can no longer gather data. It also requires a relatively complex front-end probe for each specific microprocessor which can provide it the necessary signals to detect the occurrence of hardware events. The Softanalyst is event-triggered. It detects the occurrence of up to 256 events on the bus and then starts its timing when the occurrence of the event is detected and stops when another event is detected. This presents some problems for timing of code. Firstly, this means that one cannot satisfactorily time procedures with multiple entries and exits. Secondly, it becomes difficult for it to account for occurrence of interrupts and it is also difficult to use for multi user systems.

It should be observed that in all the previous efforts to develop a tool for debugging and performance analysis, the main bottleneck was the limitation of resources of the tool. Most tools offer very advanced capabilities but only a few of them can be used at a particular time. The goal of the designers of the system was to offer a tool which can handle several different tasks. This increased the complexity of the job and resources were limited because each different task consumes away a part of the limited resources available. In my opinion, it would be better to concentrate the resources on a particular task rather than to divide them among several tasks. One can design a small but efficient tool which would handle a particular task such as performance analysis and leave tasks such as debugging to other tools. A system can then be constructed out of several different components, each dedicated to a particular task. This would achieve a more efficient utilization of resources and better capabilities for each particular task. The next chapter discusses the goals of this project with this perspective and the macroarchitecture of the chip.

#### 3. MACROARCHITECTURE OF THE CHIP

#### 3.1 Goals of this project

The goal of this project was to develop a very cheap and effective way to do performance analysis. We wanted to develop a tool which can time the execution of code for extended periods of time and which uses relatively simple circuitry interfacing with the system bus to detect events. Since this tool was to be used for nonintrusive analysis in real time, it could not be implemented software. A part of it would have to be hardware which, in turn, is driven by software. We decided to try to implement a chip which can allow a user to monitor several ranges of the program and gather performance analysis data and store it in on-chip memory which can later be read off by appropriate software. This thesis discusses only the chip. The software to run the chip has not yet been developed.

As discussed in the previous chapter, the problem with most tools was that the number of ranges which could be simultaneously monitored for gathering performance analysis data, was too small. One of the goals of the project was to try to overcome this limitation. The available chip area would constrain this number. But if one could implement a relatively simple design so that each chip would be very cheap, one could use several chips for a system and thus provide a large number of ranges capable of collecting data for extended periods of time which can be used for performance analysis purposes. These chips used in conjunction with a state or a logic analyzer would make a very effective tool for non-intrusive debugging and performance analysis.

There was the choice of implementing several features to enable debugging and performance analysis. However, putting more features would involve implementing complex logic on the chip. This involves a large amount of time and effort and increased costs. More importantly, however, there is a trade off involved between more features and increased capability for performance analysis. This is so because real time performance analysis involves gathering and processing of data at least as fast as the program being analyzed executes so that no data is missed. Since there are always limitations on the amount of data that can be stored and processed in a certain interval of time, one can either have large number of features but a few of which can be used at a time due to the limitations of chip area or one can implement a relatively small number of features, all of which can be used and which can be used much more effectively. In designing chips, chip area is always a precious resource and it is always beneficial to maximize the usage of all the logic. Therefore, the latter approach seems preferable. Another advantage offered by the latter approach to design is that one does not have to implement complex logic since the number of functions that the hardware is required to perform, is limited. Therefore, the latter approach to design was chosen i.e. implementing a relatively small number of features but try to maximize their capabilities and usage. All features to help debugging of code were, therefore, excluded and focus was on performance analysis.

Many of the debugging features can be more conveniently handled through other means. Good static analyzers can uncover several errors from the source text of the program. Such tools are typically available on large operating systems. Since real time software development is often done in host-target environments, static analyzers available on the host can be used to eliminate some errors from the programs. Source level debuggers are also increasingly available on large systems. So the programmer already has powerful tool to facilitate debugging on the host. The debugging features useful for real time environment such as monitoring memory locations for changes in values, gathering data after occurrence of a particular event etc. can be provided by a state analyzer.

Therefore, the merit of this approach to testing is that the task of testing is thus distributed to different tools. Each tool is dedicated to a particular task and thus its resources can be entirely devoted to that task. One can build a powerful testing system by combining such tools. Some part of the system helps debugging and other part does performance analysis. In this manner, maximum utilization of all resources of the system can be achieved and it is also more economical and efficient to implement the system in this manner.

The chip designed, therefore, only offers the capability to do performance analysis. But since its range of features is now delimited, one can devote the freed resources to provide additional capabilities. For instance, this chip was designed to run at a clock frequency of 100 MHz; fast enough for the current generation, high speed RISC microprocessors. It maintains a 48 bit counter for measuring the time spent for each range and a 32 bit counter for measuring the number of entries into the range. At the clock speed of 100 MHz (cycle time of 10 ns), this means that data can be collected for execution time of approximately 78 hours for each range. Thus, data can be collected for long, uninterrupted runs of programs. This is a very desirable performance analysis feature which is absent from the other tools discussed previously. This benefit is, of course, obtained at the cost of eliminating other features but considering the fact that a low cost tool such as this, in conjunction with a traditional tool such as a state analyzer, can provide a powerful software testing tool, it is a good tradeoff.

#### 3.2 Discussion of possible architectures

As discussed previously, the feature required of the chip was the ability to time sections of a code for extended periods of time. There are at least two significantly different architectures which can accomplish the same objective. In the following, the pros and cons of both and why one was chosen over the other, are discussed.

The first approach to architecture is the event triggered approach taken by *SoftAnalyst*.<sup>18</sup> In this approach, some particular function of the tool is triggered when the tool detects the occurrence of a predefined event such as, for instance, entering or exiting a procedure. The tool starts collecting data when the event is detected and stops collecting data when another event is detected. For instance, in *SoftAnalyst*, the user can specify up to 256 events. The tool maintains an on-chip timer and a status qualifier. When it detects the occurrence of any one of the defined events, it saves some tags from the status qualifier, the time of detection and the event number in a FIFO (first-in-first-out memory). The data in the FIFO is then compressed by a data compression chip which, in turn, feeds another microprocessor which analyzes the data.

There are some advantages to this approach. Firstly, since event detection is just a question of ANDing the data bits with a set of latches, this function is easy to implement and also takes very little of chip space.<sup>†</sup> Secondly, the interpretation of the events is not restricted by the hardware and is up to software. In *SoftAnalyst*, for instance, the same event recognizers are used to perform several functions such as tracing values of variables, recognizing entry to or exit from a procedure etc.

There are, however, disadvantages with this approach. The most serious problem with it is the storing and processing of data. The data is typically stored into a buffer (the FIFO in *SoftAnalyst*) which is emptied at regular intervals. The data must be processed fast enough so that the buffer does not overflow. This bottleneck is very difficult to overcome particularly with today's high speed microprocessors. The data would be, typically, written into memory which is generally a RAM. It is

It should be noted that *SoftAnalyst* is not implemented on a single chip but by using several other chips. This, however, is irrelevant from the viewpoint of architecture. The same architecture could, in theory, be implemented on a chip.

difficult to design RAMS which could be read and written at fast rates. The speed requirement of this project was 100 MHz. This would mean a 10 ns read/write accessible on-chip RAM, clearly a very difficult task. The problem, however, does not end here. Even supposing that a 10 ns RAM could be designed, one is still left with the requirement that post processing must be done at the rate of 10 ns. Taking the example of maintaining a count of time spent in a procedure, if the count was to be 32 bits long, this would mean doing a 32 bit addition in 10 ns in the worst case. There are ways to design around this problem but the logic becomes quite complicated.

Another small disadvantage with this approach is that it is very difficult to time procedures with multiple entries and exits. It is also difficult to account for interrupts. The timer needs to be stopped when executing interrupts. This requires frontend circuitry to detect interrupts. If the target system is a time sharing system, it is not possible to have a count of the timing unless some signal to stop the timer can be provided. In systems where such a signal is not available, this architecture is not useful.

Finally, there is the disadvantage of limited size of the buffer. Since the buffer is limited in size, it is not possible to time programs which run for extended periods of time. The buffer of *SoftAnalyst* for instance, fills up if the time of execution is of the order of seconds. This architecture is, thus not well-suited for the requirements of the project.

An alternate approach to the problem of timing the code is to count the number of memory addresses on the system bus which lie in a particular range. Programs are arranged sequentially in memory with instructions and data interspersed. The microprocessor puts out either instruction fetches or data fetches on the system bus during its execution. If one could detect and store the instruction fetch addresses, compare them with preprogrammed limits and detect if they are in or out of that range, one could maintain a count of the number of addresses detected in a range.

The count is approximately proportional to the time spent in the range and thus performance analysis data is obtained.

The disadvantage of this approach is that the count obtained is not accurate. But it is possible to overcome this limitation if additional signals from the system are available. One can continue counting between two successive instruction fetches assuming that the microprocessor is either executing the instruction or issuing data fetches. With such an arrangement, accurate timing information can be provided. Of course, this assumes the capability to stop the counting by an appropriate signals when needed. But when such a signal is not available, the tool can still provide a fairly accurate, though not exact, indication of where the program spends most of its time during execution. Another disadvantage of this approach is that range comparators are needed at the input to compare the input address with preprogrammed limits. In contrast to a simple ANDing of bits, significant amount of logic is now required to accomplish this function. This demands more chip area.

The most important advantage of this approach, however, is that it needs very little post processing of data and it does not need to store large amounts of data in memory. Only a count of the addresses being in or out of a range need be maintained which is not very difficult to accomplish in hardware. Since there is no buffer, the problem of having too much incoming data is completely eliminated. All that needs to be done is to maintain a counter for each range which is incremented when an address is in the range. This architecture is well suited for a chip since it is relatively simple to implement. It does not require fast on chip buffers and complicated logic to process the data in the buffer. Since this architecture appears much more appropriate for the requirements of the project, it was chosen for the chip in preference to the approach taken by *SoftAnalyst*.

The capability to do performance analysis at the source level is easily provided if the symbol table generated by the compiler is available. From the symbol table, appropriate software can obtain the entry and exit points of all the procedures and program the upper and lower limits of the range recognizers for the areas of codes which the user wants to time. If the number of ranges available does not cover all the procedures of a program, one can set up the chip so that it divides the address space of the program evenly among the available range recognizers. After one run of the program, the area of code where maximum time is spent can be narrowed down and then in the second run of the program, the chip can be set up to time various parts of that section of the code.

#### **3.3** Description of macroarchitecture of the chip

The chip consists of several range recognizers (sixteen in the version implemented for this project), each of which contains the following.

- 1. Two 32 bit latches which hold and lower and upper limit addresses for comparison (ul[0:31] for upper limit and ll[0:31] for lower limit). The recognizer increments its counter when the incoming address is greater than or equal to the lower limit and less than or equal to the upper limit. The data at the input pins is assumed to be 32 bits. The input data is used to write into the latches when the prg\_chip signal is raised. The data is written into the lower limit latch if the limit signal is low and it is written into the upper limit latch if the limit signal is high. A 4 bit range recognizer number must also be input along with the data for the lower and upper limits.

- A 48 bit counter which is incremented whenever the range recognizer detects an address that lies between the two limits and the active bit of the range recognizer is set.

- 3. An active bit which is set when the range recognizer detects a valid address within the programmed range. The bit is reset when the range

recognizer detects a valid input address which is outside the programmed range.

4. A 32 bit entry/exit counter which is used to count the number of times a range was entered. The counter is incremented when a valid input address is outside the programmed range and when the active bit was set in the previous cycle. That is, the count is incremented when the active bit changes from high to low. To provide for recursions, the entry/exit counter is also incremented when the active bit was set in the previous cycle and the input address is equal to the lower limit.

In addition, the chip has the following signals which are global.

- 5. The input clock. The maximum clock frequency is 100 MHz.

- 6. Input data (a [0:31]) to be used for comparison and counting by the range recognizers. The input data is latched in at the falling edge of the clock and can change at the clock frequency.

- 7. A valid bit for the chip indicating if the incoming data is valid or not. This bit can be used to maintain a count of particular types of addresses on the bus of the microprocessor; for example, instructions only or data only.

- 8. An en\_timer bit for the chip. When this bit is set and the chip is in the time\_a\_range mode (see the description of the chip\_mode bit below) and the active bit of the range recognizer is set, the address/time counter is incremented.

- 9. A chip\_mode bit for the chip. When this bit is set (high), the chip is in the time\_a\_range mode. In this mode, the counter of each range recognizer is incremented if the active bit of that range recognizer is set and the en\_timer bit is set. If the chip\_mode bit is reset (low), the chip is in the count\_addr mode. In this mode, the counter of each range

recognizer is incremented if the incoming data is valid (i.e. if the valid bit of the chip is set) and the incoming address lies between the upper and lower limits of the range recognizer.

- 10. Four input bits (d[0:3]) to indicate the range recognizer number. These bits are used to select a particular range recognizer when the upper and lower limits of a range recognizer are being programmed or when the address/time or the entry/exit count of a particular range recognizer is to be read out.

- 11. A strb signal to synchronize the writing of data into the range recognizer latches. After the signals d[0:3], limit, prg\_chip and a[0:31] are applied, they take some time to propagate to the range recognizer latches. The delays for each of these paths is unequal so it is necessary to synchronize them. The strb signal is used for this function. It is is applied when the signals have propagated through to their destinations. The write enable signal of the latch is raised when the strb signal is applied.

- The nr signal. This signal is the master reset for the chip. It resets all the counters to zero.

The entry/exit or the address/time count can be read out after the chip has finished collecting data for a single program run. The following signals are provided on the chip for this function.

- Eight bits (c[0:7]) which are used to output the value of address or entry/exit count of a range recognizers in pieces of eight bits i.e. in bytes.

- 14. Three bits (enr[0:2]) to select which byte of the counter is output. Valid values for the bits are 0 through 5 for the address/time count and 0 through 3 for the entry/exit count. The least significant byte of the counter (i.e. bits 0 through 7) is output when the value is 0.

- A ren (read enable) signal. The counters can be read only when this signal is set (high).

- 16. A clk4 signal. This signal outputs an internal clock of the chip which runs four times as slow as the input clock. Due to the internal structure of the chip, the signals to read the data of from the counters must be applied when the falling edge of this clock is detected. This signal is provided for the interfacing circuitry to allow it to properly synchronize the read signals that it applies to the chip.

- 17. An eccnt signal. When it is set (high), the value of the entry/exit counter is output and when it is reset (low), the value of the address/time counter is output.

- 17. Four bits (m[0:3]) which indicate the number of the range recognizer for which the data is to be read.

In addition to the above signals, the chip provides the following two additional signals used for testing the on-chip RAM.

- 18. The wen (write enable) signal. When this signal is high, the data input at the a [0:31] bits and the c[0:7] bits are used to write into the upper 40 bits of the address/time counter. (Note that the c[0:7] pins of the chip are bidirectional and are used as input pins when the wen signal is high). If the eccnt signal is low, the data is written into the upper 40 bits of the address counter and if the eccnt is high, the data (c[0:23]) is written into the upper 24 bits of the entry/exit counter. The lower 8 bits of both counters cannot be written into.

- 19. The strb2 signal, which is used to synchronize the writing of data into the on-chip RAM. This signal is applied when the wen signal and the data have propagated through their paths. This signal is needed because of the

unequal delays in these paths.

Appendix A contains a behavioral simulation of the chip written in the C language. The next chapter discussed the microarchitecture of the chip.

.

# 4. MICROARCHITECTURE OF THE CHIP

#### 4.1 Introduction

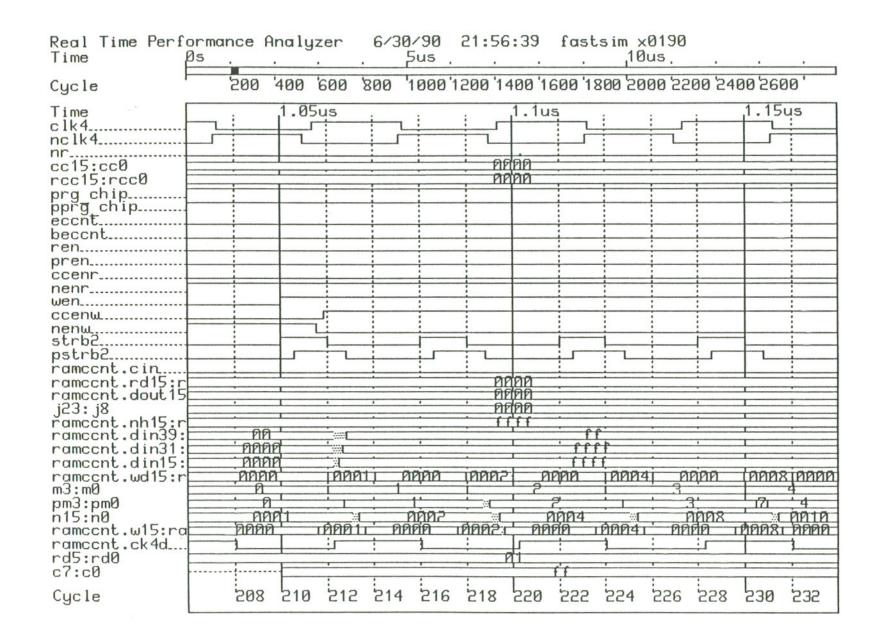

The microarchitecture of the chip is discussed in this chapter. First, the global architecture is discussed. This is followed by a description of the of blocks that make up the chip. Results from simulations are shown at the end of the chapter along with several plots of the relevant signals.

The software tools used for simulation and analysis are the tools used by the Advanced Development Group (ADG) at Tektronix Inc. The chip was designed using the ADG 1.5 µm standard cell library. The fastsim digital simulator was used for simulations, the fastplot plotting program was used to plot out the simulation results and the fastta timing analyzer was used to obtain critical path timing data. All the simulation data included in this thesis is in the form of plots. A description of each standard cell is included in Appendix B and the netlist is included in Appendix C.

The initial analysis of the chip was done using a value of 0.15 pF of wire capacitance for all the cells. This figure is used by the ADG group for most of their simulations. To account for the degradation of speed with temperature, a degradation of 0.3% per °C was assumed (as per ADG data). The chip was designed to work at 100 MHz at the junction temperature of 70°C. The timescale factor in the simulation control file is used for this purpose. All the timings of the cells were multiplied by this factor before being used by the simulator.

## 4.2 Global view of the microarchitecture

The chip may be broadly divided into the input section, the processing section and the output section. The processing section takes up most of the part of the chip and is the heart of it so it will be described first. The input and output sections are described later.

#### 4.2.1 The Processing Section

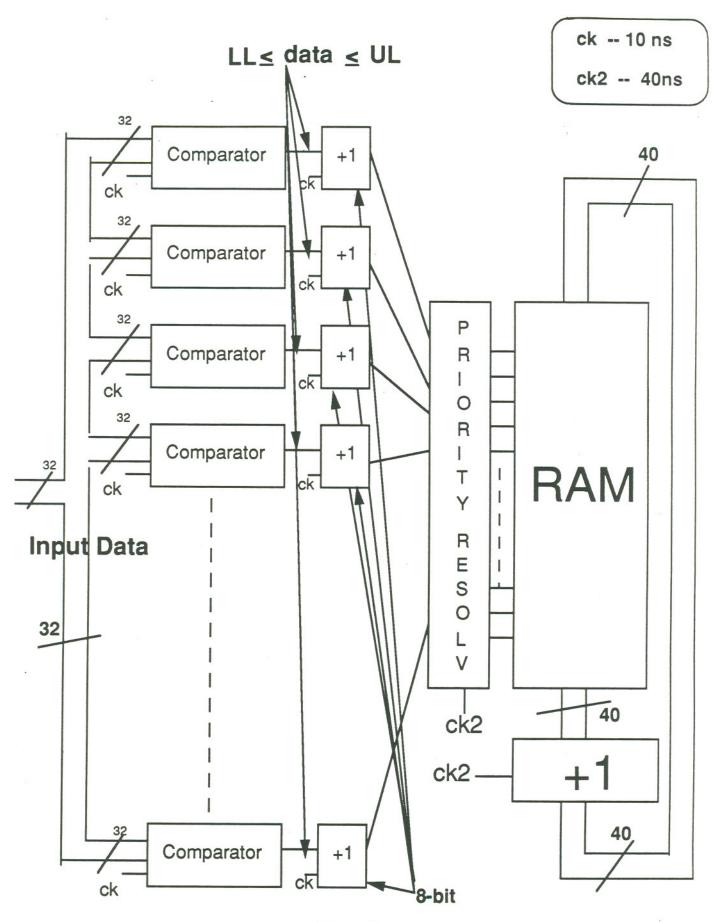

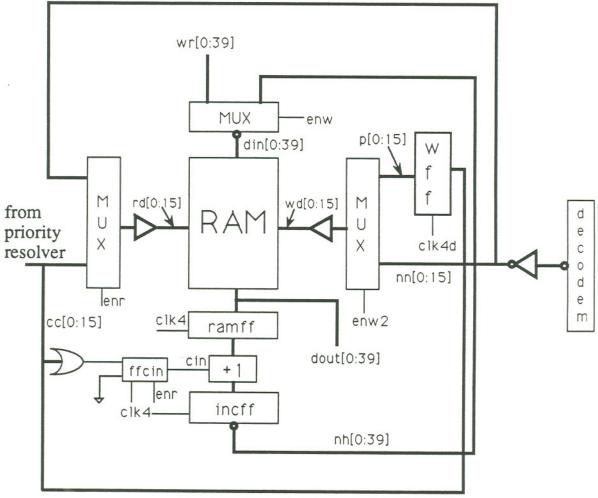

Figure 1 shows the architecture of the processing section of the chip. The chip consists of 16 comparators each having programmable 32 bit latches for upper and lower limits and a 32 bit input port for data. The output of the comparator is fed to two eight bit counters. One of the counters maintains the entry/exit count while the other maintains the time/address count. The output carry of each counter is fed to a priority resolver which feeds a large on chip RAM. The RAM maintains the upper 40 bits for the time/address count of each range recognizer. An identical arrangement is used for the entry/exit count except that the RAM for this is only 24 bits wide (i.e. a 32 bit count is maintained for the entry/exit count as opposed to the 48 bit count for the time/address count).

Since the chip runs at 100 MHz, it must be able to accept an address for counting every 10 ns. It is impossible to do a 32 bit compare in 10 ns with the standard cell library available. My solution was to use pipelined comparators. The details of this arrangements are discussed later. For the following discussion, it is assumed that the comparators provide an increment signal for each of the counters every cycle i.e. every 10 ns. The problem, thus, is to accomplish a 48 bit increment in 10 ns. This is discussed below.

Three different kinds of architectures are possible to solve the problem. Either separate counters and incrementers for each range recognizer could be provided or a

Figure 1

fast single incrementer for the all or some of the range recognizers which is fast enough to do the increments for several range recognizers, can be provided or a combination of the two approaches can also be used. The merits and drawbacks of these arrangements are discussed in the following.

In the first approach, a separate counter is provide for each range recognizer. To accomplish a 48 bit increment at the rate of 10 ns, the incrementer has to be pipelined i.e. the output carry of each stage of computation is used as the input carry for the next stage and the counter can accept requests for incrementing from the comparators each cycle. Such an arrangement, however, has some disadvantages. The counter would be implemented using flip-flops for each bit. Flip-flops occupy large chip area. If a separate counter for each is provided, a significant area of the chip is taken up by the counters and thus the number of range recognizers that can be provided, is reduced. Since one of the goals of the design was to try to squeeze as many range recognizers on the chip as possible, this approach was rejected since it violated the goals of the design.

In the second approach, only one or more high speed incrementers are used for all the range recognizers and the count is stored in an on-chip RAM. The advantage of this approach is that an on-chip RAM occupies very little space as compared to a flip-flop. Another advantage is that, since in most cases, only a few of the range recognizers will be active and counting, only a few incrementers are needed for all the range recognizers (as opposed to one for each as in the previous approach). However, there are problems with this approach.

The access time for reading and writing for RAMs is typically large. For instance, the C533 standard cell of the 1.5  $\mu$ m library (a 16 bit, single input output RAM) has an access time of 16.56 ns plus 2.34 ns for each pF of capacitance on its output. Clearly, this is unacceptable for the required speed of 10 ns. Even if a faster RAM could be designed to meet the design requirements, there is another problem

with this approach. It must be realized that in the worst case, a 48 bit increment is needed every 10 ns *for each range recognizer*. Keeping this in mind, consider the following sequence of events. Let the incrementer pipeline have 4 stages. Thus, it takes 40 ns to accomplish the 48 bit increment and write the incremented value back into memory. Let the initial count in the memory be 10. At time t = n, there is a request to increment the count and the count is read out and loaded into the incrementer. The incremented count will be available in the memory at n+40 ns. If, within this period, there is another request for an increment, the counter will read out the *old* count again i.e. 10 instead of the correct count which should be 11. So, the count will be incorrect. Since the range recognizers may provide a request for incrementing count every 10 ns, this approach is unacceptable.

In the third approach, a combination of the above two architectures is used to provide an optimal arrangement which captures the advantages of both. The problem with the RAM was that it received the increment requests too fast. If the requests can, somehow be slowed down, the RAM can be used. This can be done when it is realized that a counter is a divide by n circuit where n is the number of bits in the counter. The carry out at the n<sup>th</sup> bit occurs 2<sup>n</sup> times as slow as the carry input to the counter. So, if we have a 4 bit counter, the carry out at the 4th bit can occur at the maximum rate of 160 ns if the rate at which the input increment requests can occur is 10 ns. Now, the increment requests have slowed down sufficiently so that the second approach above can be implemented. In such an arrangement, each range recognizer will have its own n bit counter which stores the lower n bits of the 48 bit count. The carry out of this counter can be used to increment the upper (48-n) bits of the count which are stored in an on-chip RAM. The on-chip RAM can feed a single (48-n) bit incrementer which, after incrementing the data, writes it back to the RAM. This will be the only incrementer for all the range recognizers on the chip and thus significant chip area can be saved. The value of n must be chosen so that the correct timing and

optimization is achieved. This depends on the timings associated with the RAM, the number of range recognizers and whether overlapping ranges are allowed or not. The ADG standard cell library has a fast 4 bit incrementer (X137F) which, when used with a standard 4 bit flip-flop (X351W4), can read the data out of the flip-flop, increment it by one and store it back to the flip-flop within 10 ns. Assuming nonoverlapping ranges and a 4 bit counter for each range recognizer and a total of 16 range recognizers on the chip, if there was a single incrementer for all the range recognizers for the upper 44 bits (with the count being stored in the RAM), the RAM circuit (the priority resolver, the RAM and the incrementer etc. see figure 1.) would have to finish a 44 bit increment in 10 ns in the worst case. As discussed above, the access time for the ADG standard cell RAM itself is higher than 10 ns so this solution is unworkable. As is shown later, a 40 ns clock period for the RAM circuit is optimal. (A 20 ns clock period could be used but it was found that a lot of additional logic was required to accomplish this; for instance a pipelined incrementer was required and more parallelism in the priority resolver was also necessary. The write back circuit to the RAM also became quite complicated). If every range recognizer had a 6 bit counter, the RAM circuit will be able accomplish the job of doing a 44 bit increment for 16 range recognizers in the worst case. However, the range would still have to non-overlapping. Since a 4 bit incrementer standard cell was readily available and since using an 8 bit counter for each range recognizer with a 40 ns clock circuit would give us the added feature of overlapping ranges, an 8 bit counter (one each for address/time count and entry/exit count) for each range recognizer was implemented. The upper 40 bits are stored in the RAM.

#### 4.2.2 The Input Section

The input section consists of the following. (Please see Appendix C for the netlist).

- All the input signals are input to the C920 standard cell (a pad) whose output is the input for the C501 TTL to CMOS level shifter. The IPADT cell (which is actually a macro) on the netlist is a combination of the pad and the level shifter. The output signals from the level shifter is then used as the input signal for the various cells in the chip.

- 2. The input data, a [31:0], is fed to the pads whose outputs are fed to inverting TTL to CMOS level shifters (the IPADI macro which consists of the pad C920 and the buffer C507). The output of the level shifters (pa[31:0]) are fed to inverting buffers (cell S101X2). The output of the buffers (b[31:0]) are then fed to the range recognizers.

- 3. The clock buffer generates the clock signal which is routed to all the flip-flops in the chip. The input clock signal from the TTL to CMOS level shifter (pck) feeds four non-inverting buffer cells (Z101) connected in parallel. The output of these four cells (ck1) are wire-or'ed and then fed to 28 Z101 cells connected in parallel. The outputs of these cells are wire-or'ed to form the clock for the chip (clk) which is then routed to all the flip-flops in the chip.

- 4. Several flip-flops in the chip use an asynchronous reset signal. In order to synchronize the reset signal with the clock, the reset signal is fed to a 4 bit flip-flop such that the output of each bit is the input of the next bit. The final output is the reset signal (nr.3) properly synchronized with the clock which is then fed to a large non-inverting buffer (Z101X4) whose output (the bnr.3 signal) serves as the reset signal for the entire chip. The four bit flip-flop is used to avoid the flip-flop from becoming metastable and thus providing an erroneous reset signal.

- 5. The limit signal is fed to the pad and the level shifter. The output of the level shifter (plimit) is fed to a non-inverting and an inverting buffer. The outputs of the two buffers (the blimit and the bnlimit signals) are fed to

each of the range recognizers. The strb signal, which is used to synchronize the writing of data into the latches of the range recognizers is also routed to the range recognizers after being passed through two Z101X4 buffers. The prg\_chip signal, similarly, is fed to a pad whose output is fed to a level shifter. The output of the level shifter (pprg\_chip) then feeds other parts of the chip.

- 6. The four input bits, d[3:0] which select a particular range recognizer are, like the other signals, fed to a pad whose output feed a level shifter. The output of the level shifters (pd[3:0]) is fed to a decoder tree. The decoder tree uses the X417 standard cell which is a two input four output decoder with an enable signal. The upper 2 bits, pd[3:2] feed one decoder cell. The pprg\_chip signal is the enable signal for this decoder so that the decoder outputs are enabled only when prg\_chip is high. The outputs of the decoder (decode[0:3]) are fed to the enable inputs of four other decoder cells. The two inputs of the four decoder cells are the lower two bits, pd[1:0]. Each of the four decoders generate four outputs which are then fed to the range recognizer cells (signals prg lat[0:15] in the netlist).

- 7. Both the valid and the en\_timer signals, are fed to pads whose outputs are fed to level shifters. The outputs of the level shifters (pen\_timer and pvalid) are fed to the DLY4X delay cells. This is needed to equalize the delay between these signals and the b[31:0] signals i.e. the input data. The output of the delay cells (den\_timer and dvalid) is then stored in flipflops. The output of the flip-flops is fed to buffers which transmit the signals (bvalid and bnen\_timer) to the range recognizers (Note that the en\_timer signal is inverted before being distributed to the chip). The chip\_mode signal is also trapped in a flip-flop and then fed into an inverting and a non-inverting buffer. The outputs of these buffers (bchip mode and

bnchip mode) are routed to the range recognizers.

### 4.2.3 The Output Section

The output sections consists of the following. (Please see Appendix C for the netlist).

1. The ren (read enable), wen, eccnt and strb2 signals are fed to input pads which feed TTL to CMOS level shifters. The eccnt signal, as previously explained, is used to read either the time/address or the entry/exit count. The output of the level shifter for this signal (peccnt) is fed to two large non-inverting buffers (Z101X4 cells) and their output is routed to other parts of the chip (the beccnt signal). The eccnt signal is also fed to an inverter (X101 cell) whose output (neccnt signal) is used to generate the read signal for the address/time count. The output of the level shifter for the ren signal (the pren signal) is ANDed with the beccnt signal to generate the ecenr signal which is the read signal for the entry/exit count RAM. Similarly, the neccnt and the pren signals are ANDed to generate the ccenr signal which is the read signal for the time/address count.

The wen signal is the signal used to write into the RAMs. This signal is used only for testing the RAM. In the normal operation of the chip, all the locations of the RAM are initialized to zero. The wen signal is fed to the pads whose output is fed to the level shifter whose output is the pwen signal. The pwen signal is ANDed with the neccnt signal and the pprg\_chip signal to generate the write signal for the address/time count RAM. Similarly, a signal for the entry/exit count RAM is also generated. The strb2 signal is used to synchronize the writing of data into the RAM. This is explained later.

2. The enr[0:2] bits decide which byte of the count is to be read. They are, as usual, fed to input pads and level shifters whose outputs (penr[0:2]) are fed

to three inverters and to AND gates to decode the three bits into six separate signals (rd[0:5]). The signal which is high indicates the number of the byte of the count to be read.

- 3. Just like the input section, the output section also has a decoding tree which is used to generate signals for which range recognizer count is to be read. The signals m[0:3] are decoded into n[0:15] which, after being fed to inverting buffers, are fed to a mux which drives the read port (or a mux which drives the write port) of the appropriate RAM. A separate decoding tree is provided in the output circuit because of the delay associated with the signals reaching the read port of the RAM and the structure of the RAM circuit. If the decoding tree of the input section were used, the delays involved are unacceptable so a separate decoding tree was needed. This will be elaborated upon later.

- 4. The output of the entry/exit count and the time/address count RAMs and counters are fed to a large MUX tree. The first stage of the MUX tree multiplexes the output of the two RAMS (j[31:8] and k[31:8]). The beccnt signal is the control signal for these muxes. The outputs of these muxes (1[31:8]) and the output of the counters of the range recognizers are then fed into 6 to 1 muxes. These muxes are used to send a particular byte of the count to the output. The rd[5:0] signals are used as the control signals for the muxes.

- 5. The final output of the 6 to 1 muxes (1[7:0]) is then fed to bidirectional pads. The bidirectional pads consist of one incoming and one outgoing tristate buffers connected to the pad input. The pad can, thus be used for input when the incoming buffer is enabled and it can be used as an output pad when the outgoing buffer is enabled. The outgoing buffer is enabled by the nenr signal i.e. when the count is to be read out. The 1[7:0] signals are then output as c[7:0]. The incoming buffer is enabled by the nenw signal i.e. when data is to be writ-

ten into the RAM. The wr[32:39] bits are used to write to the upper 8 bits of the time/address count RAM. This is used only for testing the internal RAM. Lastly, the internally generated 40ns clock, clk4, is driven out to the pins so that it can be used as a synchronization signal for applying the enr[2:0] signals. The signals must be applied within 20ns after the falling edge of clk4 is detected or the output data will be incorrect.

The next few sections discuss the range recognizer circuit, the priority resolver, and the RAM circuit in detail.

### 4.3 The Range Recognizer Circuit

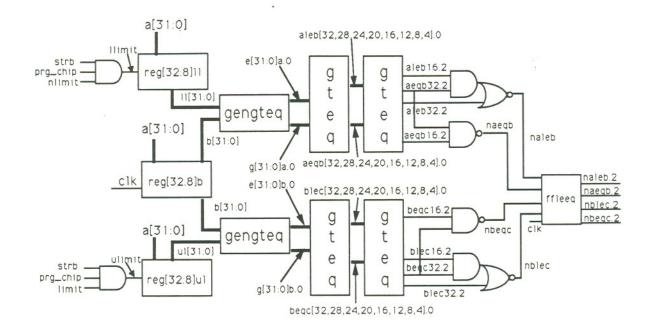

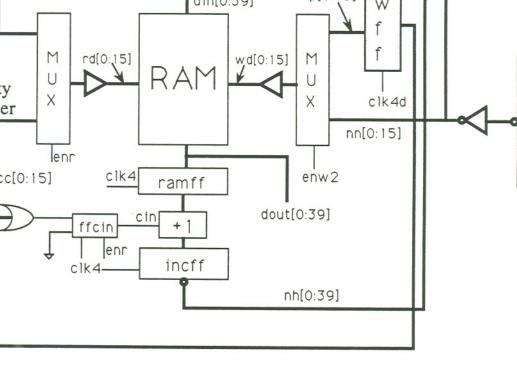

Figure 2 shows the components of the range recognizer in two parts. The netlist for the range recognizer is in Appendix C starting with the "model compare" statement. The range recognizer takes as its input the signals provided by the input section and outputs the carry bit for the two counters and the lower 8 bits for the counters.

The range recognizer uses several flip-flops with asynchronous resets. The master reset signal is first fed to a local buffer of the range recognizer and the output of the buffer is fed to the reset inputs of the various flipflops. As shown in the figure, the input data, a [31:0] is fed to two latches and a flipflop. The lower limit latch holds the 32 bits of the lower limit address, ll[31:0] and the upper limit latch holds the 32 bits for the upper limit address, ul[31:0]. The write enable signal for the lower limit latch is generated by ANDing the prg\_lat, the nlimit and the strb signals. The prg\_lat signal is connected to the output of the decoder tree of the input section and the other two signals are connected to their counterparts from the input section. Thus, the latches would be written into when the prg\_chip signal is high, the range recognizer is chosen by the decoding tree, the

Figure 2

proper latch is chosen by the limit signal and the strb signal is raised. The delay for the prg\_lat, limit and the a(31:0] are unequal so the strb signal is necessary to provide the right synchronization. The incoming data is also stored in the input four bit flipflops reg[31:4]b.

The range recognizer logic is designed to do a 32 bit compare. The input address, a [31:0] is compared with the lower and upper limit addresses and a signal for whether the input address is less than or equal to upper limit and greater than or equal to lower limit, is generated. Since a comparison must be done every 10 ns, the comparator is pipelined. The logic equation for comparison can be derived as follows. Given two numbers A and B, each n bits long, we generate two signals,  $e_i$  and  $g_i$  for each bit of both the numbers such that,

$$e_i = a_i b_i + \overline{a_i} \overline{b_i}$$

$$g_i = \overline{a_i} b_i$$

The  $e_i$  signal is true when the two bits,  $a_i$  and  $b_i$  are equal and the  $g_i$  signal is true when  $b_i$  is greater than  $a_i$ . To compare the numbers A and B, we start comparing from the highest bit. If the highest bit of B is greater than A, then we have the result immediately or if they are equal, we must compare the next lower bit. So, if the numbers are four bits long, the equation for A < B is,

$$A < B = g_3 + e_3g_2 + e_3e_2g_1 + e_3e_2e_1g_0 \tag{1}$$

This can be rewritten as

$$A < B = g_3 + e_3g_2 + e_3e_2(g_1 + e_1g_0)$$

Now, if we define

$$aleb_3 = g_3 + e_3g_2 \qquad aeqb_3 = e_3e_2$$

and

$$aleb_1 = g_1 + e_1 g_0$$

then

## $A < B = aleb_3 + aeqb_3 \cdot aleb_1$

Note that this is the same equation as the equation for A < B if A and B were 2 bits long, with  $e_1$ ,  $g_1$  and  $g_0$  replaced by  $aeqb_3$ ,  $aleb_3$  and  $aleb_1$  respectively. Thus, a 4 bit compare can be accomplished in two stages: in the first stage generate the e and g signals and use them to generate the *aleb* and *aeqb* signals which are the 2 bit equivalents of the 1 bit e and g signals. Then use the *aleb* and *aeqb* signals to generate the final signals for A<B in the second stage. This method can be extended to 32 bits and this is the method followed in the logic of the range recognizer.

As shown in figure 2, the input address and the lower and upper limits are fed to the gengteq blocks. These blocks generate the e and g signals for each bit. The gsignal is generated by feeding the corresponding bits to an XNOR gate (X421) and the e signal is generated by feeding the complements of the corresponding bits to a NOR gate (X102). The e and g signals from the gengteq blocks are then fed to the gteq block. This block consists of several gtgen cells which do a four bit compare with the corresponding e and g inputs (see equation (1) above). The output of these cells are the *aleb* signals. In addition, the e signals are fed to a four input AND gate (X404) whose output is the *aeqb* signal. The various *aleb* and *aeqb* signals are trapped in flip-flops. This is, thus, the first stage of the pipeline for comparison of the input address and the addresses in the latches. The output of the first stage is then fed to another gteq block which generates four signals, aleb16.2, aeqb16.2, aleb32.2, aeqb32.2 as its output (similar signals are generated for the comparator for the input address and upper limit latch). The equation for A < B when A and B are 32 bits long, thus, is,

$A < B = aleb 32.2 + (aeqb 32.2) \cdot (aleb 16.2)$

The *naleb* signals is the  $\overline{A < B}$  signal and the *naeqb* is the  $\overline{A = B}$  signal. Similarly, the *blec* and *beqc* signals are generated from the comparator comparing the upper limit address and the input address. These signals are trapped in a flip-flop. This

completes the second and final stage of the pipeline for the comparison.

The bottom part of figure 2 shows the logic which uses the signals provided by the comparators to generate the entry/exit and the time/address count. The inrange signal is true if the input address lies between the upper and the lower limit i.e. if  $ll[31:0] \le a[31:0] \le ul[31:0]$ . The logic equation for this is,

$inrange = (aleb + aeqb) \cdot (blec + beqc)$

Using DeMorgan's law, this can be rewritten as

$$inrange = \overline{aleb} \cdot \overline{aeqb} + \overline{blec} \cdot \overline{beqc}$$

(In the circuit, the complement outputs of the ffleq flipflops are used to generate the inrange signal. Figure 2 shows these signals.) Along with the inrange signal, the active signal for each range is also generated. Recall that the active signal indicates if the current range is active and counting or not. The active signal must be updated every cycle. The active signal should be true if the input address is valid and in the range or if the current input address is invalid and current range was active in the last cycle. The logic equation for the *active* signal at time *t* thus becomes,

# $active_t = active_{t-1} \cdot valid + valid \cdot inrange$

The *active*<sub>t-1</sub> signal is the *active.3* signal on the diagram, the *active*<sub>t</sub> is the *active* signal the *valid* signal and its complement are *valid.2* and *nvalid.2* respectively. The signal for whether the current input address signifies an exit from the range, *exitrange*, is true when the current input address is valid and not in the range and the range recognizer was active in the last cycle. In addition, to account for recursive procedures, the *exitrange* signal is asserted when the input address is valid and is equal to the lower limit and the range recognizer was active in the previous cycle. Thus the logic equation for the *exitrange* signal is,

$exitrange = valid \cdot active_{n-1} \cdot (\overline{inrange} + aeqb)$

Using DeMorgan's law,

$$exitrange = valid \cdot active_{n-1} \cdot (inrange \cdot aeqb)$$

The  $\overline{aeqb}$  is the naeqb.2 signal in the figure. The exitrange signal is used to increment the entry/exit counter.

The increment signal for the address/time counter is the inc signal in the figure. As mentioned previously, the count is incremented when either of the following conditions are met: the chip is in count-address mode and the input address is valid and in the range or the chip is in time-a-range mode, the en\_timer signal is high and the range is active and counting. As shown in the figure, a part of the increment signal is generated in parallel with the active signal. The logic equation for the inc signal is,

$inc = valid \cdot \overline{chip\_mode} + en\_timer \cdot chip\_mode$ Using DeMorgan's law,

$$inc = (valid + chip_mode)(en_timer + chip_mode)$$

This is shown in the figure. The inc signal is trapped in the ffmisc flip-flop. Various other signals are also trapped in the flip-flop as shown in the figure. It should also be noted that this flip-flop has a reset signal, bnr. At initialization time, this signal is asserted and all the bits of th flip-flop are set to zero when the signal is asserted. The complements of the inc.3 and active.3 signals from the flip-flop are fed to a NOR gate whose output is fed to an eight bit incrementer. Similarly, the exitrange.3 signal is the increment signal which is fed to an identical eight bit incrementer.

The eight bit incrementer consists of two four bit flip-flops and two four bit incrementers. A single four bit increment is done in each cycle i.e. each 10 ns. The output of the flipflop feeds the incrementer whose output is fed back to the flip-flop inputs. The carry-out from the lower 4 bits is trapped in a flip-flop and then fed to

the next stage. The output carry of each incrementer is fed to the priority resolver logic (discussed later). The output bits of the flip-flops are fed to 2 to 1 inverting muxes whose control signal is the eccnt signal. These muxes controls which count is sent to the pins when the count is to be read out. The output of the muxes feed a tristate buffer which is enabled when the read signal for this particular range recognizer is asserted. The tristate buffer feeds an eight bit bus which is common to all the 16 range recognizers on the chip. The appropriate buffer drives the bus when it is enabled. The tristate buffers reduce the number of wires and thus minimize wiring capacitances.

Thus, in summary, the range recognizer blocks take a 32 bit address as input and output two eight bit counts and two carryout signals, cntcout8 and exitcout8. The next section discusses the priority resolver circuit.

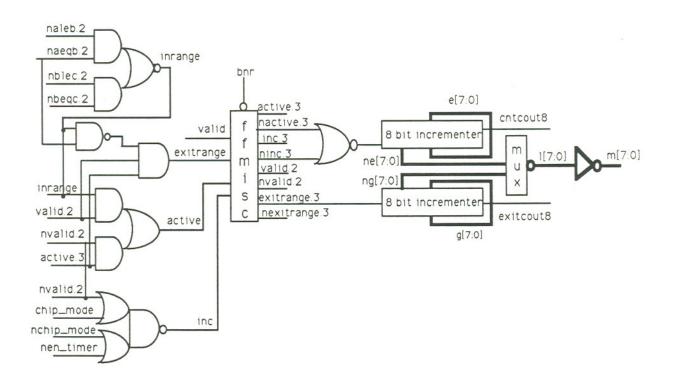

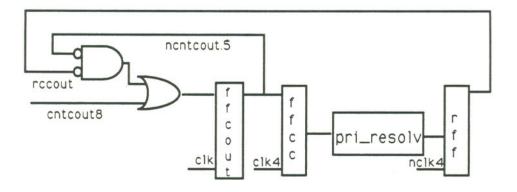

### 4.4 The Priority Resolver Circuit

As explained previously, the specifications of the chip allow overlapping ranges to be programmed. Thus more than one range recognizer may output a carry at the same time. The output carry is a signal for the RAM circuit to increment the upper bits of the count for the range recognizer. Since there is only one incrementer in the RAM circuit, only one of the increment requests can be handled at a time by the RAM circuit. Thus some mechanism to ensure that the requests are queued up and sent one after the other to the RAM circuit, is required. The priority resolver circuit performs this function. The RAM circuit takes 40 ns to complete one increment. The priority resolver takes as its input, the carry out signals from the range recognizer and stores them till the RAM circuit is free to do an increment. When the RAM circuit proceeds with the increment for a particular range recognizer, the priority resolver clears the corresponding carry out bit from its own flip-flops. This bit can be set again by another carry out signal from the respective range recognizer. Since the carryout from each range recognizer can only occur at the rate of once in 256 cycles (2560 ns), and since there are only 16 range recognizers on the chip, with the RAM circuit cycle time of 40 ns, the priority resolver will always take care of all the increment signals correctly and never miss any of them even in the worst case of all the 16 range recognizers giving an increment signal at the same time.